Prozessorkarte zur Verarbeitung rechenintensiver Echtzeit-Modelle

FPGA entlastet Hauptprozessor von I/O-Verarbeitung

Steuergerätetests mit realen Fahrzeugen sind aufwendig und werden daher zunehmend durch Labortests mit Hardware- in-the-Loop-Simulation (HIL) ersetzt. Auch die Verarbeitung von I/O-Signalen erzeugt durch Interrupts, Transfer von Daten in den Speicher usw. eine hohe Belastung des Prozessors. dSPACE nutzt das Hypertransport-Protokoll, um einen FPGA-I/O-Prozessor an einen AMD-Opteron anzubinden, damit sowohl I/O als auch Simulationsmodell in Echtzeit berechnet werden.

Steuergerätetests mit realen Fahrzeugen sind aufwendig und werden daher zunehmend durch Labortests mit Hardware- in-the-Loop-Simulation (HIL) ersetzt. Auch die Verarbeitung von I/O-Signalen erzeugt durch Interrupts, Transfer von Daten in den Speicher usw. eine hohe Belastung des Prozessors. dSPACE nutzt das Hypertransport-Protokoll, um einen FPGA-I/O-Prozessor an einen AMD-Opteron anzubinden, damit sowohl I/O als auch Simulationsmodell in Echtzeit berechnet werden.

Jobangebote+ passend zum Thema

INHALT: |

Die HIL-Simulation mit komplexen, detailgenauen Simulationsmodellen erfordert eine äußerst hohe Rechenleistung. Deshalb hat dSPACE seine echtzeitfähige Hardware erneut beschleunigt und die Prozessorkarte DS1006 entwickelt. Als zentrale Elemente enthält das Board einen AMD-Opteron-Prozessor sowie ein FPGA aus der Stratix-Familie von Altera. Es ermöglicht einen äußerst schnellen Zugriff auf I/O-Hardware mit minimalen Latenzzeiten.

Bei der Entwicklung von Hochleistungs- CPU-Plattformen kommen überwiegend Bauteile zum Einsatz, die für Server und PCs entwickelt wurden und aufgrund hoher Stückzahlen zu erschwinglichen Preisen angeboten werden. Auch bei den zugehörigen Chipsätzen und Schnittstellen greifen die Entwickler meist auf Bauteile für den Server- und PC-Markt zurück. In beiden Anwendungsbereichen steht neben der reinen Rechenleistung der Datendurchsatz im Vordergrund.

Die Anforderungen an echtzeitfähige Systeme gehen jedoch in eine andere Richtung. Hier sind kurze Latenzzeiten und zeitnahe, jitterfreie Einzelzugriffe auf die I/O-Komponenten unabdingbar. Mit modularen Echtzeit- Systemen für Rapid Control Prototyping und HILSimulation bedient dSPACE einen Markt, in dem Rechenleistung und Echtzeit-Fähigkeit gleichermaßen wichtig sind. Hier müssen sowohl Modelle mit komplexen Differentialgleichungen, zum Beispiel zur Simulation kompletter Kraftfahrzeuge, berechnet oder echtzeitfähige I/Os bedient werden.

Stets die schnellsten Prozessoren

Während sich für die I/O-Kommunikation ein von dSPACE entwickelter High-speed-I/O-Bus über viele Jahre bewährt hat und die heutigen Echtzeit- Anforderungen abdeckt, haben sich im Bereich der Rechnertechnologie mehrere Architekturwechsel vollzogen. Während man zunächst Prozessoren mit höchster Rechenleistung aus dem Bereich der digitalen Signalprozessoren (DSPs) einsetzte, entschied man sich später für RISC-Prozessoren wie zum Beispiel Alpha und PowerPC. Aufgrund des großen Marktpotentials und entsprechender Bemühungen der Hersteller haben letztendlich x86-Prozessoren die Leistungsspitze erreicht. Die Roadmaps der Hersteller zeigen, dass sich diese Entwicklung auch in den nächsten Jahren fortsetzen wird. Um seinen Kunden die maximale Rechenleistung bieten zu können, ist dSPACE diesen Trends stets gefolgt und hat sich bei den Hochleistungs- Prozessorsystemen für HIL-Anwendungen zum Umstieg von der Power- PC-Technologie auf x86-Prozessoren entschieden.

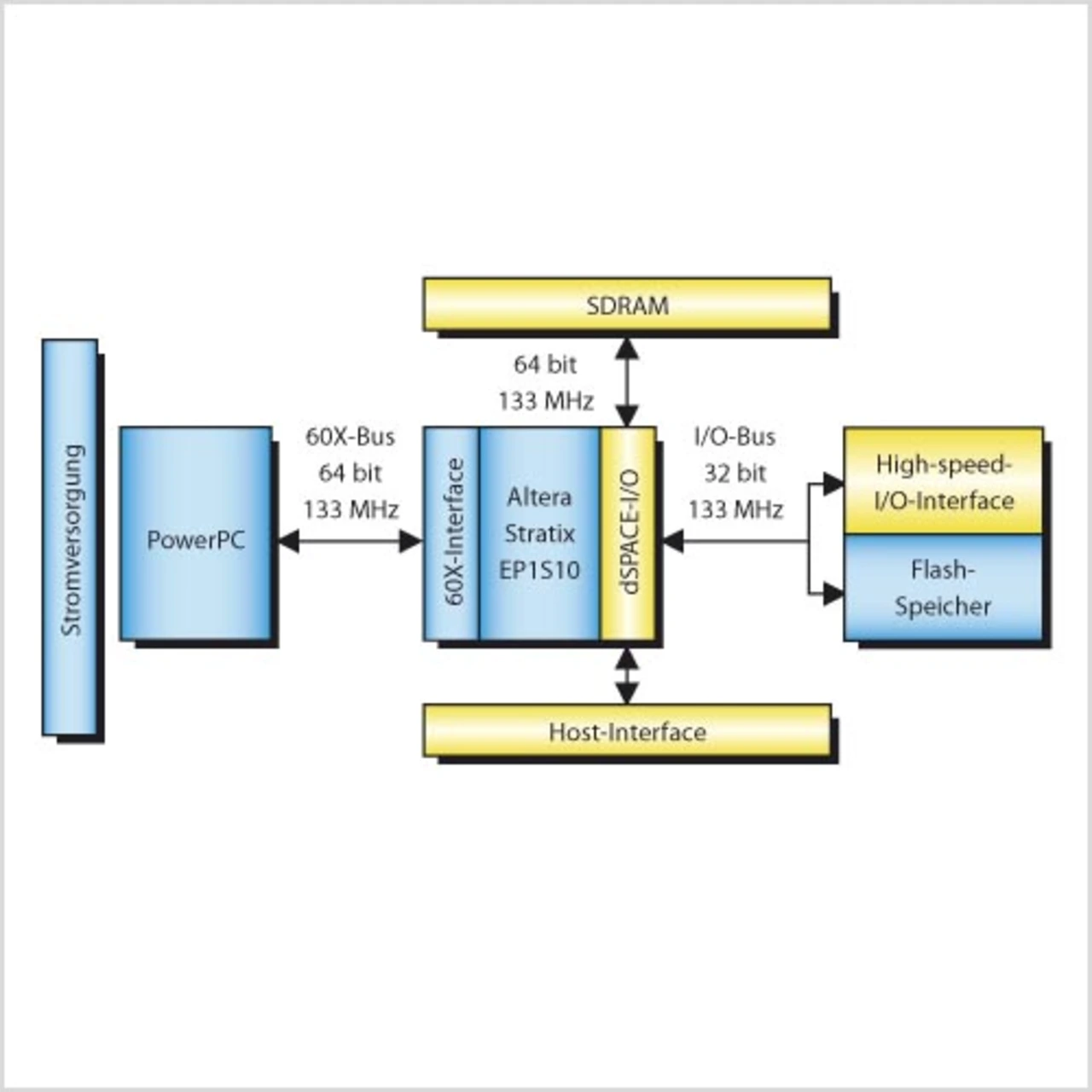

Wie bei den bisherigen Technologiewechseln bestand ein wesentliches Ziel darin, den bewährten High-speed- I/O-Bus beizubehalten, um die Vielzahl existierender I/O-Boards mit schnellen analogen und digitalen Einund Ausgängen sowie alle gängige Bussysteme wie FlexRay, CAN, LIN, RS 232, RS 422/RS 485 und MIL-STD weiterhin zu unterstützen. Diese Vorgehensweise sichert die Investitionen der Kunden, die ihre I/O-Karten mit dem neuen Prozessorsystem unverändert weiter verwenden können. Bild 1 zeigt die Systemtopologie des bisherigen Prozessorsystems DS1005 auf der Basis eines PowerPC-Prozessors.

In der Konzeptphase zur Entwicklung des neuen Prozessorsystems wurden verschiedene Untersuchungen hinsichtlich der zu erwartenden Latenzzeit für I/O-Zugriffe durchgeführt. Bei dieser Betrachtung wurden der PCI-Bus, der PCI-X-Bus, das DDR-SDRAM-Interface und der Frontside-Bus des Pentium 4 als mögliche Lösung zur Anbindung des x86-Prozessors an den I/O-Bus betrachtet. Dabei wurden folgende Erkenntnisse gewonnen.

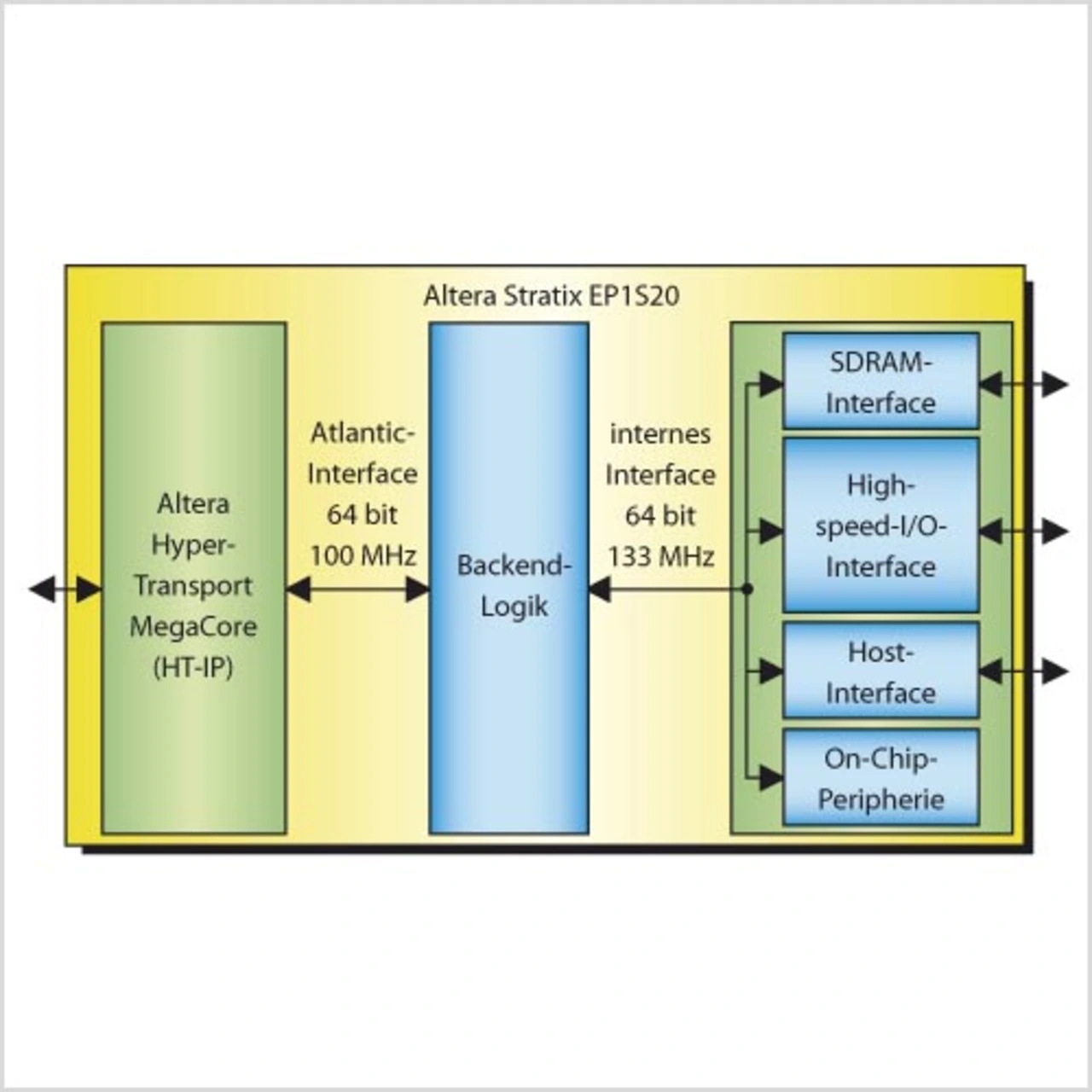

Das Stratix-FPGA bildet auf dem Prozessorboard DS1006, bei dem das Schaltungsdesign des High-speed-I/OBusses vom bestehenden Board DS1005 übernommen wurde, genau wie beim DS1005 das zentrale Element. Es verbindet den AMD-Opteron- Prozessor mit der gesamten dSPACEI/ O-Karte. Der AMD-Opteron-Prozessor wurde über den Hypertransport- Bus des Prozessors direkt an das Stratix- FPGA angeschlossen. In diesem FPGA arbeitet der Altera Hypertransport Megacore, der über Alteras Atlantic- Interface die vom Prozessor kommenden Write- und Read-Request-Pakete an die Backend-Logik weiterleitet. Sie setzt die empfangenen Hypertransport- Pakete auf das parallele Interface der FPGA-internen I/O-Komponenten um. Bild 3 zeigt die Komponenten im Stratix-FPGA. Die grün hinterlegten Blöcke sind die bestehenden Komponenten, die in das Design integriert wurden. Ausschließlich die Backend-Logik, die das Interface zwischen dem Megacore und der dSPACE- I/O bildet, musste komplett neu implementiert werden. Aufgrund des Einsatzes bestehender und bereits getesteter Komponenten konnten hier die Entwicklungszeit und das Designrisiko deutlich reduziert werden.

Ein High-end-Server-Prozessor stellt normalerweise sehr hohe Anforderungen an Kriterien wie Spannungsversorgung, Leiterplatten-Routing, thermisches Design und Signal- bzw. Power-Integrität. Die Entwicklung des Prozessorkerns für das Board DS1006 (in Bild 2 grün hinterlegt) war daher eine große Herausforderung. dSPACE begab sich mit dem Einsatz der x86- Technologie auf Neuland. Um das Designrisiko zu minimieren, arbeitete man deshalb eng mit dem AMD-Design- Center in Boston zusammen, das die gesamte Entwicklung des Prozessorkerns für das Board begleitete.

Zusätzlich zu den ausführlichen Entwurfsrichtlinien hat AMD einen schnellen technischen Support für dSPACE bereitgestellt. Die AMD-Ingenieure prüften Berechnungen und Simulationen und führten Schaltplanbzw. Routing-Überprüfungen durch. Als Resultat dieser engen und guten Zusammenarbeit funktionierte der erste Prototyp des Boards auf Anhieb. Weiterhin fand im Rahmen dieses Projektes ein Know-how-Transfer statt, durch den dSPACE sein Wissen im Bereich der Entwicklung von x86-Prozessordesigns stark erweitern konnte.

- FPGA entlastet Hauptprozessor von I/O-Verarbeitung

- Trotz schnelllebigem PC-Markt: Vermeidung häufiger Redesigns

- Lösungen aus Standard-PCs für Echtzeit-Systeme nicht optimal