Ein 8-bit-Softcore-Prozessor für programmierbare Logik

Fortsetzung des Artikels von Teil 2

Ein 8-bit-Softcore-Prozessor für programmierbare Logik

Die Ein-/Ausgabe-Schnittstelle des PicoBlaze ist recht einfach und flexibel aufgebaut. Sie besteht aus einem 8-bit-Eingangsport und zwei 8-bit-Ausgangsports. Die Ein-/Ausgabeports sind über Multiplexer mit dem Registersatz des Prozessors verbunden. Zusätzlich sieht diese Schnittstelle zwei Steuersignale vor: Read-Strobe und Write-Strobe. Beide Signale werden in der Steuerlogik während der Ausführung der Ein-/Ausgabebefehle aktiviert.

Jobangebote+ passend zum Thema

Assemblerbefehle und Befehlsformate

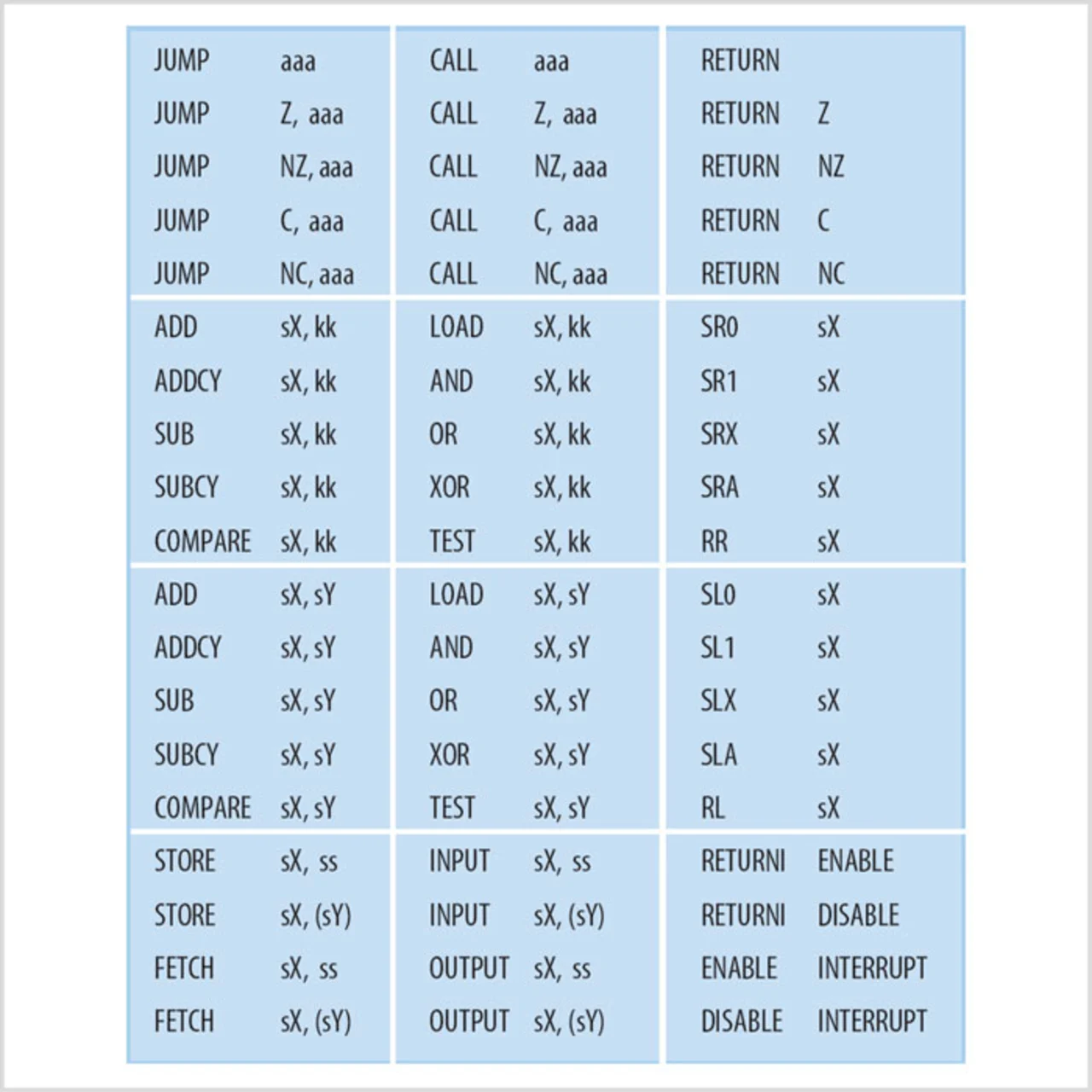

Wie bereits erwähnt, verfügt der Pico-Blaze über einen reduzierten Befehlssatz mit einigen wenigen Adressierungsarten. Eine Übersicht über alle Assemblerbefehle des Prozessors in Kombination mit den zulässigen Adressierungsarten ist in Tabelle 2 aufgeführt.

Alle Befehle des Prozessors haben eine feste Länge von 18 bit und ein weitgehend einheitliches Befehlsformat. Bild 2 zeigt die Befehlsformate des Prozessors, dabei sind einzelne Bit-Stellen in Abhängigkeit von deren Bedeutung mit unterschiedlichen Buchstaben gekennzeichnet. Bit-Stellen mit dem Operations-Code sind durch den Buchstaben c markiert. Die Registeradressen des ersten und des zweiten Operanden tragen entsprechend die Buchstaben x und y. Die Registeradresse des ersten Operanden fungiert gleichzeitig als die Registeradresse für das Ergebnis einer arithmetischen/ logischen Operation oder eines Transportbefehls.

Mit dem Buchstaben k ist ein 8-bit-Wert gekennzeichnet, der in Abhängigkeit von der Adressierungsart entweder als eine 8-bit-Konstante (bei unmittelbarer Adressierung) oder als 8-bit-Adresse (bei direkter Adressierung) interpretiert wird.

Der Buchstabe a markiert eine 10-bit-Adresse, mit der der Befehlszähler PC bei der Ausführung von Steuerfluss-Befehlen geladen wird (absolute Adressierung).

Im Befehlsformat von Steuerfluss-Befehlen befindet sich auch ein 3-bit-Feld, das mit dem Buchstaben b gekennzeichnet ist. Die Codierung in diesem Feld gibt vor, wie die Statusbits C und Z während der Ausführung von Steuerfluss-Befehlen auszuwerten sind.

Das Befehlsformat für Interrupt-Befehle enthält neben dem Operationscode nur eine 1-bit-Stelle, die direkt in das Interrupt-Enable-Bit kopiert wird.

- Ein 8-bit-Softcore-Prozessor für programmierbare Logik

- Ein 8-bit-Softcore-Prozessor für programmierbare Logik

- Ein 8-bit-Softcore-Prozessor für programmierbare Logik

- Entwicklungsumgebung