Ein 8-bit-Softcore-Prozessor für programmierbare Logik

Fortsetzung des Artikels von Teil 1

Ein 8-bit-Softcore-Prozessor für programmierbare Logik

Der PicoBlaze ist in den Hardware-Beschreibungssprachen Verilog und VHDL implementiert worden. Seine Strukturbeschreibung besteht aus primitiven FPGA-Komponenten der Spartan-3-Familie wie Look-Up-Tabellen, Multiplexer, Flipflops und Speichermodule. Beispielsweise umfasst die VHDL-Beschreibung des Prozessors ungefähr 2000 Zeilen Programmcode, wovon etwa 400 Zeilen für die VHDL-Simulation vorgesehen sind. Nach der Synthese für einen FPGA-Baustein vom Typ XC3S200 belegt der PicoBlaze 96 Slices (das sind knapp 5 % der FPGA-Ressourcen). Obwohl der Prozessor als Komponentenliste mit den primitiven FPGA-Elementen modelliert ist, lassen sich einige Merkmale seiner Architektur relativ leicht modifizieren oder erweitern. Dazu gehören z.B. die Erweiterung des Befehlssatzes, die Größe des Notizblock-Speichers oder die Kapazität des Return-Stacks.

Jobangebote+ passend zum Thema

Prozessorstruktur

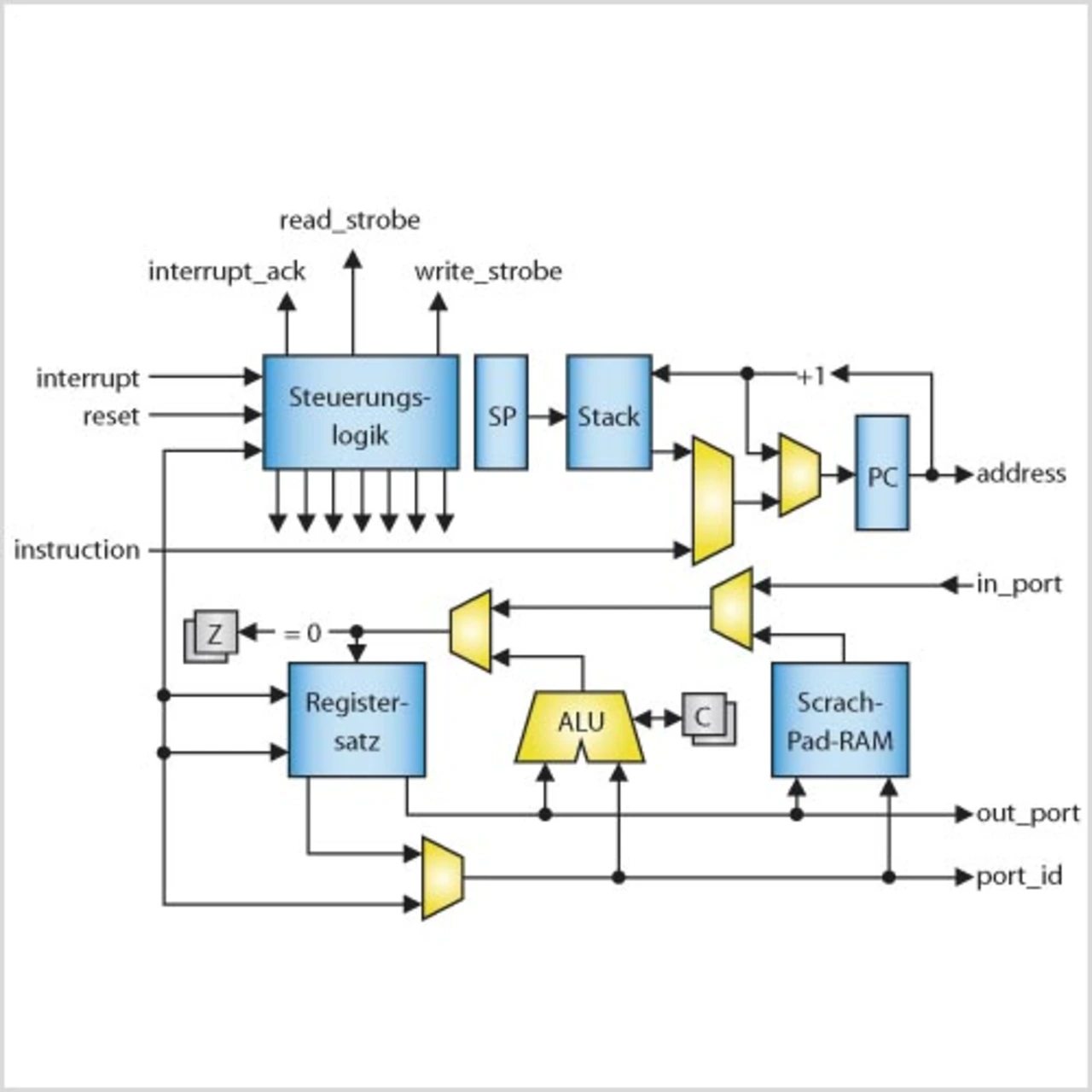

Der PicoBlaze ist aus mehreren Funktionsblöcken aufgebaut, die direkt oder über Multiplexer miteinander verbunden sind. Bild 1 zeigt die interne Prozessorstruktur, die unmittelbar aus der VHDL-Beschreibung rekonstruiert ist. Die Steuerlogik mit Schnittstellen-Signalen, ein Return-Stack mit einem Stack-Pointer SP und ein Befehlszähler PC mit dazugehöriger Inkrementierund Lade-Logik bilden das Steuerwerk. Das Rechenwerk umfasst den Registersatz, eine arithmetisch-logische Einheit (ALU), zwei Statusbits (C und Z), einen Notizblock-Speicher (Scratch-Pad-RAM) sowie Ein-/Ausgabe-Ports.

Die Steuerlogik dient zur Generierung interner und externer Steuersignale aus dem aktuellen Prozessorzustand und dem Operations-Code. Sie enthält u.a. das IE-Bit (Interrupt-Enable-Bit), mit dem per Software Interrupts freigeschaltet oder gesperrt werden können. Der Return-Stack hat eine Kapazität von 32 Einträgen und wird von dem 5-bit-Stack-Pointer SP adressiert. Auf dem Stack werden Rücksprungadressen bei Aufrufen von Unterprogrammen oder bei Interrupts abgelegt. Der Befehlszähler ist ein 10-bit-Register mit einer Adresse, die auf den Programmspeicher mit dem auszuführenden Befehl verweist. Bei der Ausführung sequenzieller Befehlsfolgen wird der PC um 1 inkrementiert. Bei der Ausführung bedingter oder unbedingter Sprungbefehle wird der PC mit der Zieladresse aus dem Befehlswort geladen.

Der Registersatz des Prozessors enthält 16 universelle 8-bit-Register und ist als Zwei-Port-Speicher ausgelegt. Dadurch ist es möglich, in einem Taktzyklus zwei Operanden gleichzeitig auszulesen und das Ergebnis der Operation zurückzuschreiben. Die ALU ist auf die Ausführung von 8-bit-Operationen ausgelegt und setzt sich aus drei Modulen zusammen: einem Addierer/Subtrahierer, einer Shift-/Rotationslogik und einem Modul für logische Operationen. Der Prozessor verfügt noch über zwei Statusbits mit den dazugehörigen Shadow-Bits. Das C-Bit (Carry) dient als Übertragsbit bei Additionen, Subtraktionen und Shift-/Rotationsoperationen; das Z-Bit (Zero) dient als Indikator dafür, dass das Ergebnis einer arithmetischen/logischen Operation Null war. Der Notizblock-Speicher ist ein lokaler Datenspeicher mit 64 byte, auf den der Prozessor nur mit Hilfe von Load-/ Store-Befehlen zugreifen kann.

- Ein 8-bit-Softcore-Prozessor für programmierbare Logik

- Ein 8-bit-Softcore-Prozessor für programmierbare Logik

- Ein 8-bit-Softcore-Prozessor für programmierbare Logik

- Entwicklungsumgebung