Superskalarer SH-Mikrocontroller mit 480 MIPS Rechenleistung für industrielle Anwendungen

Echtzeitfähiger Kommunikationskünstler

Fortsetzung des Artikels von Teil 4

Echtzeitfähiger Kommunikationskünstler

Operation | Ausführungszeit |

sin | 680 ns |

cos | 650 ns |

tan | 900 ns |

arcsin | 995 ns |

arccos | 1225 ns |

arctan | 695 ns |

log | 910 ns |

exp | 950 ns |

pow | 1140 ns |

| Tabelle: Ausführungszeiten der Gleitkomma-Einheit (FPU) bei typischen mathematischen Operationen mit doppelter Genauigkeit | |

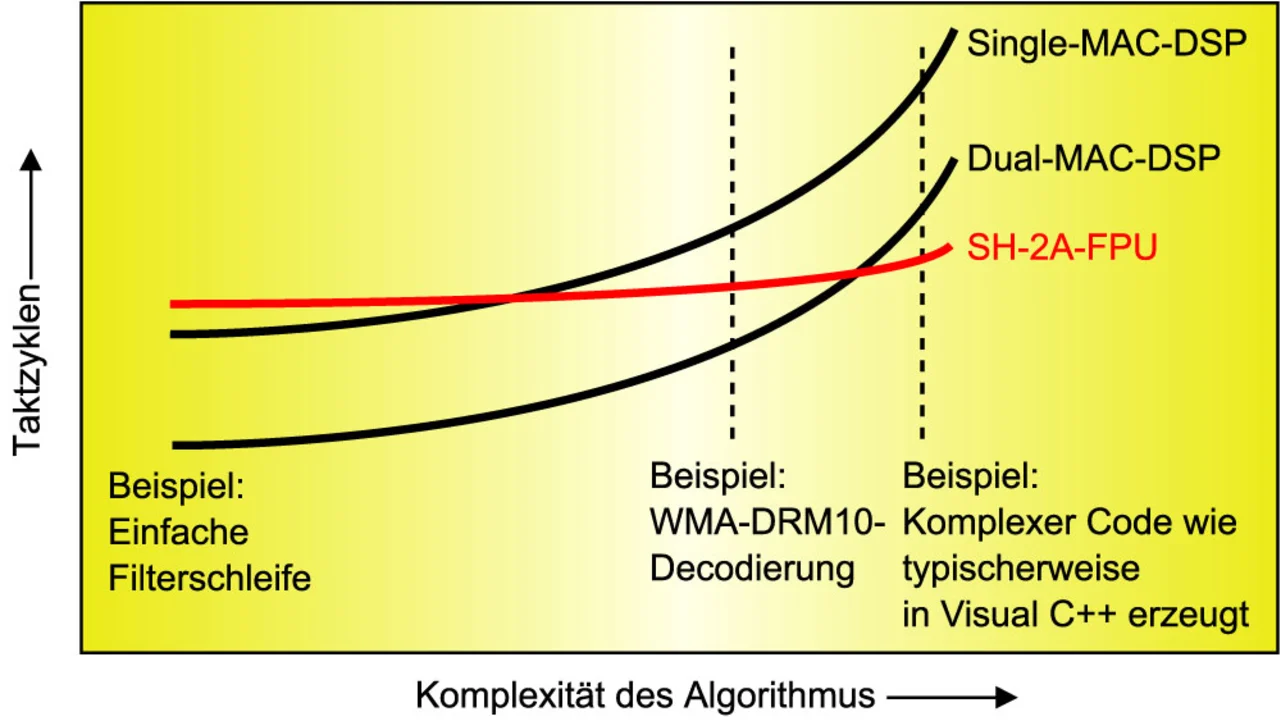

Vergleichstests haben gezeigt, dass die SH-2A-FPU gerade bei zunehmend komplexer werdenden Algorithmen wesentlich besser als klassische DSPs abschneidet (Bild 2). Besonders deutlich sichtbar wird dieser Effekt, wenn hochkomplexer Gleitkomma-Code von PC-Systemen, der üblicherweise in Visual C++ entwickelt wurde, auf Embedded-Systeme portiert werden muss.

Der integrierte DMA-Controller verfügt über acht Kanäle und entlastet die CPU von reinen Datentransfer-Aktivitäten zwischen den Speicherbereichen oder zwischen Speicher und den On-Chip-Modulen. Er unterstützt „Burst“- und „Cycle-Steal“-Mode und ist in der Lage, in der Mitte oder am Ende des Transfers einen Interrupt zu erzeugen, um auch beim Verarbeiten von größeren Blöcken schnell auf höher priorisierte Ereignisse reagieren zu können.

Jobangebote+ passend zum Thema

Bei der Realisierung von Echtzeit-Anwendungen ist die Verarbeitungsgeschwindigkeit von Interrupts ein wesentliches Kriterium. Dem Interrupt-Controller des SH7203 stehen 15 Register-Bänke zur Verfügung (Bild 3), wodurch sehr schnelle Kontext-Umschaltzeiten ermöglicht werden. Lediglich das Status-Register und der Programm-Zähler (PC) müssen im Stack gespeichert werden. Die minimale Antwortzeit auf einen Interrupt beträgt somit nur noch sechs Taktzyklen.

Der Cache-Speicher des SH7203 stellt zwei getrennte, 8 Kbyte große Speicherblöcke für Daten und Instruktionen bereit, wobei jeder – in 4 Blöcke unterteilt – jeweils 128 Einträge (Lines) enthält (4-way set-associative Cache). Eine Cache-Zeile ist dabei mit 16 byte genau so groß, dass sie mit einem einzigen SDRAM-Burst-Zugriff gefüllt wird. Aus diesem Grund ist der Einsatz eines SDRAM mit Burst-Modus gegenüber einem externen SRAM oder Flash-Speicher immer die schnellere Alternative. Dies sollte man bei Leistungs-Messungen mit SDRAMs nicht vergessen. Hier gilt: Grundsätzlich den Cache einschalten! Daten, die im Cache liegen und nicht überschrieben werden dürfen, können in einen definierten Bereich geladen und anschließend mit einem Bit verriegelt werden.

Zusätzlich zum integrierten Cache-Speicher verfügt der SH7203 auch über ein 64 Kbyte großes, in vier Blöcke aufgeteiltes „High-Speed-RAM“ und ein mit bis zu 33 MHz getaktetes, am Peripheriebus angeschlossenes 16-Kbyte-„Low-Speed-RAM“. Der schnelle Speicher kommt vor allem in Echtzeit-Anwendungen zum Einsatz, zum Beispiel wenn ein deterministisches Verhalten der Software gefragt ist. Der langsame Speicher lässt sich in Verbindung mit dem „Deep-Stand-by“-Modus unter anderem zur Datenerhaltung nutzen. In diesem Modus wird auf dem ganzen Chip der Takt abgeschaltet, und die Daten im Low-Speed-RAM stehen nach einem „Power-on-Reset“ der Software als Initialisierungswerte zur Verfügung.

- Echtzeitfähiger Kommunikationskünstler

- Komplettes IDE erleichtert den Einstieg

- USB-Schnittstelle mit bis zu 480 Mbit/s

- On-Chip-Peripherie kommt der eines Computermoduls nahe

- Echtzeitfähiger Kommunikationskünstler