Superskalarer SH-Mikrocontroller mit 480 MIPS Rechenleistung für industrielle Anwendungen

Echtzeitfähiger Kommunikationskünstler

Die klassischen Industrie-PCs bekommen Konkurrenz auf Chip-Ebene. Ein neuer 32-bit-Controller mit superskalarer Architektur liefert bei einer Taktfrequenz von 200 MHz eine Rechenleistung von 480 MIPS und stellt darüber hinaus zahlreiche Kommunikations-Schnittstellen zur Verfügung. Niedrige Interrupt-Reaktionszeiten gewährleisten ein hohes Maß an Echtzeit-Fähigkeit.

Superskalarer SH-Mikrocontroller mit 480 MIPS Rechenleistung für industrielle Anwendungen

Die klassischen Industrie-PCs bekommen Konkurrenz auf Chip-Ebene. Ein neuer 32-bit-Controller mit superskalarer Architektur liefert bei einer Taktfrequenz von 200 MHz eine Rechenleistung von 480 MIPS und stellt darüber hinaus zahlreiche Kommunikations-Schnittstellen zur Verfügung. Niedrige Interrupt-Reaktionszeiten gewährleisten ein hohes Maß an Echtzeit-Fähigkeit.

Jobangebote+ passend zum Thema

Nicht nur die moderne Antriebstechnik erfordert immer schnellere Regelalgorithmen. Auch in der Bildverarbeitung sowie der Versorgung und Überwachung großer Gebäudekomplexe oder in der Steuerung kompletter Produktionsprozesse spielt das Thema Echtzeit-Fähigkeit eine immer wichtigere Rolle. Ohne leistungsfähige 32-bit-Controller mit entsprechend optimierten Timer-Strukturen, schnellen integrierten Peripheriefunktionen, kurzen Interrupt-Zeiten und umfangreichen Kommunikations-Schnittstellen läuft deshalb in diesen Bereichen inzwischen so gut wie nichts mehr. Auf dieses spezielle Anforderungsprofil hat Renesas die neue SH-2A-Mikrocontroller-Familie zugeschnitten.

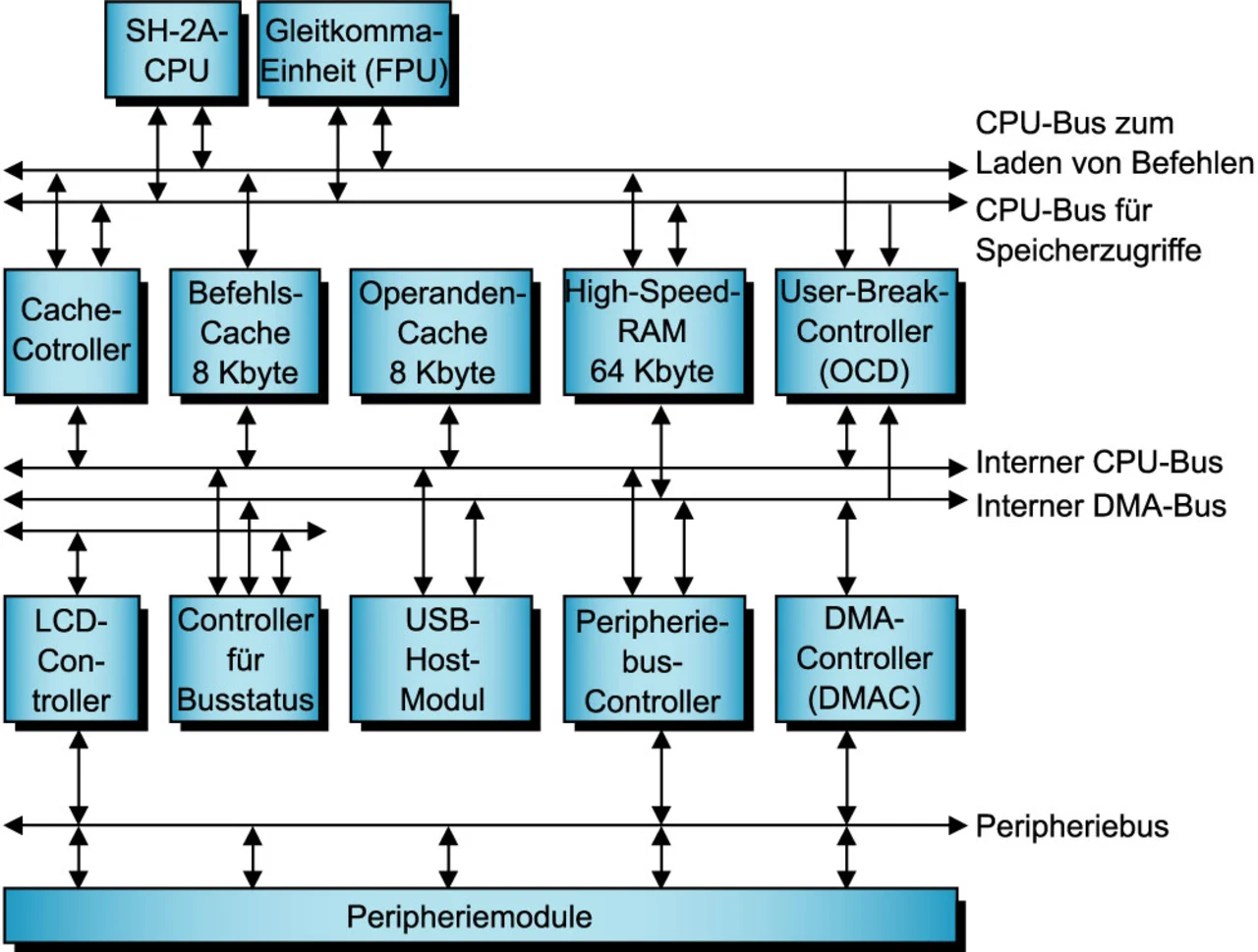

Um den 32-bit-RISC-Controller SH7203 als ernsthafte Alternative zu klassischen Industrie-PCs ins Spiel zu bringen, trieben die Entwickler gehörigen Aufwand. Herzstück des SH7203 ist eine superskalare 200-MHz-CPU mit Harvard-Architektur, fünf unabhängigen Bussystemen sowie einem speziellen Bus für den auf dem Chip integrierten LCD-Controller (Bild 1). Durch den Einsatz einer fünfstufigen Pipeline wird eine optimale Auslastung aller Funktionseinheiten erreicht. Im Zusammenspiel mit der internen MAC-Einheit (Multiply/ACcumulate), dem achtkanaligen DMA-Controller (Direct Memory Access) und dem schnellen Daten- und Befehls-Cache lassen sich so bis zu 480 Millionen Instruktionen pro Sekunde abarbeiten.

Neuer Befehlssatz und höhere Code-Effizienz

Der Befehlssatz des SH-2A ist abwärtskompatibel zu dem des SH-2, so dass sich für den SH-2 geschriebene Programme weiterhin verwenden lassen. Das hilft heutigen SH-2-Anwendern, den Schritt vom SH-2 auf den SH-2A mit minimalem Aufwand zu vollziehen. Zudem wurde der bisherige 16-bit-Befehlssatz um neue 32-bit-Instruktionen und Adressierungsarten ergänzt. Zu den jetzt insgesamt 112 Befehlen gehören unter anderem auch 21 Instruktionen für die Gleitkomma-Einheit (Floating-Point Unit – FPU).

Mit den neuen 32-bit-Befehlen lassen sich 20 bit breite Konstanten oder Adressen direkt im Befehls-Code verarbeiten. Der Programm-Code kann so deutlich kompakter angelegt werden als mit 16-bit-Befehlen, bei denen zum Beispiel die Adressinformationen in Form von Tabellen im Speicher abgelegt werden mussten. Bei typischen Anwendungen reduziert sich der Speicherbedarf dadurch um etwa 25 %, was wiederum in der Regel eine Reduktion der Systemkosten zur Folge hat. Darüber hinaus unterstützt der SH-2A die folgenden Instruktionen, die zu einer Verbesserung der Echtzeit-Fähigkeit und der Code-Effizienz führen:

- Bit-Operations-Befehle zur Steigerung der Echtzeit-Fähigkeit,

- Instruktionen zur schnelleren Implementierung von 32-bit-Divisionen mit einem einzigen Befehl,

- Barrel-Shift-Instruktionen für arithmetisches und logisches Verschieben um eine beliebige Anzahl von Stellen,

- Store-Multi/Load-Multi-Instruktionen zur Codierung der bei Unterprogramm-Aufrufen benötigten Stack-Save/Restore-Operationen für CPU-Universalregister mit einem einzigen Befehl.

- Echtzeitfähiger Kommunikationskünstler

- Komplettes IDE erleichtert den Einstieg

- USB-Schnittstelle mit bis zu 480 Mbit/s

- On-Chip-Peripherie kommt der eines Computermoduls nahe

- Echtzeitfähiger Kommunikationskünstler