Fallstudie: Entwicklung einer SystemVerilog-Testbench #####

Fortsetzung des Artikels von Teil 1

Fallstudie: Entwicklung einer SystemVerilog-Testbench

Jobangebote+ passend zum Thema

Vielschichtiger Aufbau der Umgebung

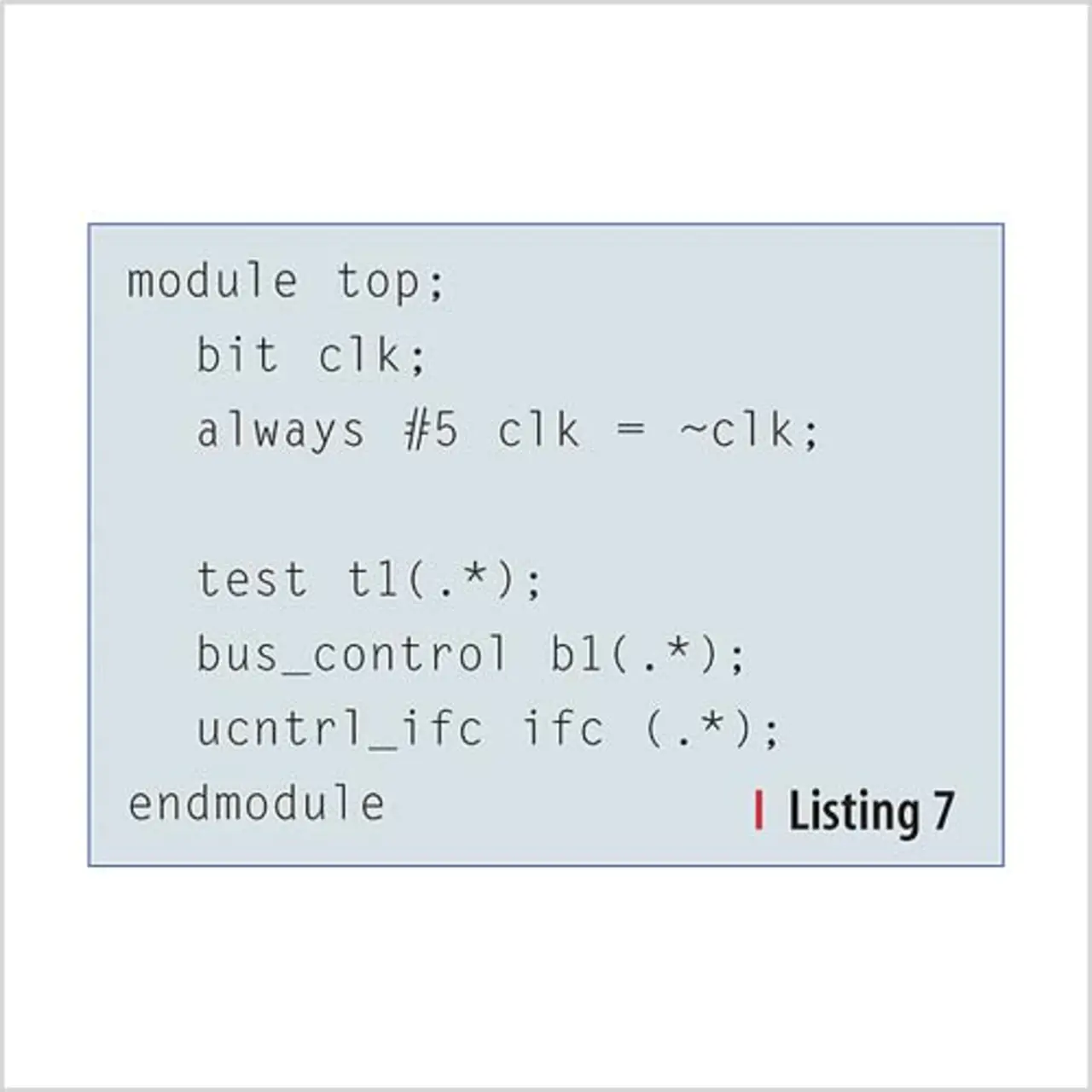

Die Testbench-Blöcke sind in einer Umgebungsklasse (environment) enthalten. Das VMM spezifiziert neun Schritte hin zu einer kompletten Simulation:

- Erzeugung einer zufälligen Konfiguration. Durch zufällige Definition der gesamten Umgebung – sowohl des DUT als auch umgebender Blöcke – können Chipdesigner zuversichtlich sein, dass sie den Baustein so getestet haben, wie er im produktiven Einsatz genutzt wird. Die Anzahl an Transaktionen wird ebenfalls zufällig bestimmt.

- Aufbau der Umgebung: Instanziierung der zur Testbench gehörigen Objekte wie Generatoren, Checker, Treiber und Monitore.

- Rücksetzen des DUT.

- Konfiguration des DUT. Herunterladen der Konfigurationsinformation aus Schritt 1 in das DUT.

- Starten des Tests.

- Warten auf das Testende. Nach der Generierung aller Transaktionen müssen die Anwender warten, bis die Transaktionen durch das Design und die Scoreboards geflossen sind.

- Stoppen der Testbench-Komponenten.

- Aufräumen der Testbench.

- Generieren eines Reports bezüglich der Anzahl erfolgreicher und fehlgeschlagener Transaktionen.

- Prüfen des Scoreboards auf nicht beanspruchte Transaktionen.

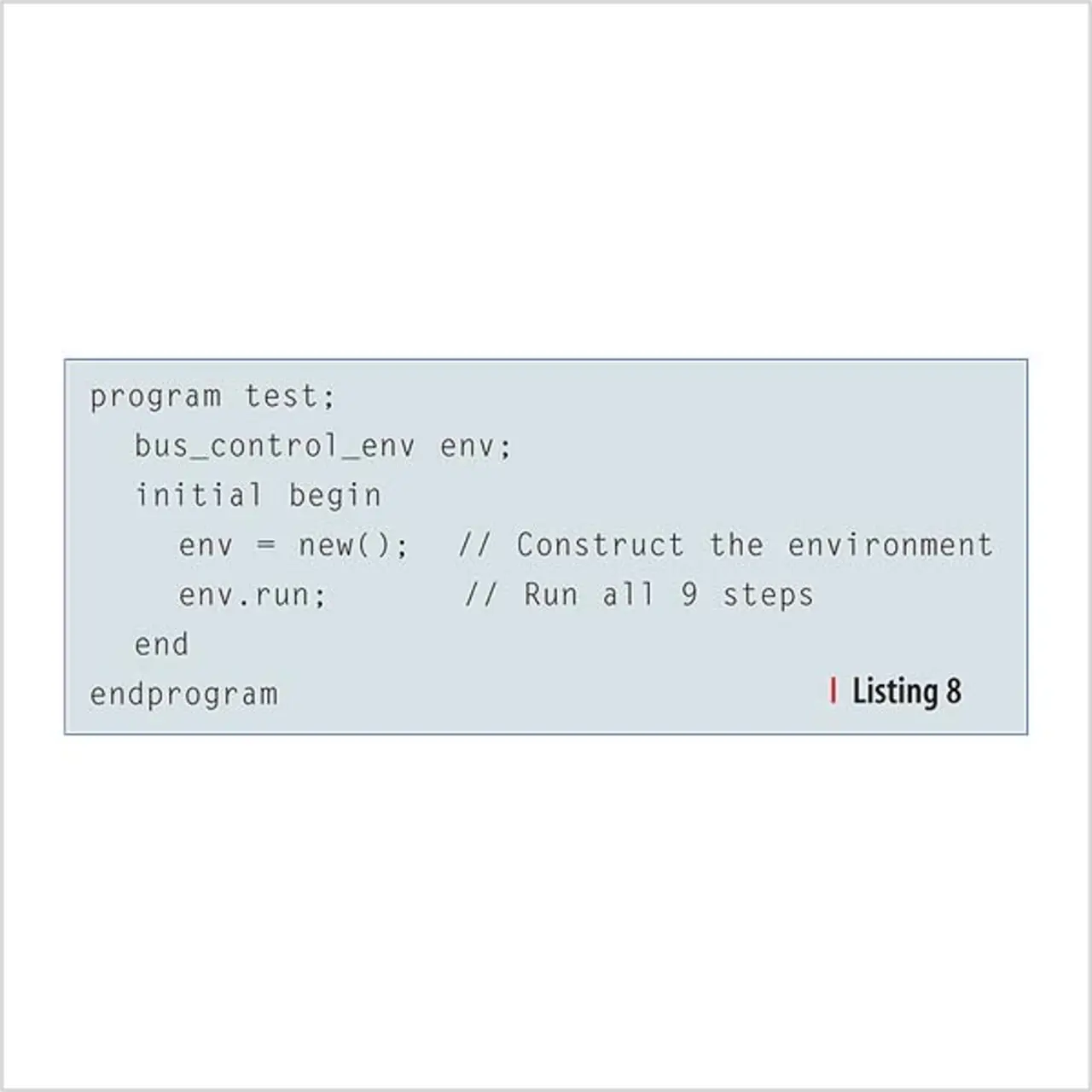

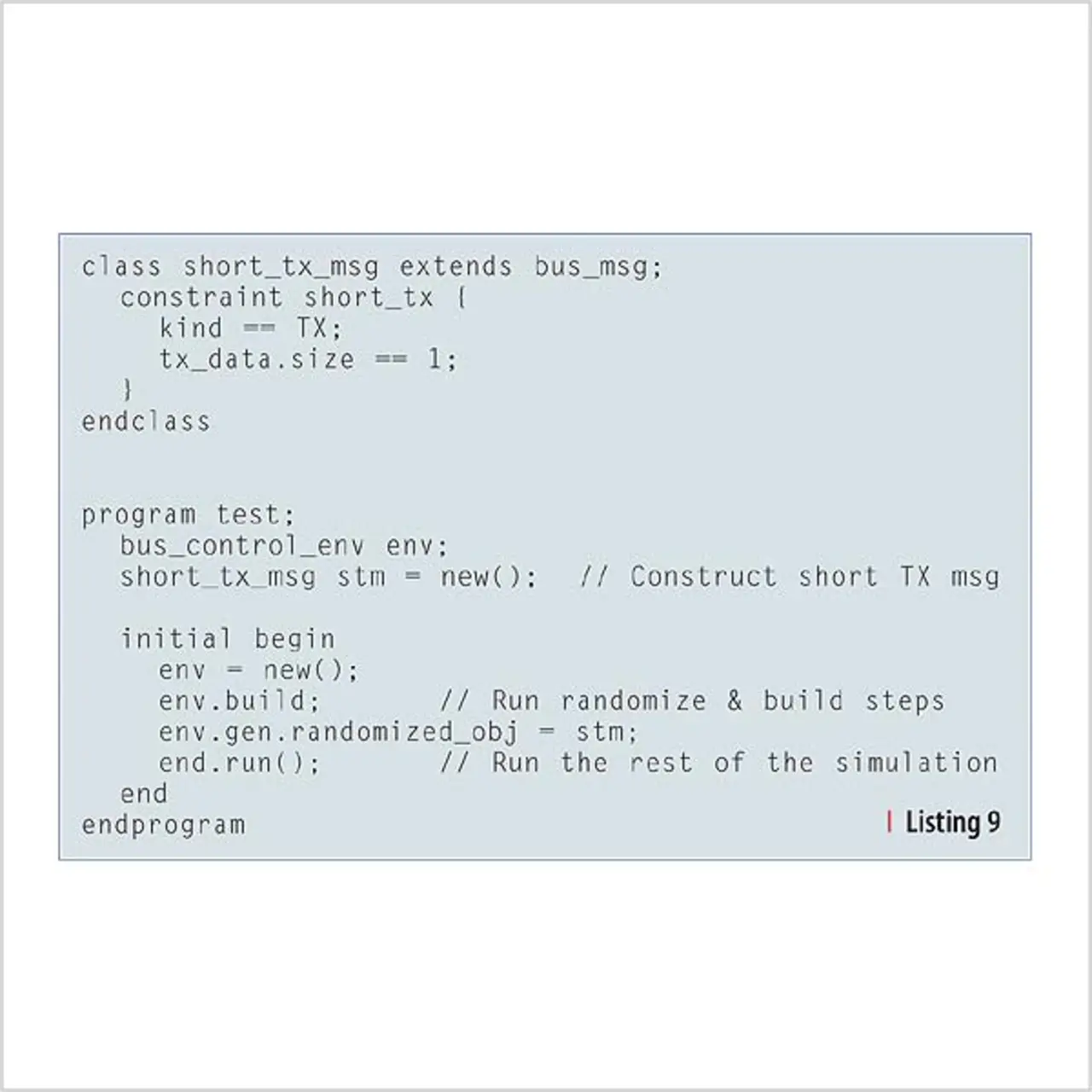

Durch die vielen Schritte kann der Anwender noch „feiner abgestuft“ als bisher auf die Testbench Einfluss nehmen. Darüber hinaus ruft die Basisklasse „vmm_env“ automatisch die ausgelassenen Schritte auf. Der grundlegendste Testcase jedenfalls sieht aus, wie in Listing 8 zusammengefasst. Chipdesigner können zudem einen neuen Stil von Nachrichten in den Generator einbringen, indem sie die originale Stimuli-Klasse erweitern und dann die Kopie im Generator ersetzen (siehe Listing 9).

| Chris Spear arbeitet als Verification-Consultant bei Synopsys und ist Autor des Electronic-Design-Automation- Bestsellers SystemVerilog for Verification. Er hat für Kunden in Europa, Japan und den USA SystemVerilog- und Vera-Testbenches entwickelt. Bevor er zu Synopsys kam, entwickelte er bei Digital Equipment einen Hardware-Simulator und war dort auch für die Prozessor-Verifikation verantwortlich. |

- Fallstudie: Entwicklung einer SystemVerilog-Testbench #####

- Fallstudie: Entwicklung einer SystemVerilog-Testbench

- Fallstudie: Entwicklung einer SystemVerilog-Testbench

- Fallstudie: Entwicklung einer SystemVerilog-Testbench

- Fallstudie: Entwicklung einer SystemVerilog-Testbench