ARM11-basierende SoCs - preiswerte Alternative für Embedded-Boards

Fortsetzung des Artikels von Teil 1

ARM11-basierende SoCs - preiswerte Alternative für Embedded-Boards

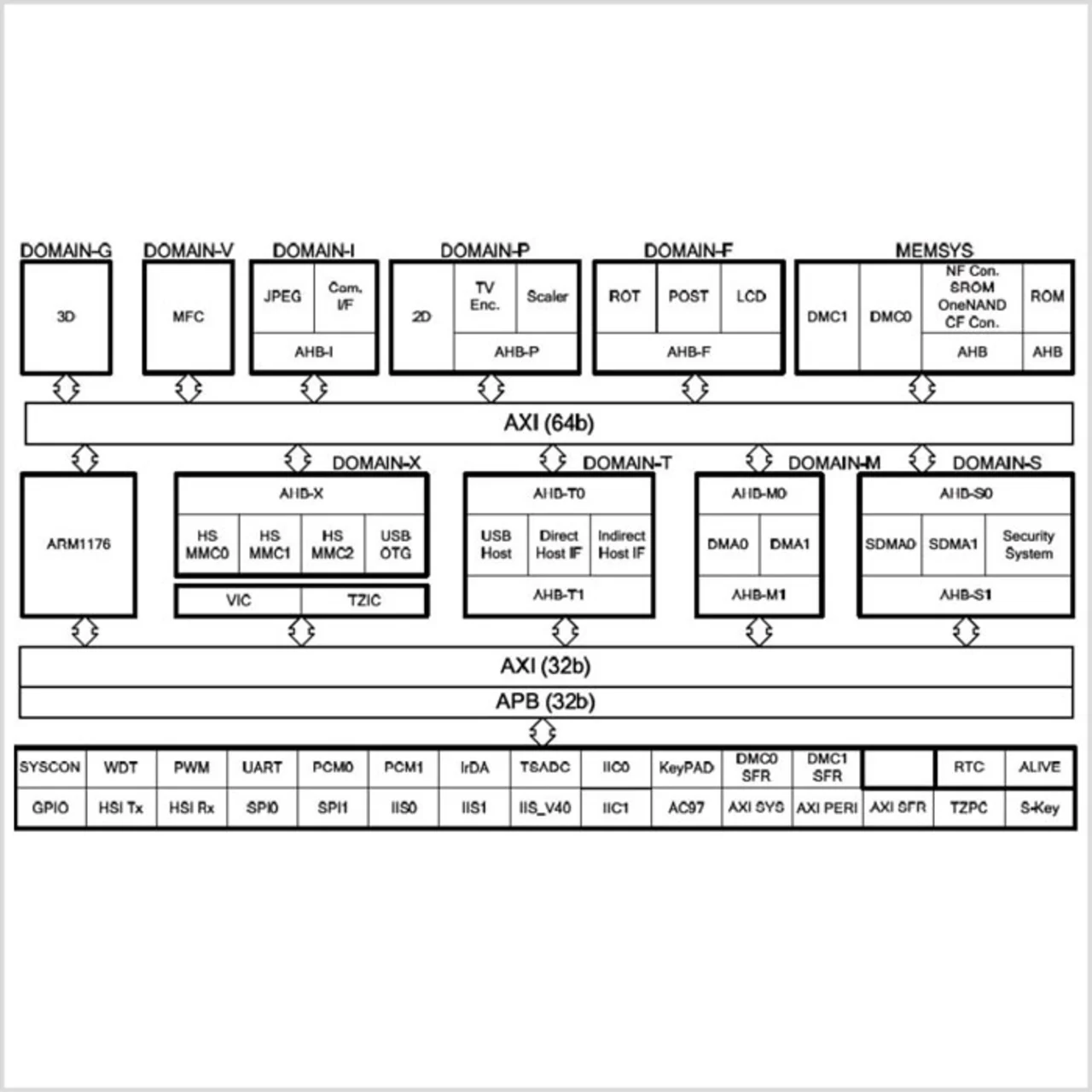

Der Advanced-Peripheral-Bus (APB) hingegen wird verwendet, um Peripherien mit geringer Anforderung an Bandbreite und Geschwindigkeit in die Prozessorarchitektur zu integrieren. Es handelt sich um ein einfaches Bus-System, bei dem lediglich Adressen, Daten und Status der Datenübertragung kommuniziert werden.

Ein weiterer wichtiger Bestandteil des ARM1176JZF-S-Core ist dessen Memory-Management-Unit (MMU). Die MMU überwacht nicht nur den Schreib- und Lesezugriff auf die jeweiligen Speicher. Zu den wesentlichen Aufgaben zählen auch die Abbildung von virtuellen Speicheradressen auf physikalische Adressen, eine Funktion, die unter anderem von Betriebssystemen benötigt wird, sowie die Überwachung und Verwaltung von Zugriffsrechten. Letztere erfolgen nach den Richtlinien von ARMs TrustZone-Technologie. Diese Technologie ermöglicht die Integration von Anwendungen, für die die Privatsphäre des Nutzers geschützt werden muss. Als mögliche Anwendung sei hier mobiles Online-Banking genannt.

Jobangebote+ passend zum Thema

Hohe Flexibität bezüglich der Befehlssätze

Der ARM1176JZF-S-Core unterstützt neben 32-bit-ARM- und 16-bit-THUMB- Befehlssätzen auch 8-bit-JAVA-Bytecodes. Zur Unterstützung von Java wird dabei auf die ARM-eigene Jazella-Technologie zurückgegriffen. Diese dient als Basis für eine Multi-Tasking-Java-Virtual-Machine und ermöglicht eine einfache und effiziente Implementierung von in Java geschriebenen Anwendungen.

Anwender des ARM1176JZF-S-Cores profitieren auch von dem um einige DSP-Funktionen erweiterten ARM-Befehlssatz. Dazu zählen neben Multiplizieren-Akkumulieren (MAC-Operationen) oder der Unterstützung von Sättigungsarithmetik auch Befehlssätze zur Verarbeitung von Multimediadaten. Hierfür wird im Wesentlichen auf SIMD (Single-Instruction-Multiple-Data)-Befehle zurückgegriffen. SIMD erlaubt einen optimierten Zugriff auf zwei 16-bit- oder vier 8-bit-Werte, die gemeinsam in einem 32-bit-Register hinterlegt sind. Die Werte werden gleichzeitig und unabhängig voneinander verarbeitet, Überträge haben auf das 32-bit-Register keine Auswirkungen. Zudem werden Sum-of-Absolute-Difference (SAD)-Befehle für die MPEG- Bearbeitung bereitgestellt. Für die zusätzlich Beschleunigung von Rechenoperationen wurde auf dem Core eine Vektor-Fliesskommaeinheit integriert.

Der ARM11-Architektur bietet dem Anwender darüber hinaus ein hohes Maß an Debug- und Boundary-Scan-Funktionalität. Als Schnittstelle zu den ARM-Debug-Tools dient eine leistungsfähige JTAG-Schnittstelle, die integrierte Embedded Trace Macrocell (ETM) erlaubt ohne Einschränkung der Rechenleistung das Tracen von Prozessorwerten. Im Core ist zudem eine Embedded-ICE-RT-Logik integriert, die diverse Break-Points ermöglicht.

Was sich mit einem ARM11-Core wie dem ARM1178JZF-S in der Praxis alles anstellen lässt, wird am Beispiel des S3C6410-Controllers von Samsung deutlich (Bild 3). Der S3C6410 verfügt über drei verschiedene AXI-Busse. Der 64 bit breite Systembus (AXI_SYS) wird mit maximal 133 MHz betrieben. Die beiden anderen AXI-Busse dienen als Zugriff auf AHB oder direkt auf SFRs. Alle Peripherien wie Speicher und Sub-Bus-Systeme, die einen hohen und schnellen Datendurchsatz fordern, sind hier angebunden. Ein weiterer, 32 bit breiter AHB dient als Schnittstelle zu einem APB für weniger performante Peripheriekomponenten wie beispielsweise Timer, serielle Schnittstellen oder I/Os. Der AHB wird wie das AXI mit maximal 133 MHz betrieben, der APB mit 66 MHz.

Neben seriellen Schnittstellen wie UART, SPI und I2C befinden sich auf dem Chip unter anderem fünf 32-bit-Timer mit zwei PWM-Ausgängen inklusive Totzeitgenerator. Der integrierte Watchdog überwacht die Funktionalität des Systems und eine Echtzeituhr plus Kalenderfunktionalität mit extra Spannungsversorgung sorgt auch im Energiesparmodus für die richtige Zeit. Und als zeitgemäße Kommunikationsschnittselle zur Außenwelt sind ein Zwei-Port-USB 1.1-Host-Controller und ein USB 2.0-OTG-Controller mit High-Speed-, Full-Speed- und Low-Speed-Unterstützung integriert.

- ARM11-basierende SoCs - preiswerte Alternative für Embedded-Boards

- ARM11-basierende SoCs - preiswerte Alternative für Embedded-Boards

- ARM11-basierende SoCs - preiswerte Alternative für Embedded-Boards

- ARM11-basierende SoCs - preiswerte Alternative für Embedded-Boards