Neue Herausforderungen beim Analog-/Mixed-Signal-Design

Fortsetzung des Artikels von Teil 2

Neue Herausforderungen beim Analog-/Mixed-Signal-Design

Effektive Analog/Mixed-Signal-Design und -Verifikation erhält man eher durch die Fähigkeit, eine „systematische Designmethodik“ zu entwickeln und zu implementieren, als durch eine durchgehende Automatisierung. Bessere Automatisierung des Analog-Layouts ist ein guter Ansatz. Heute gibt es z.B. von Mentor, Cadence und zahlreichen Startups geeignete Werkzeuge, die automatische Funktionen für das Analog-Layout bereitstellen. Diese unterstützen neue Design-Entwürfe und sind bei der Generierung eines Layouts behilflich, das die angestrebten Technologieprozesse und Transistorgrößen enthält. Das ist zwar nur „Analog-Synthese im Kleinen“, verspricht aber durchaus große Vorteile.

Jobangebote+ passend zum Thema

Parallelisieren von Analog- und Digitaldesigns

Obwohl sie nur einen kleinen Teil der gesamten Chipfläche belegen, verbrauchen Analog- und Mixed-Signal-Designprobleme weiterhin überproportional viele Chipdesign-Ressourcen. Da immer mehr SoCs Analog- und Mixed-Signal-Komponenten enthalten, müssen Digitaldesigns auch immer häufiger mit Analog-I/Os, Intellectual-Property-Kernen und Bibliotheken zurechtkommen. Dies verzögert bei traditionellen Flows sowohl die Integration dieser Komponenten als auch das IC-Layout und das Testen bis nach der Fertigung.

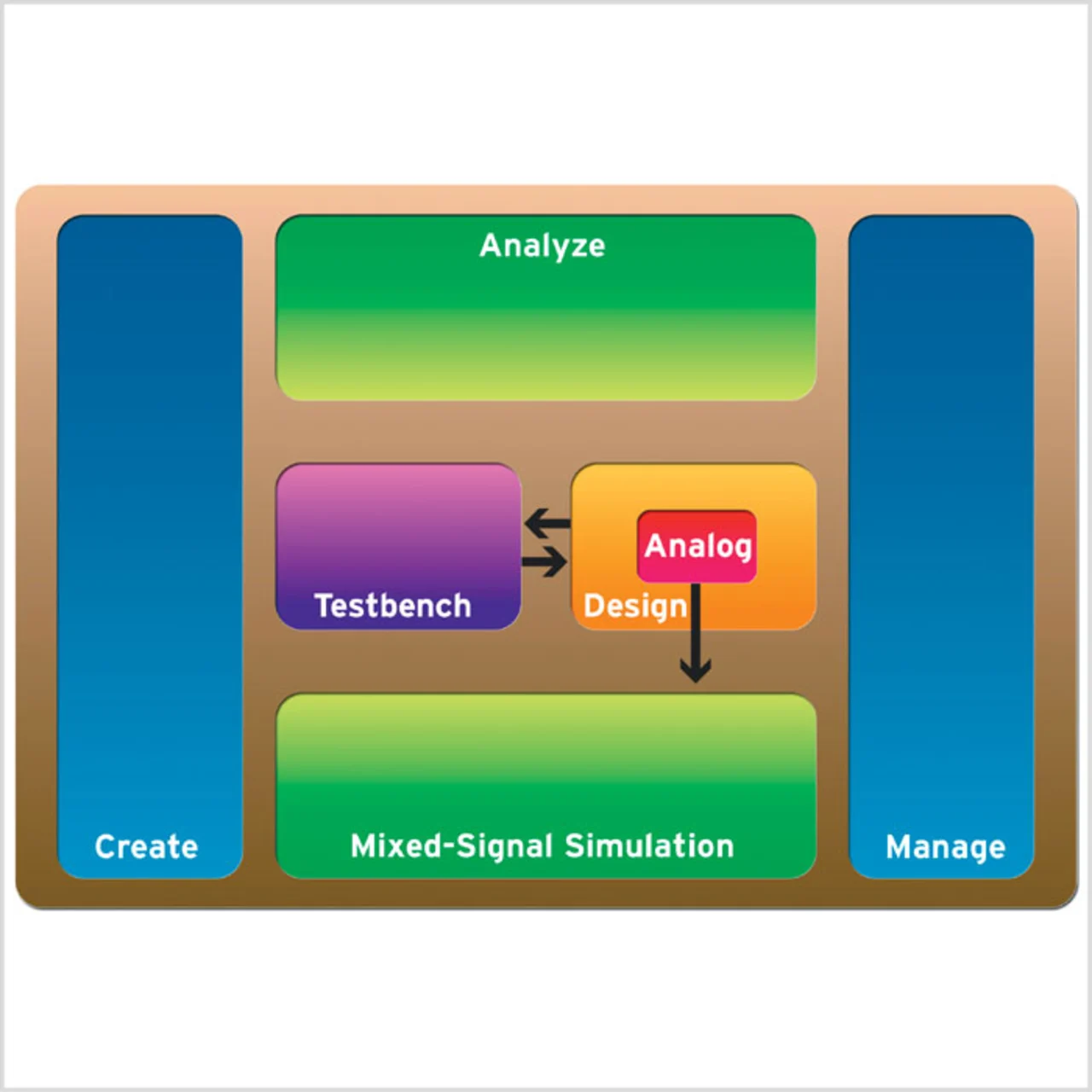

Für komplexe Chips, bei denen Design-Fehler vor dem Tapeout entdeckt werden müssen, sind modernste Mixed-Signal-Simulationswerkzeuge erforderlich. Benötigt wird eine echte Mixed-Level-Verifikationsplattform, die Mixed-Signal-Standard-Sprachen verwendet und gleichzeitig eine vereinheitlichte Simulationsumgebung verwendet. Designer müssen ferner in der Lage sein, VHDL-AMS, Verilog-AMS, VHDL, Verilog, SystemVerilog, Spice und SystemC überall und auf jedem Level im Design zu kombinieren. Dies gestattet die parallele Simulation von Analog-Blöcken, die auf Transistor-Ebene beschrieben sind, ebenso wie die von Verilog-AMS- und VHDL-AMS-Modellen; und zwar mit der gleichen Analog-Verhaltenssprache, die während der Top-down-Designphase verwendet wurde (Bild).

Ein solches Werkzeugset ist z.B. Questa ADMS von Mentor Graphics; Designern wird hier eine umfassende Umgebung zur Verifikation komplexer Analog/ Mixed-Signal-SoC Designs geboten. Questa ADMS kombiniert vier leistungsfähige Simulations-Engines in einem Werkzeug: Eldo für allgemeine Analog-Simulationen, Questa für Digitalsimulationen, ADiT für schnelle Simulationen auf Transistor-Ebene und Eldo-RF für modulierte Dauerzustandsimulationen. Linda Fosler/go

Siehe auch:

Optimierung des Rauschverhaltens von Mixed-Signal-Schaltungen

- Neue Herausforderungen beim Analog-/Mixed-Signal-Design

- Moderne Design- und Verifikations-Umgebung auf Transistorebene

- Neue Herausforderungen beim Analog-/Mixed-Signal-Design