Entwicklung eines leistungsfähigeren A/D-Wandlers

Immer in der Schleife

Die fortschreitende Weiterentwicklung der Prozesstechnologien stellt Mixed-Signal-Entwickler ständig vor neue Herausforderungen. Bei einem für den Kommunikationsmarkt konzipierten A/D-Wandler brachte der Schritt zur 65-nm-Technik derart große Probleme mit sich, dass ein komplett neues Design fällig wurde.

Mixed-Signal-Designer sollen neue Produkte entwickeln, die mit geringerer Spannung arbeiten, wenig Platz auf den Chips beanspruchen und eine geringere Rechenleistung erfordern. Manchmal lassen sich vorhandene Architekturen erweitern, da-mit diese Anforderungen erfüllt sind; andernfalls muss etwas Neues erfunden werden. Die technologischen Änderungen haben ganz spezielle Probleme für das Infineon-Projekt der Sigma-Delta-A/D-Wandler (ADC) mit sich gebracht. Bei den ADCs, die für den Kommuni-kationsmarkt be-stimmt sind, sollten die Bandbreite nach Wünschen des Unternehmens auf 20 MHz erhöht, der Energieverbrauch gesenkt und 65-nm-Prozesstechnologien eingesetzt werden. Für genau diesen Markt haben die Entwickler bei Infineon und an der Madrider Universidad Carlos III (UC3M), die seit mehr als zehn Jahren gemeinsam an Mixed-Signal-Designs arbeiten, kurz zuvor eine neuartige, zeitkontinuierliche Multibit-Sigma-Delta-Architektur entwickelt, die einen »Flash Quantizer« verwendet, also ein Quantisierungselement in Flash-Architektur. In der kleineren Prozessgeometrie sind die Spannungen niedriger, sodass die Spannungen zwischen den Widerständen im Widerstandsteiler sehr niedrig sind, was die Implementierung in Flash erschwerte. Außerdem verbrauchten die Flash-Quantisierer viel Platz auf dem Chip und viel Leistung. Kurz, ein neues Design war nötig.

Ein neues Designkonzept

Die Entwicklung eines neuen Bauteils beinhaltet viele Entwurfsiterationen. Um die Entwicklung zu beschleunigen, wählte das Team einen Konstruktionsansatz auf Systemebene. Dieser Ansatz ist sehr viel schneller als ein Design auf Schaltkreisebene. Damit konnten viele unterschiedliche Designs in der gleichen Zeit simuliert werden, die es dauern würde, eine einzige Simulation auf Schaltkreisebene durchzuführen. Auf diese Weise ließ sich auch das gesamte Projekt besser organisieren. Indem die Entwickler in einer Umgebung auf Systemebene arbeiteten, konnten die geografisch auf Madrid und Villach (Österreich) aufgeteilten Teams für sich unterschiedliche Teile des Systems konstruieren und dann dafür sorgen, dass die Einzelteile als System zusammen funktionierten.

Jobangebote+ passend zum Thema

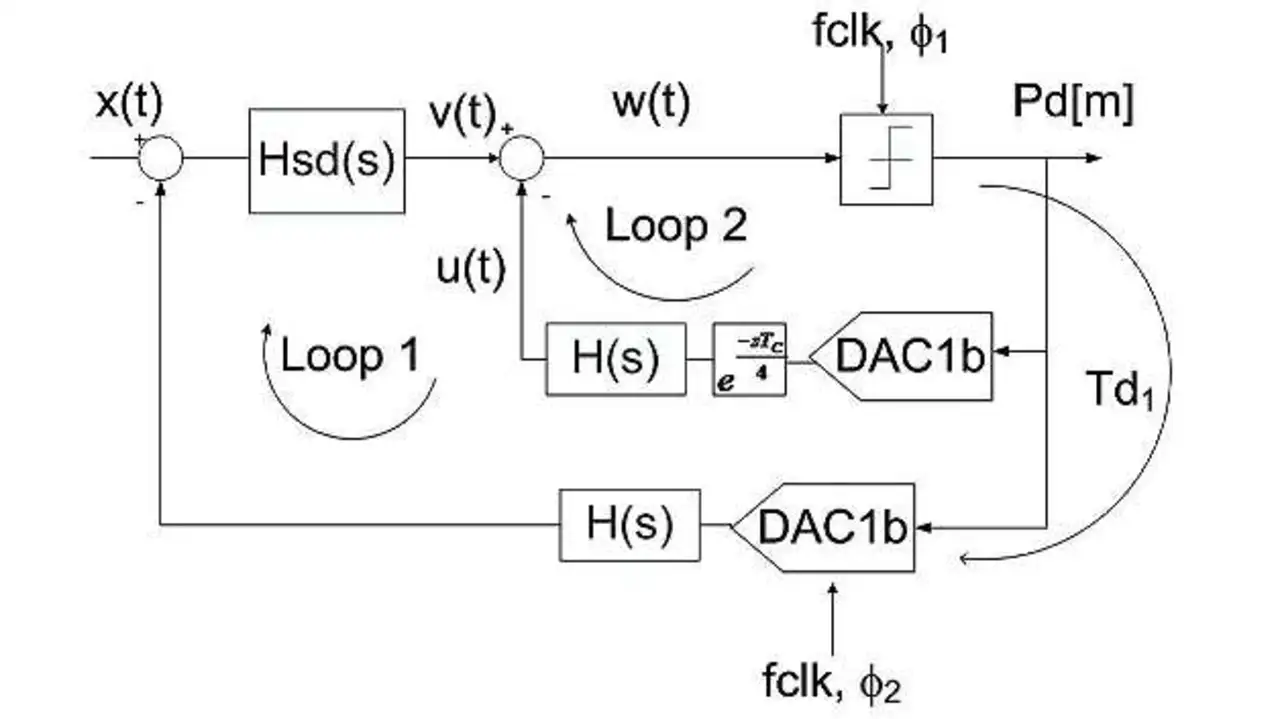

Ein Mitarbeiter, der bei Infineon für ein anderes Projekt die Zeitbereichsmodulation verwendete, schlug vor, die Zeitcodierung mit einem Pulsbreitenmodulator (PWM) zu untersuchen (Bild 1). Für ADCs wurde diese Architektur noch nie zuvor eingesetzt, doch so kann man auf den Flash-Quantisierer verzichten, da hier die Pulsbreitenmodulation bei schwankendem Binärsignal zur Quantisierung des Signals dient. Um ein neues Bauteil auf Grundlage dieser Architektur herzustellen, sollten gemeinsame Projekte zwischen UC3M und Infineon eine neuartige Sigma-Delta-Modulation der Zeitcodierung mit PWM entwickeln. UC3M konzentrierte sich dabei auf ein Design auf Systemebene, Infineon auf die Schaltkreisebene.

In Madrid wurden zunächst die Parameter für die analogen Loops berechnet. Dabei unterstützte die »Delta Sigma Toolbox« von Math-works und eine auf »Matlab« basierte Loop-Design-Bibliothek, die in den Jahren der gemeinsamen Arbeit mit Infineon aufgebaut wurde.

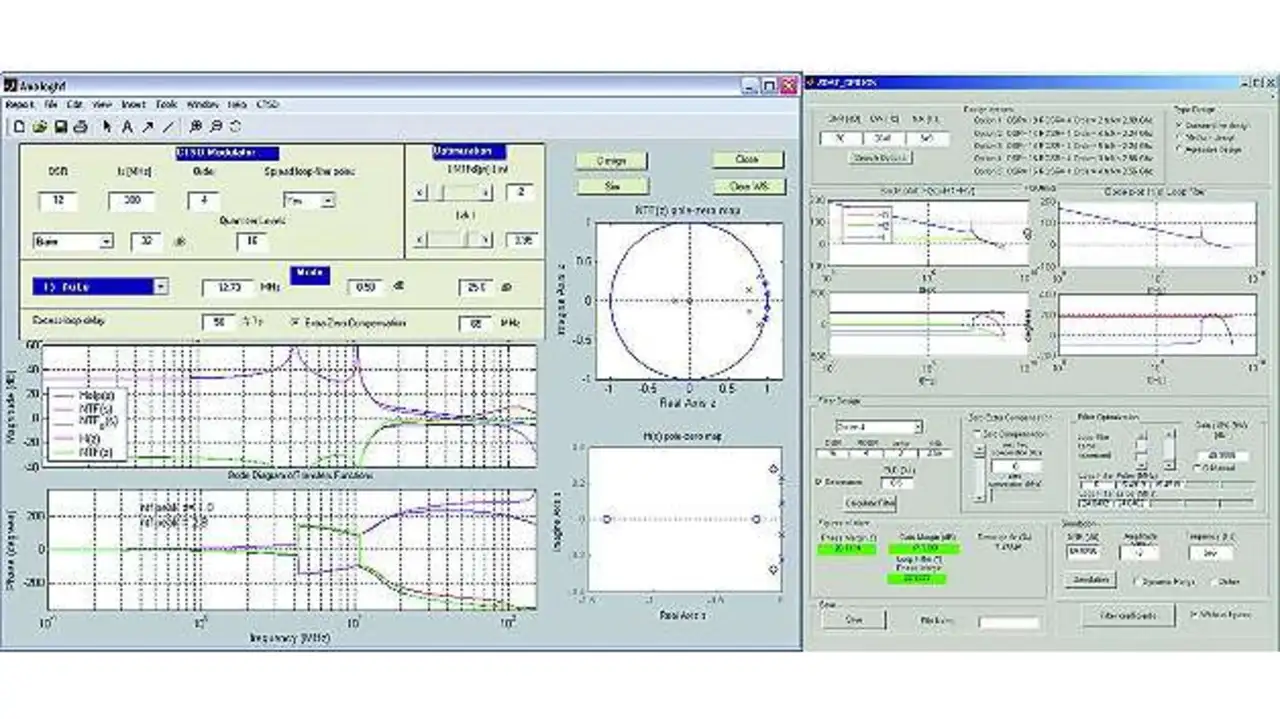

Diese Bibliothek enthält Designanwendungen, die mit dem »Matlab Guide«-Tool entwickelt wurden. Diese Anwendungen können beispielsweise die Systemleistung mit Bode-Diagrammen darstellen. Die Analysewerkzeuge ermöglichten es, allgemeine Anforderungen einzuführen (Beispiel: Signal/Rausch-Verhältnis, Bandbreite und Taktfrequenz) und zu beobachten, wie sich unterschiedliche Entwürfe auf höchster Entwurfsebene verhielten. Damit konnte die Sigma-Delta-Reihen-folge bestimmt werden (Bild 2).

Systemsimulation

In einem nächsten Schritt erstellte das Team die Modelle auf Systemebene in »Simulink«. Zwar lässt auch Matlab eine lineare Analyse von Schleifen (Loops) zu, doch war Simulink die passende Wahl für die schnelle Mixed-Signal-Systemsimulation. Dank der eigenen umfangreichen IP-Bibliothek konnten verschiedene Topologien schnell getestet werden. Sobald die Entwickler ein funktionsfähiges Design in Händen hatten, fügten sie Störungen wie Jitter, finite Verstärkerbandbreite, Abweichungen der Kondensatoren und DACs sowie thermisches Rauschen hinzu. Die Simulationen auf Systemebene sollten sich so realistisch wie möglich gestalten.

Der Ersatz des Flash-Quantisierers durch eine asynchrone PWM beeinflusste die Schleifendynamik im System. Demzufolge galt es, die Parameter anzupassen und Designänderungen vorzunehmen. Die neue Architektur erforderte es auch, neue Designtools in Matlab zu erstellen. Zu Testzwecken dienten Matlab-Skripte, um die Simulink-Modellparameter zu variieren. Einige dieser Skripte wurden über eine grafische Benutzeroberfläche gesteuert. Für Parameter-Sweeps muss traditionell eine große Anzahl Simulationen gefahren werden, weshalb die Simulationsgeschwindigkeit wichtig ist, um schnell Ergebnisse zu erhalten.

Bei Infineon wurde überwiegend an den digitalen Designkomponenten gearbeitet. Ursprünglich betrachtete man mehrere unterschiedliche Architekturansätze, um das Quantisierungsrauschen durch die digitale Filterung zu reduzieren. Das beste diesbezügliche Ergebnis lieferte die PWM-Architektur namens »MASH« (Multi-Stage Noise Shaping) eines Mitarbeiters. Solche Architekturen sind an sich nicht neu, aber ihre Anwendung auf PWM schon. Das Problem dabei war, dass eine genaue Zeitauflösung erforderlich war. Das bedeutete eine Taktung der Modulatoren mit hoher Frequenz.

Bei physikalischen Taktgebern gibt es immer einen Restfehler bei der zeitlichen Steuerung. In MASH-Architekturen hingegen lässt sich dieser Fehler kompensieren. Die Idee für das Konzept war, den Fehler mit einem digitalen Filter zu bestimmen, um die Rauschübertragungsfunktion (NTF) des Modulators abzuschätzen. Der geschätzte Fehler wurde vom Signal subtrahiert, und das Ergebnis war ein Leistungszuwachs von mehreren Dezibel. Auch in Villach kamen Matlab und Simulink für die Entwurfsarbeit zum Einsatz.

Die analogen und digitalen Komponenten des Systems mussten natürlich zusammenarbeiten, die beiden Entwürfe mussten integrierbar sein. Dieses Projekt war Teil einer andauernden Kooperation, die sich über mehrere Projekte und mehrere Jahre erstreckte. Physische Treffen, auf denen alle zusammenkommen, sind sehr zeitintensiv und kostspielig, so fanden alle 14 Tage Telefonkonferenzen statt, in denen die Ergebnisse austauscht wurden. Jährliche Workshops vereinten alle Teammitglieder für circa eine Woche.

In der Realität ist die Grenze zwischen den analogen und digitalen Komponenten eines Systems jedoch ziemlich unscharf: Das Analog-Team arbeitet zum Teil auch am digitalen System und umgekehrt. In Villach wurde beispielsweise untersucht, wie das analoge Design aus Madrid den digitalen Teil des Systems beeinflusste. Auch die digitalen und analogen Design-komponenten wurden zusammengeführt, um zu untersuchen, wie der ADC als Ganzes arbeitete. Da der Wandler Teil einer größeren Einheit war, wurde im Modell simuliert, wie alle Komponentensysteme, einschließlich des A/D-Wandlers, das Verhalten der Einheit als Ganzes auf Systemebene beeinflussten.

Sobald sich das Modell, das die Anforderungen der Entwickler erfüllte, auf Systemebene befand, konnten diese zur Implementierung auf Schaltkreisebene übergehen. Sie bauten VHDL-Modelle mit Tools von Cadence, die das Verhalten der Modelle auf System-ebene nachahmten, und ersetzten jede VHDL-Komponente durch ein Schaltkreismodell, bis das gesamte Design auf Schaltkreisebene umgesetzt war.

Testergebnisse

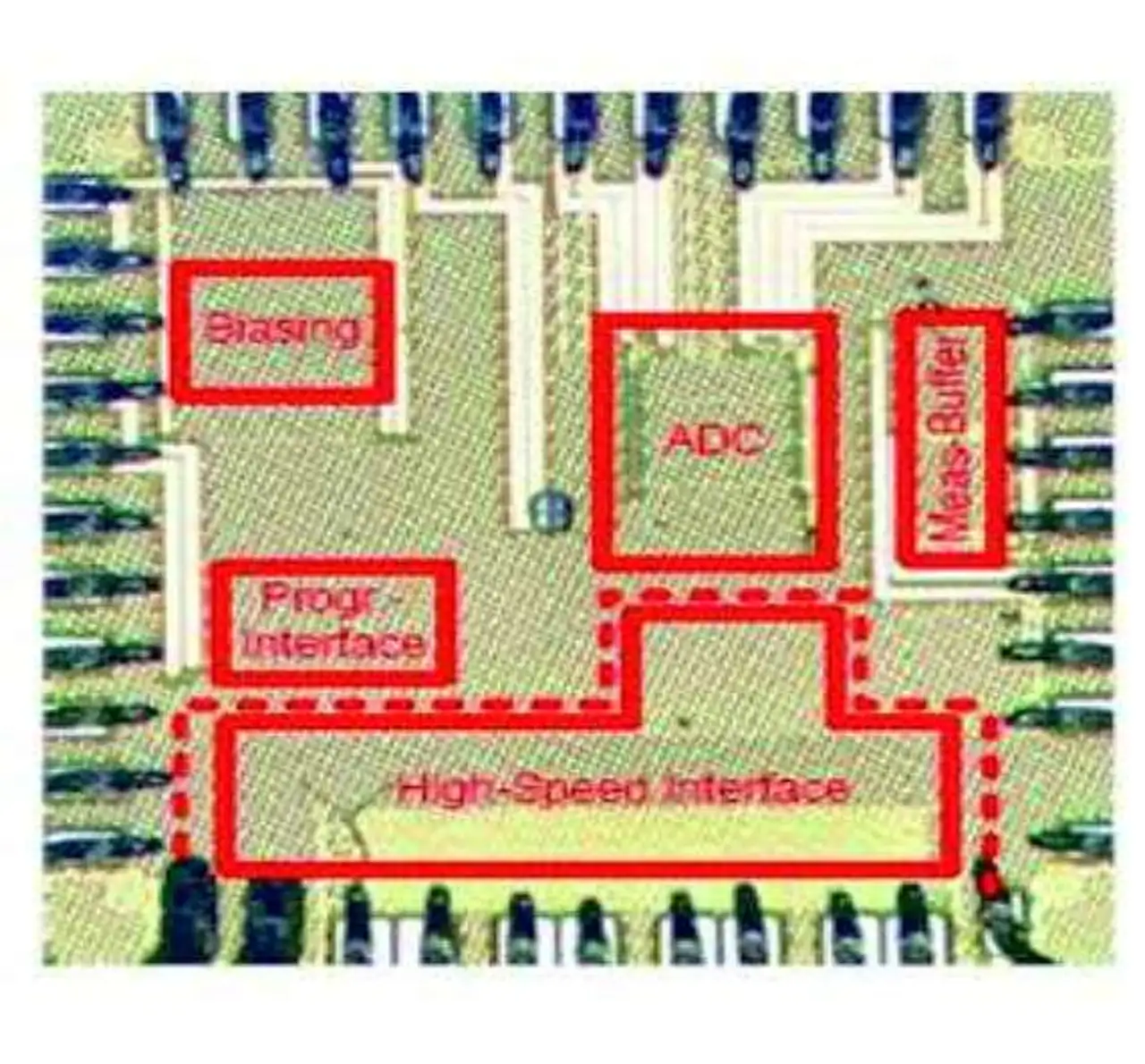

Der Chip-Prototyp im 65-nm-CMOS-Prozess (Bild 3) wurde im Labor getestet.

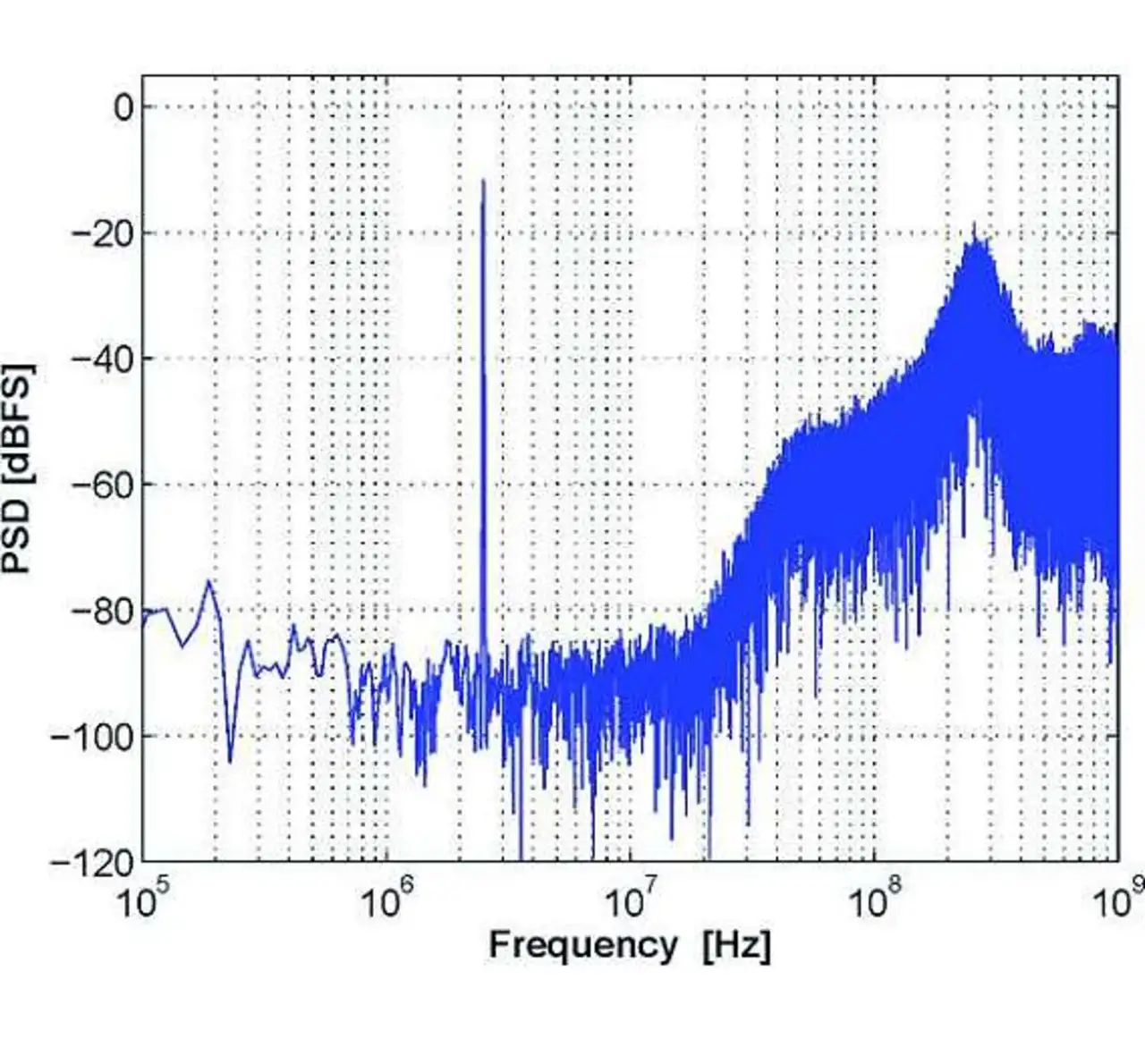

Bild 4a zeigt die gemessene spektrale Leistungsdichte der digitalen Daten, wenn ein Eingangssignalton angelegt war. Das Spektrum zeigt die Trägerfrequenz des PWM-Oszillators zusammen mit dem Eingangssignal sowie das Quantisierungsrauschen.

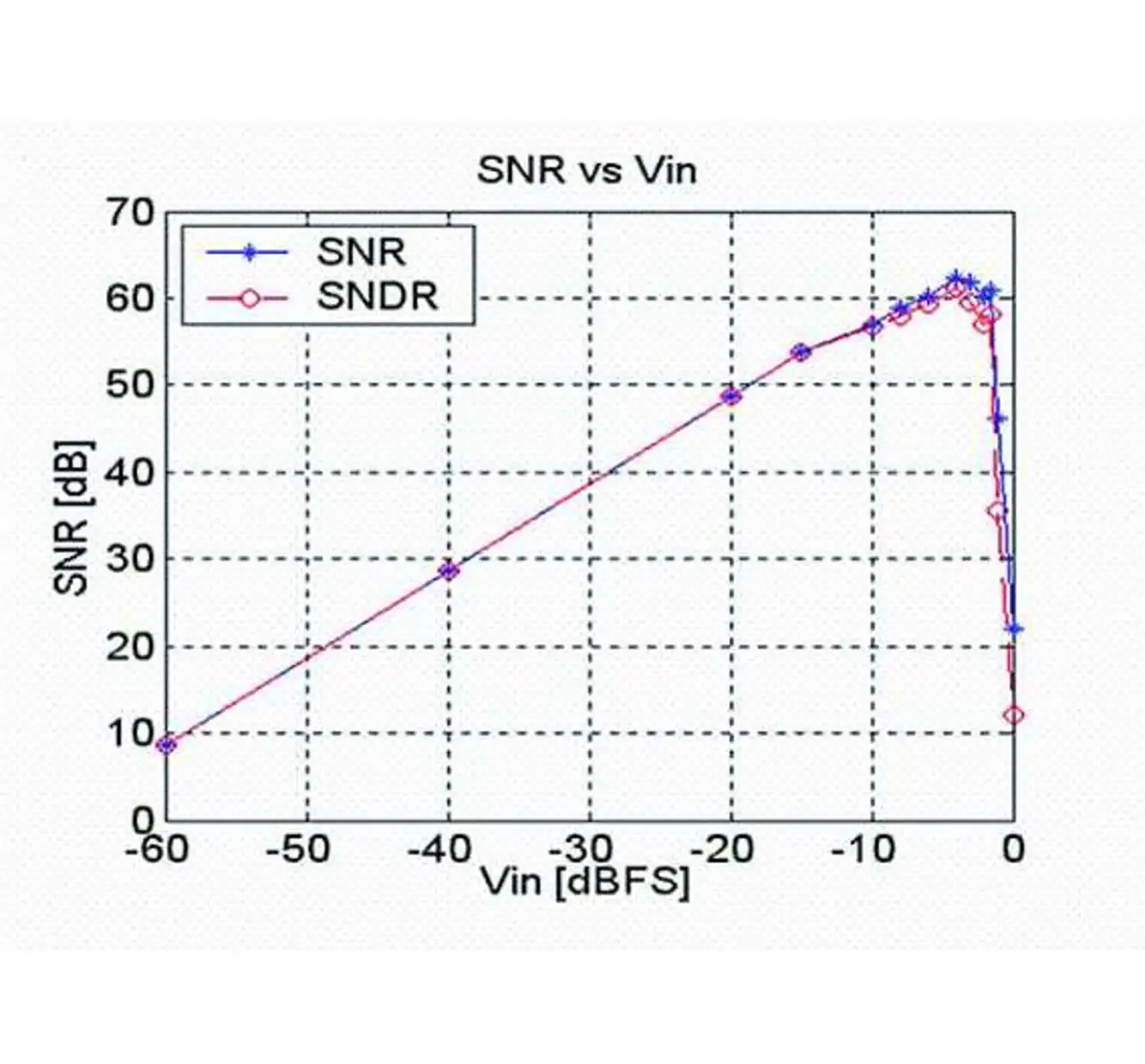

Bild 4b zeigt das gemessene Signal/Rausch-Verhältnis und den Signal/Rausch-Verzerrungsquotienten im Verhältnis zur Eingangsspannung. Dies ergibt einen dynamischen Bereich von 63 dB. Die elektrischen Messungen zeigten, dass der ADC bei einer Spannungsversorgung von 1,0 V etwa 7 mW verbrauchte. Dies lag genau im Rahmen der Anforderungen.

Der beachtlichste Vorteil dieser neuen Architektur ist der geringe Platzbedarf des Cores von 0,8 mm2. Dies ist wichtig bei der Multichannel-Kommunikation mit Ein-Chip-Systemen, in der viele Wandler aufeinander abgestimmt sind. Die Ergebnisse des Testchips ergaben, dass die Projektziele erfolgreich umgesetzt worden sind. Die Ergebnisse dieses Gemeinschaftsprojekts ermöglichen die Untersuchung vieler möglicher Designs und vieler Designparameter. Da alternative Designs sehr schnell untersucht und bewertet wurden, stellte die Simulationsschnelligkeit des Designs auf Systemebene einen maßgeblichen Faktor für den Erfolg dieses Projekts dar. Aktuell arbeiten die Autoren an zahlreichen anderen gemeinschaftlichen Mixed-Signal-Projekten und verwenden dabei den gleichen Systemebenen-Ansatz.

Über die Autoren:

Prof. Dr. L. H. Corporales ist Institutsdirektor, Dr. S. Patón Álvarez ist Dozentin, beide im Departamento de Tecnologia Electronica der Universidad Carlos III, Dietmar Sträussnigg arbeitet bei Infineon Technologies und ist nebenberuflicher Lektor an der Fachhochschule Kärnten.