Dynamikbereich eines A/D-Wandlers optimieren

Fortsetzung des Artikels von Teil 2

Dynamikbereich eines A/D-Wandlers optimieren

Gleichung (1) liefert einen groben Schätzwert, welcher Takt-Jitter für eine bestimmte Eingangsfrequenz tolerabel ist. Häufig ist es jedoch sinnvoller, den Zusammenhang zwischen Jitter und SNR zu untersuchen. Welcher SNR bei gegebenem Jitter maximal zu erreichen ist, lässt sich mit Gleichung (2) bestimmen. Durch Umstellen dieser Gleichung wiederum kann man ermitteln, welche Jitter-Performance zur Einhaltung eines bestimmten SNR erforderlich ist (Gleichung (3)). Bei einem SNR = 100 dB ergibt sich für eine analoge Eingangsfrequenz von 50 MHz ein maximal zulässiger Takt-Jitter von 32 fs.

Lässt sich so ein Wert überhaupt realisieren? Angenommen, ein solcher Jitter wäre realistisch, welche Auflösung müsste der Wandler haben, um 100 dB SNR zu erreichen? Bei einem idealen A/D-Wandler wird der Zusammenhang zwischen SNR und Auflösung durch die einfache Formel (4) ausgedrückt. Darin steht n für die Auflösung des ADCs. Für einen SNR von 100 dB ist demnach eine effektive Anzahl von Bits (ENOB) von 16,32 nötig.

Jobangebote+ passend zum Thema

Saubere Taktquelle ist wichtig

Dies ließe sich theoretisch mit einem 18-Bit-ADC erreichen, doch gibt es auf dem Markt keine solchen Bausteine mit Abtastraten über 100 MSample/s. Deshalb wollen wir jetzt Methoden untersuchen, wie sich die SNR-Spezifikation mit einem auf dem Markt verfügbaren 14-Bit-Wandler, dem »ADC14DS105« von National Semiconductor, erfüllen lässt. Dieser 14-Bit-Dual-ADC erreicht 105 MSample/s und eine FPBW von 1 GHz und ist mit serialisierten LVDS-Ausgängen ausgestattet. Bei 70 MHz Eingangsfrequenz erzielt er einen typischen SNR von 72,5 dB und einen SFDR von 86 dB.

Wie bereits erwähnt, sind Taktquellen mit extrem guter Jitter-Performance die Voraussetzung für einen hohen SNR-Wert. Welches ist die jitterärmste Taktquelle, die für eine Leiterplatte in Frage kommt? Zur Durchführung präziser Messungen stehen den Entwicklern in der Regel leistungsfähige Signalgeneratoren und anderes anspruchsvolles Equipment zur Verfügung. Leistungsfähige Signalgeneratoren sind, abhängig von ihrem Frequenzbereich und ihren Eigenschaften in Bezug auf Phasenrauschen und Jitter, zu Preisen ab 10 000 Euro bis 50 000 Euro zu haben. Doch selbst die leistungsfähigsten Geräte setzen eine gute Bandpassfilterung des Ausgangssignals voraus, um ein gutes Oberwellenverhalten erzielen zu können. Eigene Jitter-Messungen mit einem leistungsfähigen Signalgenerator und einem neunpoligen Bandpassfilter (50 MHz bis 500 MHz) ergaben einen Jitter im Bereich von 60 fs.

Für die Produktion ist also eine Taktquelle zu entwickeln, die einen geringen Jitter aufweist und zugleich kosteneffektiv und praktikabel ist. Es gibt Einfrequenz-Quarze mit ausgezeichneter Stabilität und hervorragendem Timing-Jitter. Einen hohen Bekanntheitsgrad haben Produkte der Firma Wenzel, die zwar mit über 1000 Euro nicht gerade billig sind, dafür aber einen Timing-Jitter im Bereich von 50 fs bis 60 fs bieten. Im Interesse optimaler Performance ist auch die Verwendung eines schmalbandigen Bandpassfilters empfehlenswert.

Im Labor kommen für diesen Zweck meist speziell angefertigte Filter mit fester oder variabler Frequenz zum Einsatz, die mehrere hundert Euro kosten. Für die Produktion muss selbstverständlich ein hochwertigeres Filter aus diskreten Bauelementen aufgebaut werden. Designs dieser Art sind alles andere als trivial, speziell wenn Filter von mehr als dritter oder vierter Ordnung benötigt werden. Dabei sind auch die Effekte von Signaldämpfung und Phasenlaufzeit zu berücksichtigen. Hochwertige Bauelemente wie jene von Wenzel geben außerdem ein Single-Ended-Signal aus, das vor der Weiterleitung an den ADC in ein differenzielles Signal umzuwandeln ist. Sollte dabei zusätzlicher Jitter entstehen, muss der Entwickler diesen im Gesamt-Jitterbudget natürlich mit einkalkulieren. Nicht unerwähnt bleiben darf die Tatsache, dass Quarze aufgrund ihrer fehlenden Abstimmbarkeit eher unflexibel sind.

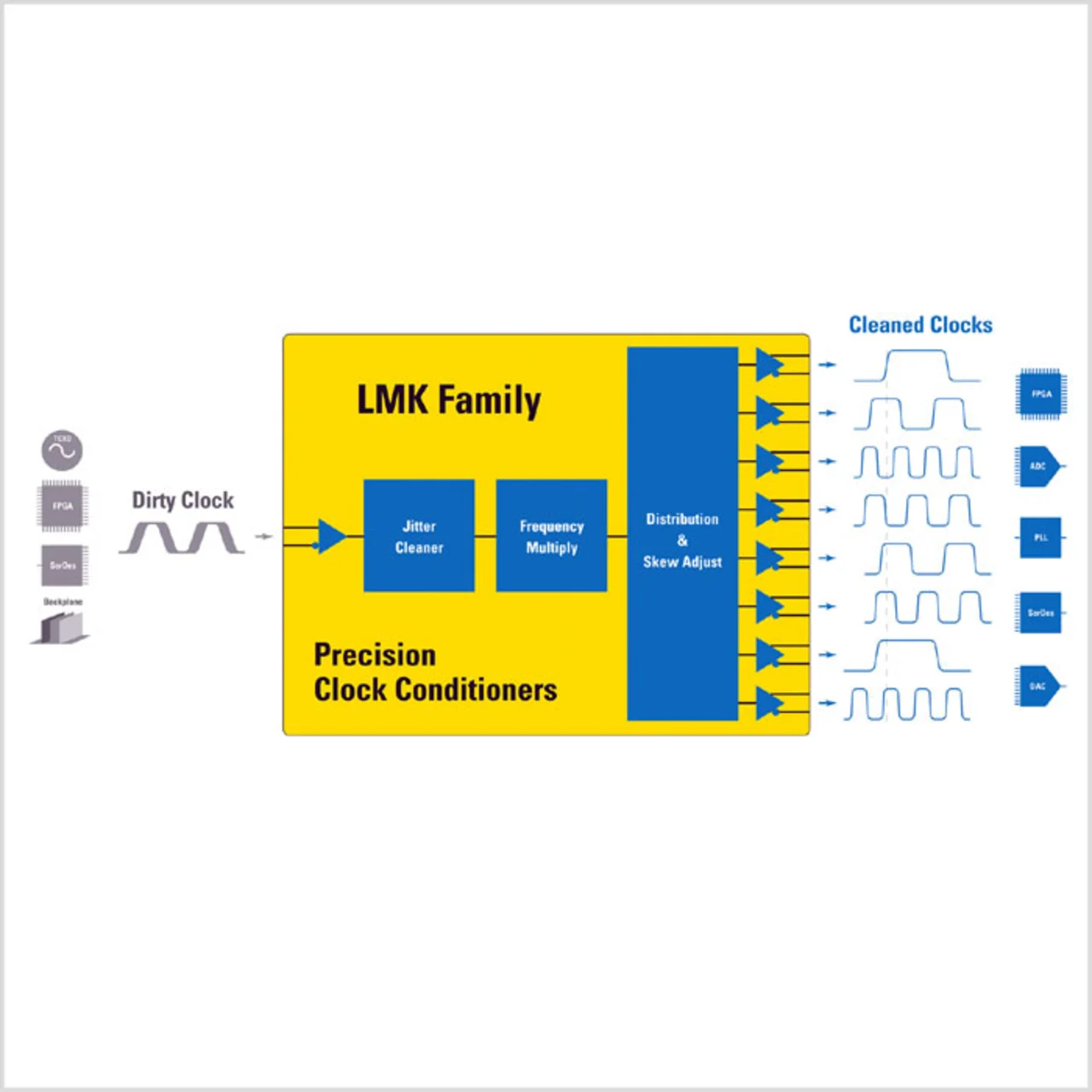

Welche übrigen Alternativen existieren hinsichtlich der Taktquellen? Als Systemtaktquelle wesentlich besser geeignet ist eine Lösung auf der Basis eines Frequenzsynthesizer-Chips. Derzeit werden Bausteine mit einem Timing-Jitter von 200 fs angeboten, wie zum Beispiel die Familien »LMK02000« und »LMK03000« von National (Bild 2, [1]).

Takt aufbereiten

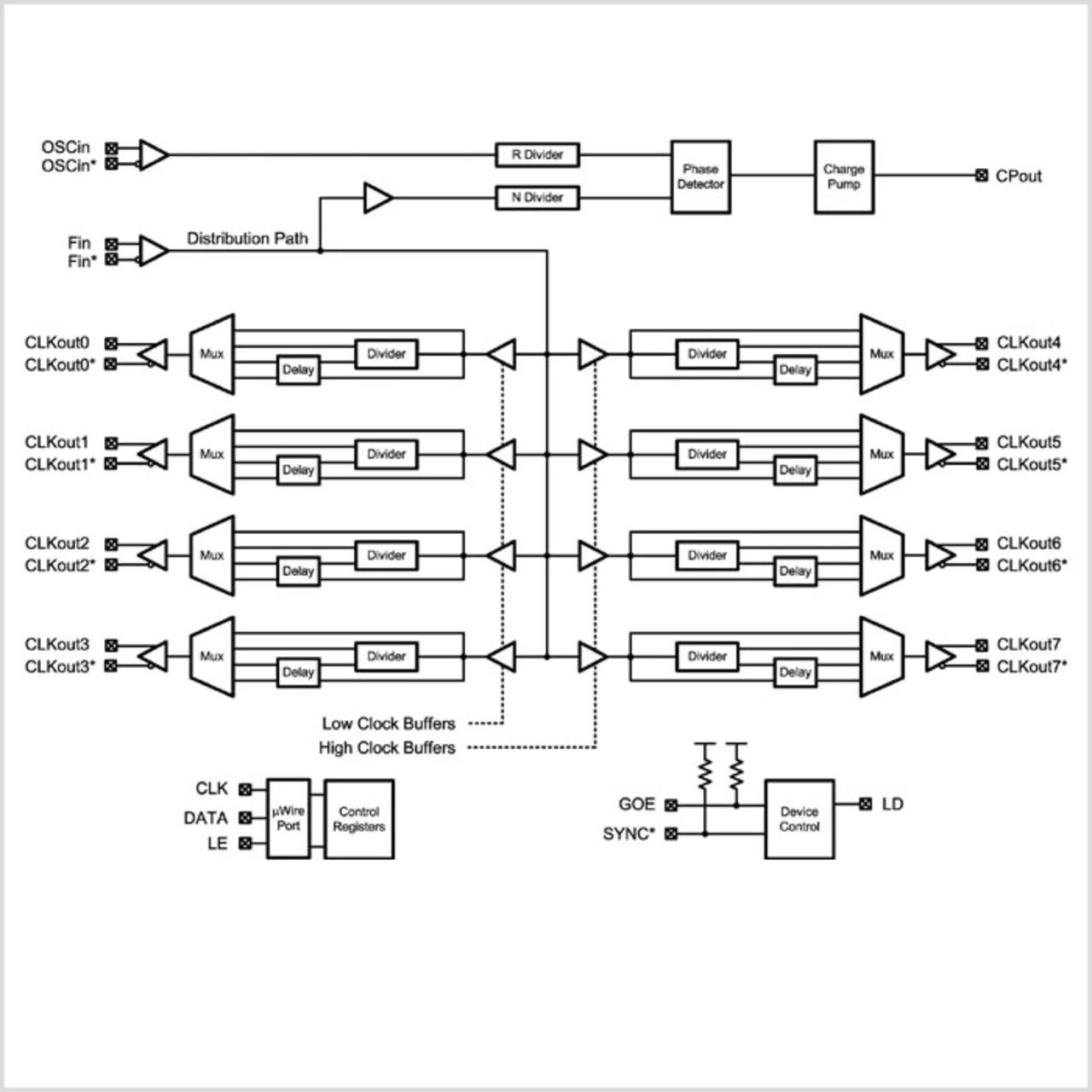

Die Bausteine der LMK03000X-Reihe können Jitter entfernen, das Signal aufbereiten und den Referenztakt multiplizieren und verteilen. Die Chips enthaltendazu einen spannungsgesteuerten Oszillator (Voltage Controlled Oscillator, VCO), eine leistungsfähige Integer-N-PLL-Stufe (Phase Locked Loop), ein teilweise integriertes Schleifenfilter sowie drei LVDS- und fünf LVPECL-Taktverteilungs-Ausgänge. Optional ist der VCO-Ausgang am Fout-Pin herausgeführt. Intern wird der VCO-Ausgang einem Eingangsteiler zugeführt, um die verschiedenen Taktverteilungsblöcke anzusteuern.

Jeder Taktverteilungsblock besteht aus einem programmierbaren Teiler, einer Schaltung zur Phasensynchronisation, einem programmierbaren Verzögerungsglied, einem Taktausgangs-Multiplexer und einem LVDS- oder LVPECL-Ausgangspuffer. Damit ist es möglich, mehrere in ganzzahligem Verhältnis stehende, phasenangepasste Kopien des Referenztakts an acht Systemkomponenten zu verteilen. Ein Beispiel zeigt Bild 3.

In Applikationen, in denen es um das Entfernen von Jitter geht, richtet der Entwickler den Synthesizer so ein, dass er eine feste Frequenz erzeugt. Die Schleifenbandbreite stellt er auf einen extrem kleinen Wert von typisch weniger als 10 Hz ein, um etwaiges Phasenrauschen des Referenztakts herausfiltern zu können. In dieser Konfiguration dominiert daher das Phasenrauschen des VCOs. Mit einem externen VCXO (Voltage Controlled Crystal Oscillator) ist ein Jitter von 200 ps realistisch.

Die Jitter-Spezifikation des LMK03000 von 200 fs setzt dem SNR eine Grenze von 84 dB – ein Wert, der theoretisch mit einem idealen 14-Bit-Wandler zu erzielen ist (siehe Gleichung (1)). In der Praxis jedoch kommen 14-Bit-ADCs bestenfalls auf 72 dB bis 74 dB, was auf verschiedene Rauschquellen und Prozessfaktoren zurückzuführen ist. Doch selbst wenn die 200 fs der wichtigste einschränkende Faktor sind, fehlen noch 16 dB bis zum angestrebten SNR-Wert. Was nun?

- Dynamikbereich eines A/D-Wandlers optimieren

- Einfluss des Takt-Jitters

- Dynamikbereich eines A/D-Wandlers optimieren

- Dynamikbereich eines A/D-Wandlers optimieren