Dynamikbereich eines A/D-Wandlers optimieren

Fortsetzung des Artikels von Teil 1

Einfluss des Takt-Jitters

Angenommen, es sei ein Wandlersystem zu entwickeln, das über eine Bandbreite von 50 MHz hinweg einen Signal/Rauschabstand von 100 dB erreicht. Eine solche Vorgabe kann beispielsweise beim Design eines Funk-Transceivers oder eines Spektrumanalysators gestellt sein. Wie lässt sich diese Forderung erfüllen, und welches sind die wichtigsten Herausforderungen? Welche Auflösung muss der Wandler haben, und welche Faktoren beeinträchtigen das Rauschverhalten am stärksten?

Unabhängig von der Auflösung des verwendeten Datenwandlers begrenzt in erster Linie der Jitter der Taktquelle den Signal/Rauschabstand. Was den SNR betrifft, legt ein 14- oder 16-Bit-ADC kein besseres Verhalten an den Tag als ein 12-Bit-Wandler, solange der Jitter der Taktquelle nicht hinreichend niedrig ist. Aus diesem Grund untersuchen wir nun als erstes, welchen Einfluss der Takt-Jitter auf den SNR hat.

Jobangebote+ passend zum Thema

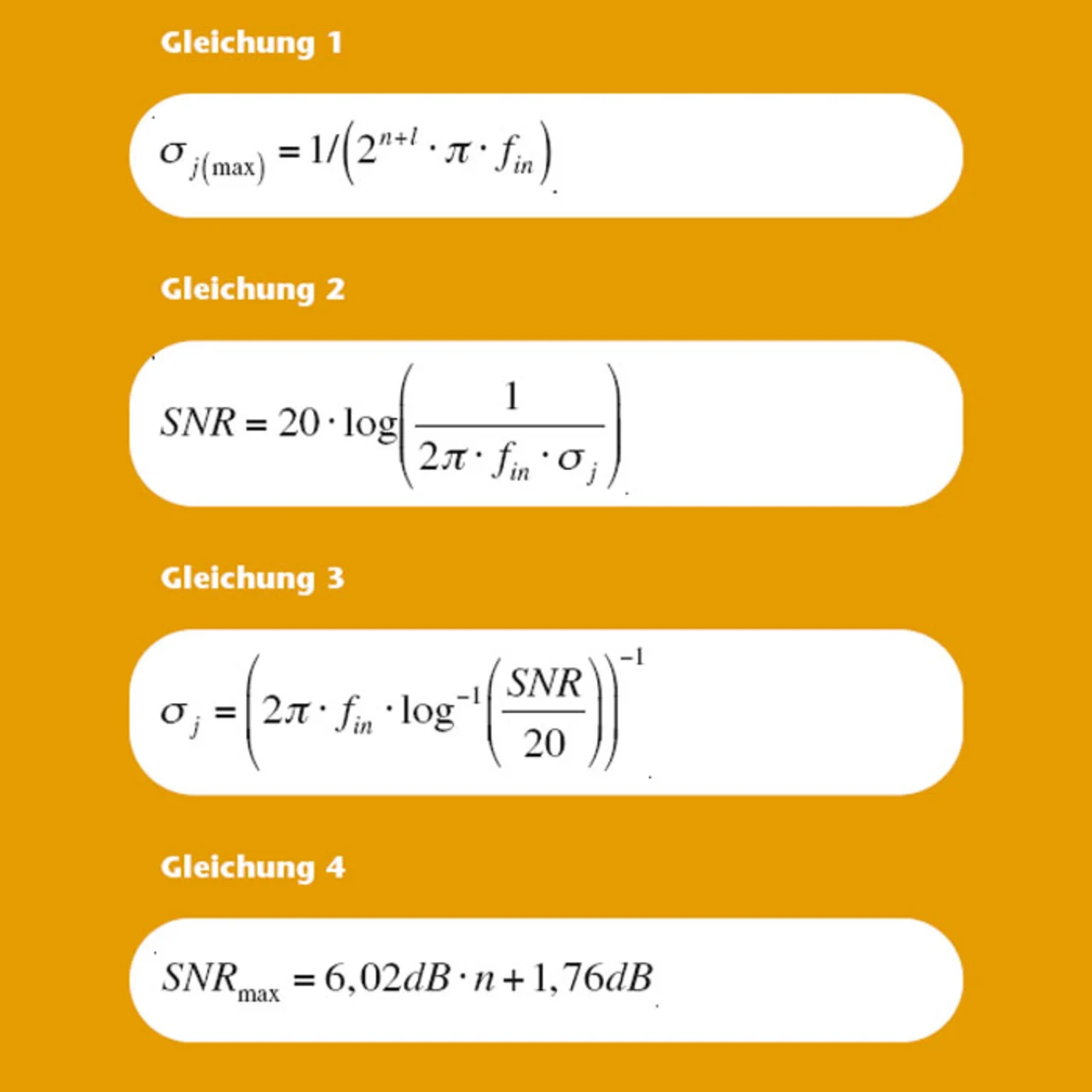

Die richtige Taktung ist im Zusammenhang mit Datenwandlern ein häufig diskutiertes Thema. Im Prinzip kann man einen ADC als einen Baustein mit zwei Eingängen (Signal und Takt) betrachten, die beide mit größter Sorgfalt zu behandeln sind. Rauschen hat an beiden Eingängen negative Auswirkungen auf die Gesamtperformance. Die gängigste Formel zum Berechnen des maximal zulässigen Takt-Jitters σj(max) für einen Wandler mit n Bit Auflösung ist in Gleichung (1) wiedergegeben. Die Formel geht davon aus, dass ein n-Bit-Datenwandler auch einen ENOB-Wert von n hat. Sie ergibt den maximal zulässigen Jitter für ein Rauschen von 1/2 LSB. Im Wesentlichen ist der Formel zu entnehmen, dass der maximal tolerierbare Jitter eine Funktion der analogen Eingangsfrequenz (fin) und der Wandlerauflösung ist. Interessanterweise ist der berechnete Jitter unabhängig von der Frequenz des Abtasttakts. Bei gegebener Eingangsfrequenz ist der tolerierbare Jitter also stets gleich. Je höher die Frequenz des analogen Eingangssignals wird, umso höher die Anforderungen, die an das Taktsignal gestellt werden.

- Dynamikbereich eines A/D-Wandlers optimieren

- Einfluss des Takt-Jitters

- Dynamikbereich eines A/D-Wandlers optimieren

- Dynamikbereich eines A/D-Wandlers optimieren