30 neue Mikrocontroller mit ARM Cortex-M3

120-MHz-STM32-F2-Familie drückt Leistungsaufnahme

Die STM32-F2-MCUs sind nicht die ersten ARM-Cortex-M3-basierenden Produkte auf dem Markt, die bis zu 120 MHz getaktet werden können. Dank des aus dem Automotive-Geschäft übernommenen 90-nm-Fertigungsprozesses und eines trickreichen Flash-Speicher-Betriebs werden allerdings neue Maßstäbe bei der Leistungsaufnahme gesetzt.

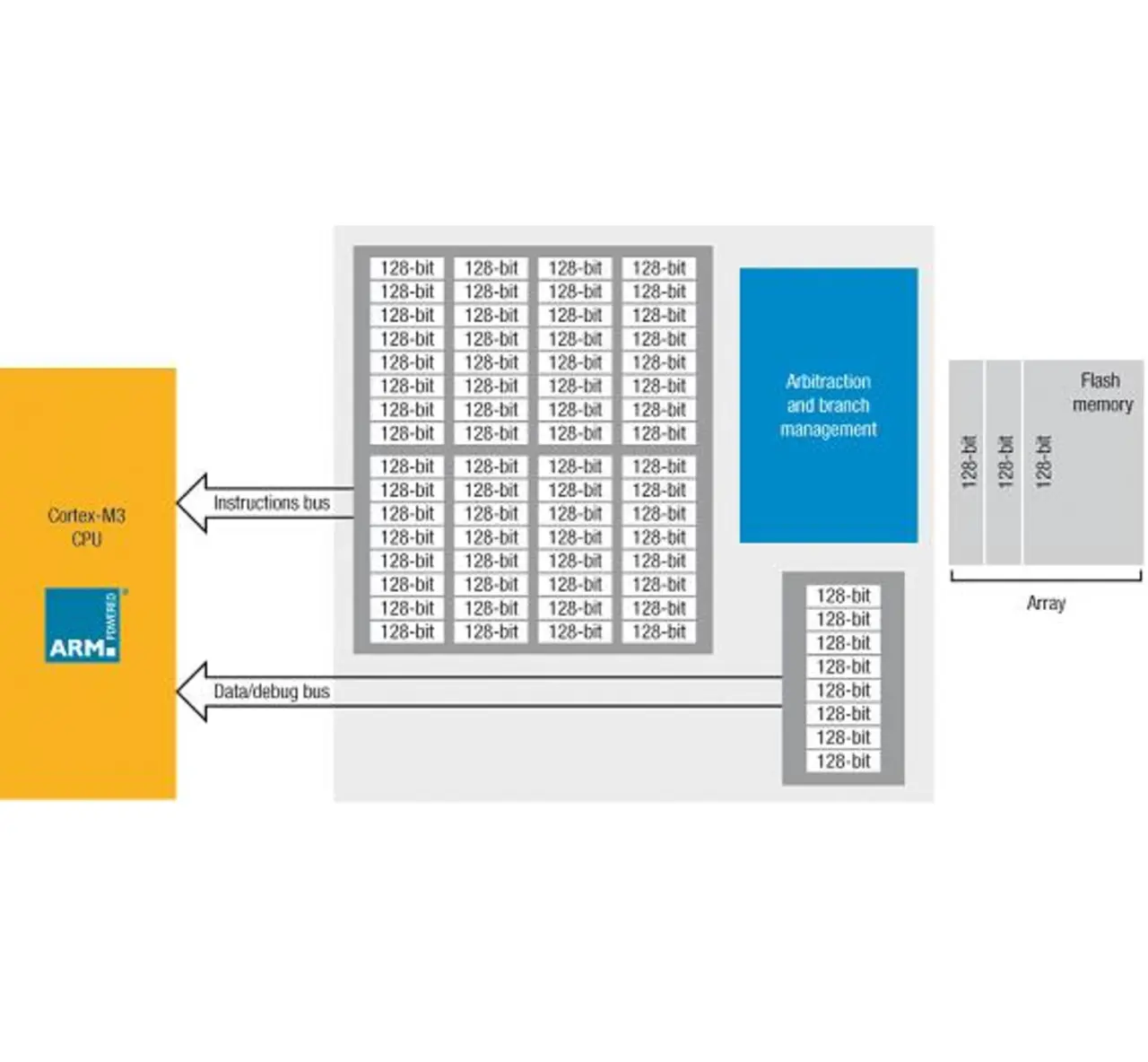

Um Energie und Kosten zu sparen und ein günstiges EMC-Verhalten zu erzielen, bietet sich bei MCUs generell der Einsatz von langsamen Flash_Speicher an. Das Problem besteht dann darin, dass bei schnellen Core-Frequenzen Wait-States generiert werden, weil der Code nicht schnell genug gelesen werden kann. ST Microelectronics hat dafür einen Adaptive-Real-Time-Memory-Accelerator (ART) entwickelt (Bild), der es ermöglicht, einen nur mit 30 MHz betriebenen Flash-Speicher einzusetzen und trotzdem Null Wait-States zu ermöglichen. Wie geht das?

Bei eines Busbreite von 128 bit werden gleichzeitig 4-8 Thumb-Befehle in einen Zwischenspeicher, der 8 Blöcke mit jeweils acht 128-bit-Einträgen enthält, eingelesen. Bei linearem Code handelt es sich daher „nur“ um eine einfache Prefetch-Einheit. Bei Sprüngen und bedingten Verzweigungen sowie beim Aufruf von Interrupt-Service-Routinen werden die Befehle ab der Zieladresse eingelesen, so dass der Code aus dem schnellen RAM ohne Wartezyklen abgearbeitet werden kann. Bei der Architektur des Beschleunigers handelt es sich um eine LRU-Architektur (Least recently used), d.h. die am häufigsten benutzen Sprungziele bleiben im Zwischenspeicher, die am wenigsten benutzten werden durch neue Sprungziele ersetzt. Ein Sprungziel wird in den Cache aufgenommen, sobald es das erste Mal angesprungen wird, und dann entsprechend der LRU-Regel im Cache gehalten.

Die STM32-F-2-MCUs kommen, wenn sie ihren Programmcode mit 120 MHz aus dem Flash-Speicher verarbeiten, auf eine Rechenleistung von 150 DMIPS. Dies ist die maximale Verarbeitungsleistung, die ein Cortex-M3-Prozessor bei dieser Taktfrequenz überhaupt erreichen kann. Bei dem von der EEMBC entwickelten Coremark-Benchmark schlägt die MCU mit 1,905 CoreMark/MHz die Konkurrenz u.a. von NXP (Der LPC1768 bei 100 MHz erreicht 1,753 CoreMark/MHz, für den LPC1769 mit 120 MHz liegen keine Werte vor, er dürfte jedoch auf Grund der identischen Architektur nicht höher sein) und Texas Instruments (Stellaris mit 80 MHz erreicht 1,595 CoreMark/MHz).

Was jedoch noch erstaunlicher sind, sind die Daten für die Leistungsaufnahme: Die CoreMark-bestätigte dynamische Stromaufnahme beträgt bei Code-Ausführung aus dem Flash-Speicher nur 188 µA/MHz, was 22,5 mA bei 120 MHz entspricht. Zum Vergleich: Der LPC1769 von NXP nimmt bei 120 MHz unter identischen Bedingungen (Peripherie abgeschaltet) 67 mA auf. Dieses Ergebnis wird durch den langsamen Flash-Speicher und die durch den ACT reduzierte Anzahl der Flash-Zugriffe ermöglicht.

Interessant ist auch der Standby-Modus, bei dem der komplette Chip bis auf die Echtzeituhr abgeschaltet werden kann und nur noch weniger als 1 µA aufgenommen wird. Damit die Status-Informationen nicht verloren gehen, hat ST einen 4 Kbyte großen SRAM-Speicher implementiert, der ebenfalls mit weniger als 1 µA auskommt, d.h. zusammen kommt der STM32F2 mit weniger als 2 µA aus.

Auch die Peripherie wurde im Vergleich zur bekannten STM32-F1-Familie weiterentwickelt: So wurde nicht nur die Abtastrate der A/D-Wandler von 1 MSPS auf 2 MSPS angehoben, die drei Wandler können auch zusammen um jeweils 120° phasenverschoben im Interleave-Modus betrieben werden, der dann eine Abtastrate von 6 MSPS erlaubt. Der Durchsatz der SPI-Schnittstellen wurde von 18 auf 30 Mbit/s angehoben und der der 6 UARTS von 4,5 auf 7,5 Mbit/s.

Weiterhin gibt es I2S, USB (mit PLL- und Datensynchronisations-Konzepten), 528 Byte OTP-Speicher (One-Time-Programmable) zum Ablegen kritischer Daten (z. B. Ethernet-MAC-Adressen oder Chiffrierschlüssel), eine Parallel-Schnittstelle (8 bis 14 bit) für einen CMOS-Bildsensor mit einer Bandbreite von bis zu 48 Mbyte/s bei 48 MHz, Ethernet MAC 10/100 mit IEEE1588 PTP-Hardware-Unterstützung, zwei CAN 2.0B aktiv, eine externe Speicherschnittstelle mit bis zu 60 MHz und Unterstützung für Compact-Flash, SRAM, PSRAM, NOR und NAND sowie LCD.

Weiterhin gibt auch noch zwei 16-bit-PWM-Motorsteuerungs-Timer, 12 Universal-Timer, zwei 32-bit-Timer und einen 12-bit-D/A-Wandler. Für die Datenverschlüsselung implementierte ST einen Crypto/Hash-Prozessor und einen analogen, echten Zufallszahlen-Generator, der seine Zufallszahlen z.B. aus analogen Werten wie Rauschen generiert. Der Verschlüsselungs-Block arbeitet mit mit Hardwarebeschleunigung für AES 128, 192, 256, Triple DES und HASH (MD5, SHA-1).

Die Ziel-Applikationen sind Consumer‑ und Mobil-Anwendungen, begünstigt durch die hohe Rechenleistung und die Spannungsversorgung von 1,65 bis 3,6 V (intern wird die Core-Spannung mittels eines Linear-Reglers auf 1,2 V abgesenkt)sowie das platzsparende WLCSP64-Gehäuse. Auch für Industrie- und Medizintechnik-Applikationen scheint die neue MCU-Familie dank der Konnektivitäts-Peripherie und der Verschlüsselungs-Funktionen sowie dem großen Flash- und SRAM-Speicher geeigent zu sein.

Mit den über 30 neuen Bausteinen der F-2-Serie wächst die Gesamtzahl der STM32-Mikrocontroller auf insgesamt 180 pin‑ und softwarekompatible Produkte, die einen einheitlichen Pool an Peripheriefunktionen besitzen. Allgemein verfügbar werden die Produkte ab dem ersten Quartal 2011. Die Preisskala der STM32-F-2-Serie beginnt bei 3,18 Dollar für den STM32F205RBT6 mit 128 Kbyte Flash und 64 Kbyte RAM im LQFP64-Gehäuse (ab 10.000 Stück).