PCI/104-Express

Fortschritte bei kleinen Formfaktoren

Fortsetzung des Artikels von Teil 1

Prozessor, Bus und Speicher ergeben „Prozessor-Footprint“

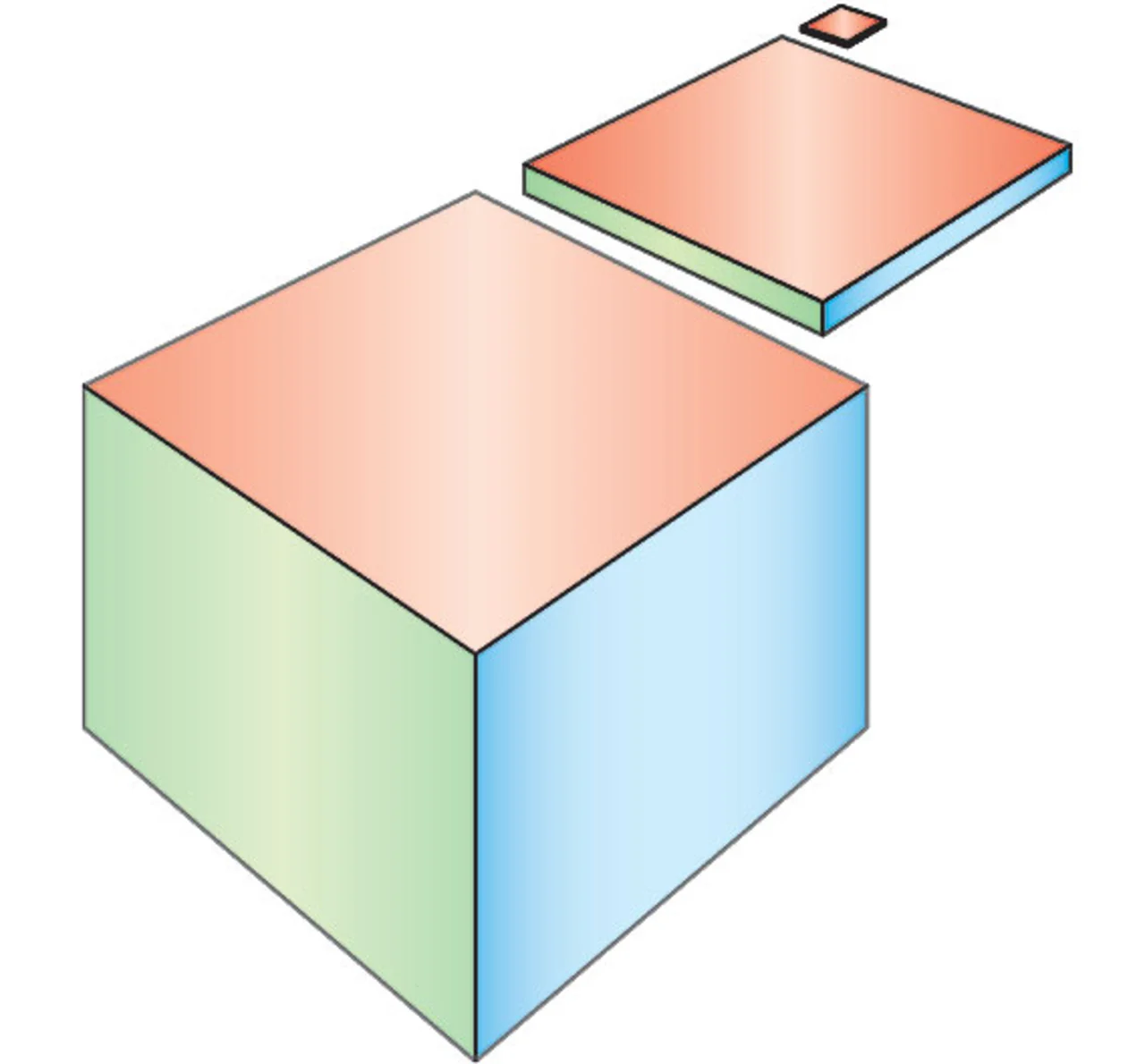

Aus der Zusammensetzung von freien Prozessor- und Speicherressourcen ergibt sich der so genannte „Prozessor-Footprint“. Hiermit kann die Bandbreite des I/O-Busses grafisch in der dritten Dimension dargestellt werden. Die I/O-Busbandbreite ist vertikal (y-Achse) und die Prozessorgeschwindigkeit horizontal (x-Achse) dargestellt. Der Arbeitsspeicher wird auf der diagonalen z-Achse abgebildet. Aus diesen Werten ergeben sich die in Bild 1 gezeigten grafischen Umsetzungen der gesamten Rechenvolumina der Busse ISA, PCI und PCI-Express.

Die kleinste Darstellung ist eine 133-MHz-Elan-SC520-CPU mit ISA-Bus und 128 Mbyte SDRAM. Die mittlere Darstellung zeigt einen 1,8-GHz-Pentium-M 745 mit PCI-Bus und 1 Gbyte DDR-RAM. Der große Würfel verkörpert einen Core-2-Duo SP9300 mit 2,26 GHz, PCI-Express-Anbindung und 4 Gbyte DDR-3-RAM. Alle gewählten CPUs können einen oder mehrere Befehle pro Taktzyklus ausführen, weshalb ihre Integer-Performance der CPU-Taktrate entspricht oder diese übertreffen kann.

Die Form des PCI-Express-Berechnungsvolumens ist eher würfelförmig als flach. Breite und Tiefe entsprechen den anderen beiden Volumina. Dies ist ein Anzeichen dafür, dass die Kombination von Bus, CPU und Speicher das Bus-Maximum nicht erreicht hat. Bei PCI-Express muss die Speicherbandbreite die Busbandbreite um das Vierfache überschreiten, bevor das Speichern und Weiterleiten im Vollduplex-Betrieb die Busauslastung erreicht. Die Steigerung der Speicherbandbreite, die unter Umständen einen breiteren und schnelleren Kanal erfordert, ist eine der grundlegenden architektonischen Herausforderungen, die gelöst werden muss, um PCI-Express voll auszulasten. Der jetzige PCI-Express-Bus wird deshalb wohl noch für mehrere „Moore-Zyklen“ erhalten bleiben.

Die technischen Beschränkungen der PCI/104-Express-Implementierung halten die Datenrate pro Lane auf dem derzeitigen Niveau. Die höhere Bandbreite der zweiten PCI-Express-Generation wird die Zuverlässigkeit heutiger Systeme weiter ausdehnen. Für die Entwicklung des physikalischen PC/104-Formfaktors ist es entscheidend zu wissen, wann die nächste Verbindungslösung eingesetzt wird.

Die Kuben in Bild 1 stellen Mooresche Volumen (Mv) dar. Diese sind das Produkt von CPU-Taktfrequenz (MHz), Speichergröße (Mbyte) und Busbandbreite (Mbyte/s). Ein MMv hat die impliziten Einheiten von MHz · Mbyte2/s. Dabei sollte beachtet werden, dass ein System mit 1 MHz bei 1 Mbyte/s und 1 Mbyte Speicher wie der IBM PC/XT einen Wert von 1 MMv haben würde. Die Busgeschwindigkeiten zur Basis 10 wurden in MiB (1024 × 1024) konvertiert, so dass ein korrektes Mooresches Volumen berechnet wird. Dies bewahrt die Größenordnung, die durch die Einheit Hz · B2/s impliziert ist.

Jobangebote+ passend zum Thema

| CPU | MHz | BuS | Mbyte/s | Mbyte RAM | MMv | (MMv)1/3 | log2(MMv) |

|---|---|---|---|---|---|---|---|

| SC520 |

133 | ISA |

12,72 | 128 | 216460,16 | 60,04 | 17,72 |

| PM745 | 1800 | PCI | 127,16 | 1024 | 234374997,66 | 616,55 | 27,8 |

| SP9300 | 2260 | PCIe | 4768,37 | 4096 | 88281250000 | 4452,69 | 36,36 |

Tabelle 1: Nummerische Darstellung des Bildes. Die Kubikwurzel-Spalte des PCIe-System zeigt, dass es noch viel Raum gibt, bevor die Sättigung von ca. 6200 erreicht wird.

Tabelle 1 zeigt die Dimensionen der drei Kuben. Die ersten beiden Zeilen enthalten die gesättigten Volumina (letzte zwei Spalten). Hieraus geht hervor, dass es einen Faktor von ca. 10 in der Kubikwurzel und einen Anstieg von 10 im Base-2-Logarithmus der Mooreschen Volumendarstellung gibt. In der Spalte für die Kubikwurzel wird die PCI-Express-Generation voraussichtlich einen Wert in der Größenordnung von 6200 erreichen und noch weiter ansteigen. Ebenso deutet die log2-Spalte darauf hin, dass bis zur Sättigung noch 1,5 Zyklen vergehen.

- Fortschritte bei kleinen Formfaktoren

- Prozessor, Bus und Speicher ergeben „Prozessor-Footprint“

- Blick in die Zukunft