Hard- und Software-Co-Design mit FPGAs #####

Fortsetzung des Artikels von Teil 2

Die Grenzen des „Self-made“-Design

In einem simplen Embedded-System mit FPGA ist es normalerweise nicht zu kompliziert, eine solche Software selbst zu schreiben. So wird z.B. für die Steuerung einer Reihe von LEDs eine binäre 8-bit Zahl in eine Adresse geschrieben. Diese Adresse steuert die physikalisch mit den LEDs verbundenen FPGA-Pins. Die Software für dieses Design manuell zu schreiben, ist nicht schwierig. Aber selbst in diesem einfachen Beispiel ist der C-Code nicht komplett portierbar, da die Adresse der LEDs durch das FPGA-Design definiert ist und ungültig werden kann, sobald sich das FPGA ändert.

Jobangebote+ passend zum Thema

In einem simplen Embedded-System mit FPGA ist es normalerweise nicht zu kompliziert, eine solche Software selbst zu schreiben. So wird z.B. für die Steuerung einer Reihe von LEDs eine binäre 8-bit Zahl in eine Adresse geschrieben. Diese Adresse steuert die physikalisch mit den LEDs verbundenen FPGA-Pins. Die Software für dieses Design manuell zu schreiben, ist nicht schwierig. Aber selbst in diesem einfachen Beispiel ist der C-Code nicht komplett portierbar, da die Adresse der LEDs durch das FPGA-Design definiert ist und ungültig werden kann, sobald sich das FPGA ändert.

- Auf der untersten Ebene müssen zunächst die Basisadresse des PS/2-Ports und der Zugriff auf die Takt- und Daten-Leitungen definiert werden.

- Auf der nächsten Ebene muss die Applikation darauf vorbereitet werden, einen Interrupt von der Tastatur zu empfangen. Der Interrupt muss korrekt abgefangen werden, um dann die Daten am PS/2-Port in Form von Frames und Scancodes zu lesen.

- Wieder eine Ebene höher werden diese Daten gesammelt und der aktuelle Scancode gespeichert (z.B. 0xC1 beim Drücken und 0xF0 0xC1 beim Loslassen der „A“-Taste).

- Auf der obersten Ebene müssen Scancode und Tastenkombinationen korrekt interpretiert werden – Drücken der Shift-Taste vor der A-Taste und Interpretation als Großbuchstabe „A“.

Diese Beschreibung ist nicht komplett, gibt aber doch einen Eindruck der Komplexität wieder, die bei einer Applikation mit einem Peripheriegerät wie einer PS/2-Tastatur auftritt.

Hardware/Software-Co-Design mit programmierbaren Bausteinen

Altium arbeitet daran, aus vielen verschiedenen Teilbereichen der Elektronikentwicklung diese enorme Komplexität herauszunehmen und einem Entwickler weiterhin die Möglichkeit zu geben, aktuelle Technologien voll auszuschöpfen. Der „intelligente Generalist“ benötigt dazu ein Werkzeug, das für die Entwicklung von kompletten Embedded-Systemen mit FPGAs und für die Realisierung der Hardware folgendes bietet:

- ein Designprozess für alle Aspekte der Entwicklung,

- ein einziges, stimmiges Modell des kompletten Designs,

- ein stimmiges Modell der verwendeten Bausteine,

- eine Design-Umgebung mit einer einheitlichen Benutzeroberfläche,

- eine Design-Datenablage.

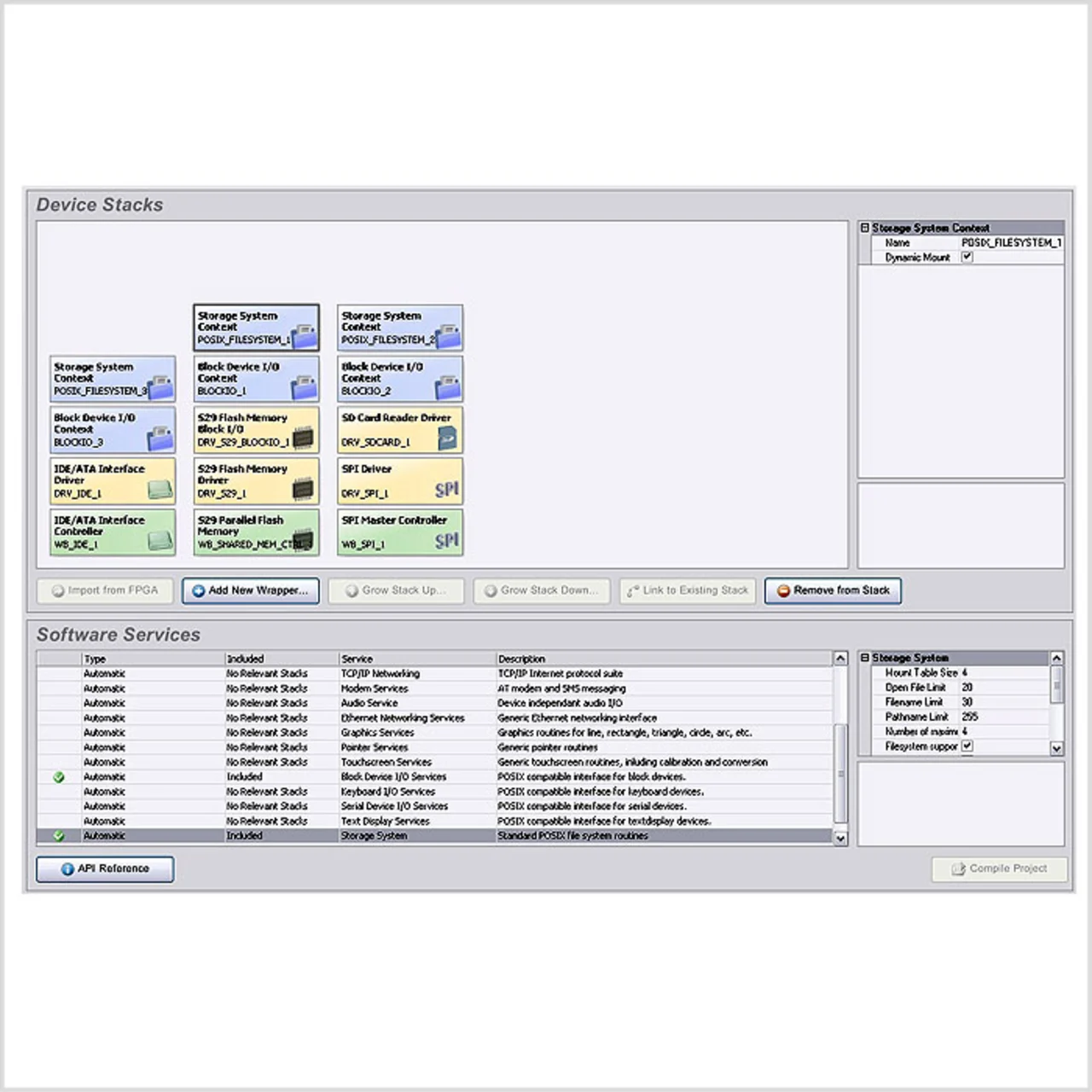

Bei der Kombination einer solchen Design-Umgebung mit einer variablen Hardware-Plattform wie dem Nano-Board von Altium kann eine Vielzahl der aufgeworfenen Fragen abgehandelt werden. Durch einen „Software Platform Builder“ wird die Entwicklung der Software vereinfacht. In einer grafischen Oberfläche wird das Projekt konfiguriert und verschiedene Software-Module werden integriert (Bild 1). Diese Module kümmern sich sowohl um die Routinen der niedrigeren Ebenen als auch um die Implementierung einer Top-Level-API. Dadurch können hardware-unabhängige Applikationen entwickelt werden, da die API zur eigentlichen Applikation selbst bei sich ändernder Peripherie identisch bleibt. So lässt sich z.B. ein generischer Kontext für ein Speicher-System aufbauen, der wahlweise auf einen parallelen S29-Flashchip oder einen SPI-Master-Controller zugreift.

Ein C-zu-Hardware-Compiler, der den Standard-C-Code der Embedded-Applikation verarbeiten kann und der wahlweise C-Routinen in Hardware überträgt, erlaubt einfaches „Durchspielen“ verschiedener Implementierungen. Eine enge Anbindung an das FPGA-Design erlaubt eine Design-Partitionierung sehr spät im Design-Prozess.

- Hard- und Software-Co-Design mit FPGAs #####

- Herausforderung Hardware-Entwicklung

- Die Grenzen des „Self-made“-Design

- Hard- und Software-Co-Design mit FPGAs

- Übersichtliche Bauteilbezeichnungen