Hard- und Software-Co-Design mit FPGAs #####

Fortsetzung des Artikels von Teil 3

Hard- und Software-Co-Design mit FPGAs

Ebenso verhält es sich mit der Anbindung an das Hardware-Design. Die bereits erwähnten Listen für das Pin-Out des FPGA sind hinfällig. Änderungen am FPGA-Pin-Out können jederzeit sowohl in der Leiterplatte (leichtere Entflechtung) als auch im FPGA-Design (geändertes Place & Route für verbessertes Timing) durchgeführt und entsprechend übertragen werden.

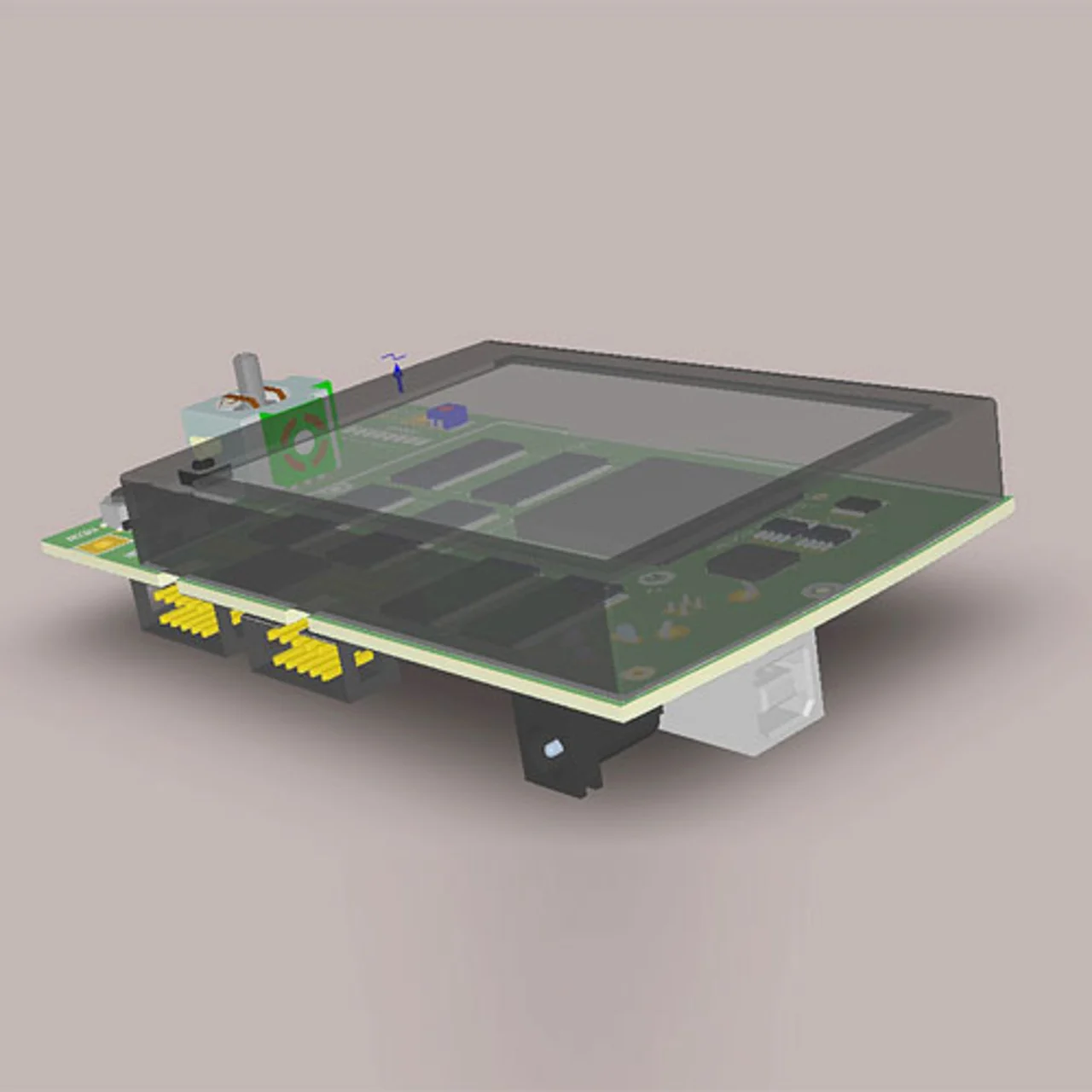

Die Leiterplattenentflechtung wird durch eine Verschmelzung mit dem generischen STEP-Format zu einer 3DErfahrung. Die Leiterplattenkontur kann über STEP-Import definiert und eine Kollisionskontrolle gegen das Gehäuse bzw. andere Komponenten durchgeführt werden. Es gibt keine zwischengeschaltete Instanz. Eine Live-Verbindung zum Gehäusemodell erzeugt sofort eine Meldung im Design-Tool, wenn sich das Gehäuse ändert.

Jobangebote+ passend zum Thema

Wiederverwenden ist mehr als Kopieren und Einfügen

Relativ häufig wird schon so etwas Ähnliches wie die Wiederverwendung von Designs praktiziert. Das Kopieren und Einfügen von Teilen existierender Designs wie Standardschaltkreise für Kommunikation oder Stromversorgungen ist ein alltäglicher Vorgang. Dabei gibt es jedoch keinerlei Integrität im kopierten Design. Während des Kopierens/ Einfügens können zahlreiche Fehler vorkommen – die Schaltung muss an die entsprechenden Bedingungen angepasst werden, so dass sie auch die üblichen Überprüfungs- und Abnahmeprozesse durchlaufen muss.

Damit die Wiederverwendung von Designs funktionieren kann, gilt es zunächst, zwei grundlegende Herausforderungen zu überwinden:

- Zunächst müssen die zu verwendenden Schaltpläne jedermann zur Verfügung stehen, gleichzeitig aber vor Änderungen geschützt werden (die Änderung eines Bauteilnamens in Projekt 1 darf keine Auswirkungen auf dieses Bauteil in Projekt 2 haben).

- Da durch den vorstehenden Punkt die zentrale Ressource nicht bearbeitet werden kann, muss die Design-Umgebung die Fähigkeit unterstützen, die Bauteilbezeichnungen in jedem neuen Design zu aktualisieren, ohne die Vorlage zu verändern.

Im Beispiel sollen Teile der Prototypen-Plattform (z.B. USB-Anschluss und Touchscreen des NanoBoard) in die kundenspezifische Leiterplatte übernommen werden. Dabei lässt sich viel Zeit sparen, wenn die benötigten Schaltungen direkt wiederverwendet werden können.

Der Device-Sheet-Ansatz

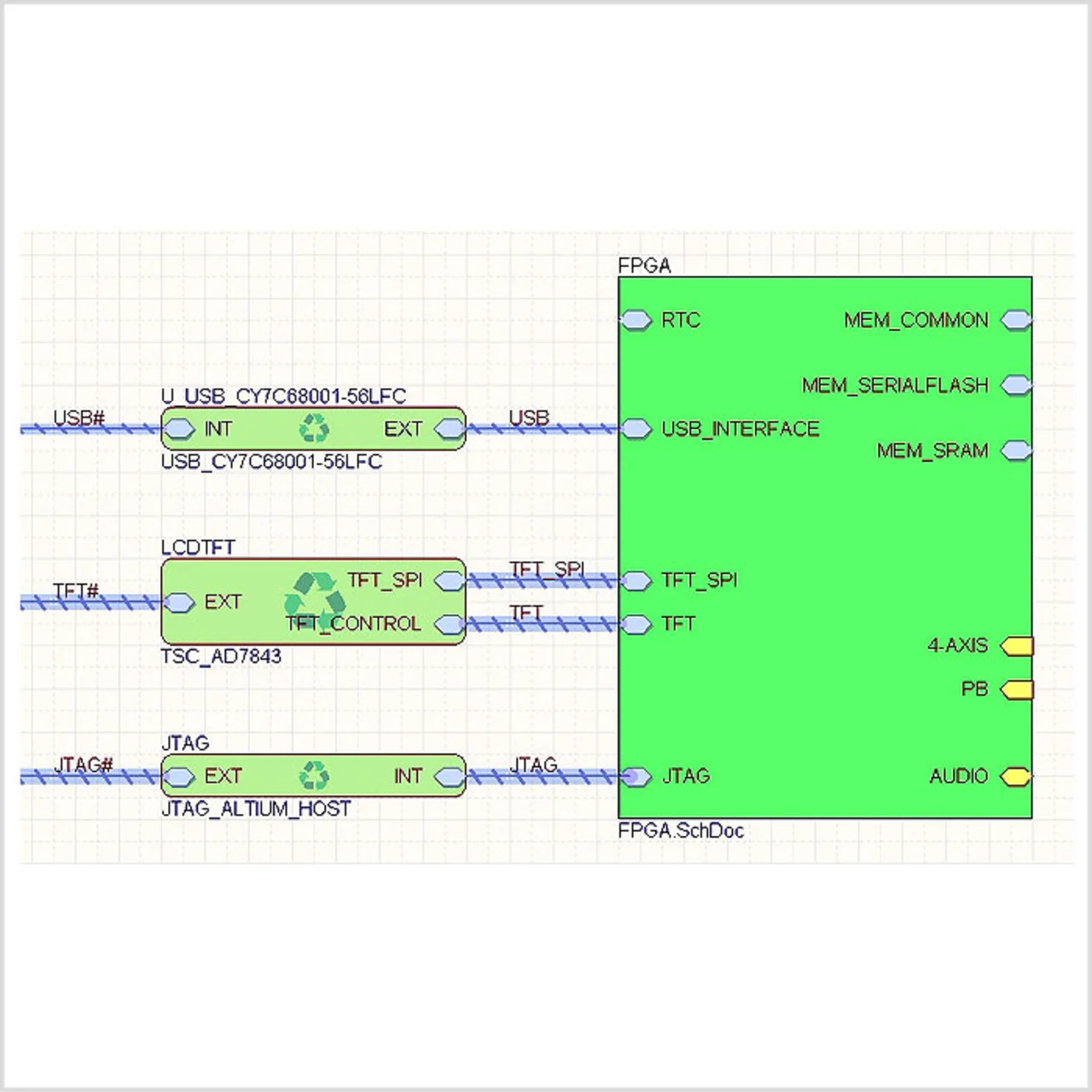

Ein Device-Sheet ist eine für spätere Wiederverwendung aufbereitete Schaltplanseite. Werden solche Device-Sheets in ein Design eingebunden, werden Sie mit einem Recyclingsymbol gekennzeichnet, und zwar sowohl im Sheet-Symbol, das auf die Schaltplanseite verweist, als auch auf der Schaltplanseite selbst (Bild 2).

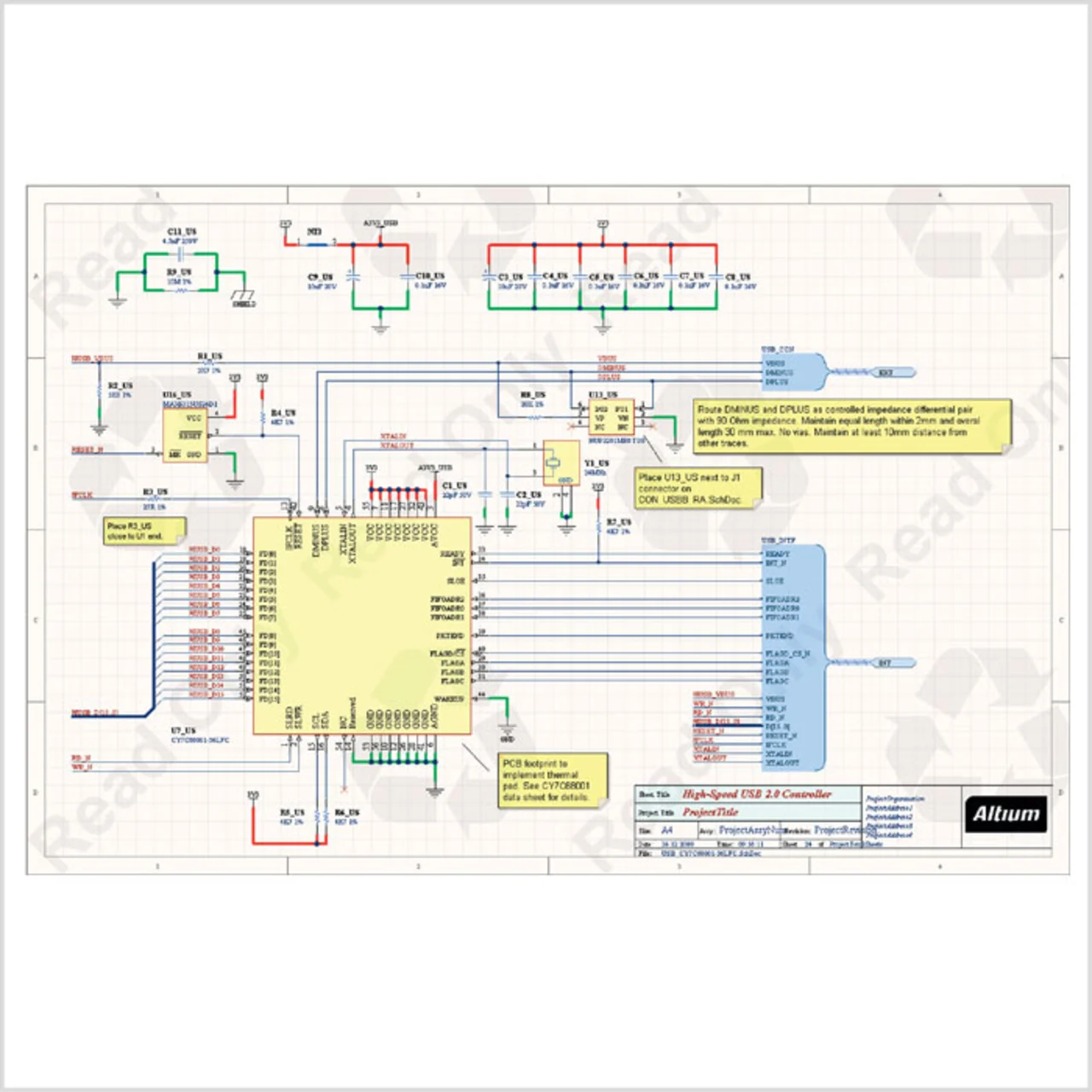

Existiert z.B. in einem Design ein USB-Port, der wiederverwendet werden kann, so wird der Schaltplan neben dem Recyclingsymbol mit einem „Wasserzeichen“ dargestellt, das ihn als „Read Only“ kennzeichnet (Bild 3). Diese Kennzeichnungen verschwinden im PDF oder im Ausdruck der Schaltplanseite. Device-Sheets lassen sich einfach aus „normalen“ Schaltplanseiten erzeugen. Dabei kann sogar eine Hierarchie nachgebildet werden, d.h., ein Device Sheet kann über mehrere Ebenen auch mehrere Schaltplanseiten enthalten. Die Device Sheets werden in einem eigenen Verzeichnis abgelegt und bilden so eine eigene Bibliothek.

Im Handumdrehen kann so z.B. die Hardware für einen USB-Anschluss und einen Touchscreen zu einem Design hinzugefügt werden. Mit dem entsprechenden Befehl können die geeigneten Device-Sheet-Symbole platziert werden. Signalbündel (Signal Harnesses) sind eine ideale Ergänzung für Device-Sheets. Sie bündeln Netze und Busse zusammen, so dass strukturelle Schaltplanblätter klar und übersichtlich bleiben.

- Hard- und Software-Co-Design mit FPGAs #####

- Herausforderung Hardware-Entwicklung

- Die Grenzen des „Self-made“-Design

- Hard- und Software-Co-Design mit FPGAs

- Übersichtliche Bauteilbezeichnungen