LabView Communications

Grafische FPGA-Entwicklung

Fortsetzung des Artikels von Teil 1

Arbeitsfluss mit LabView Communications

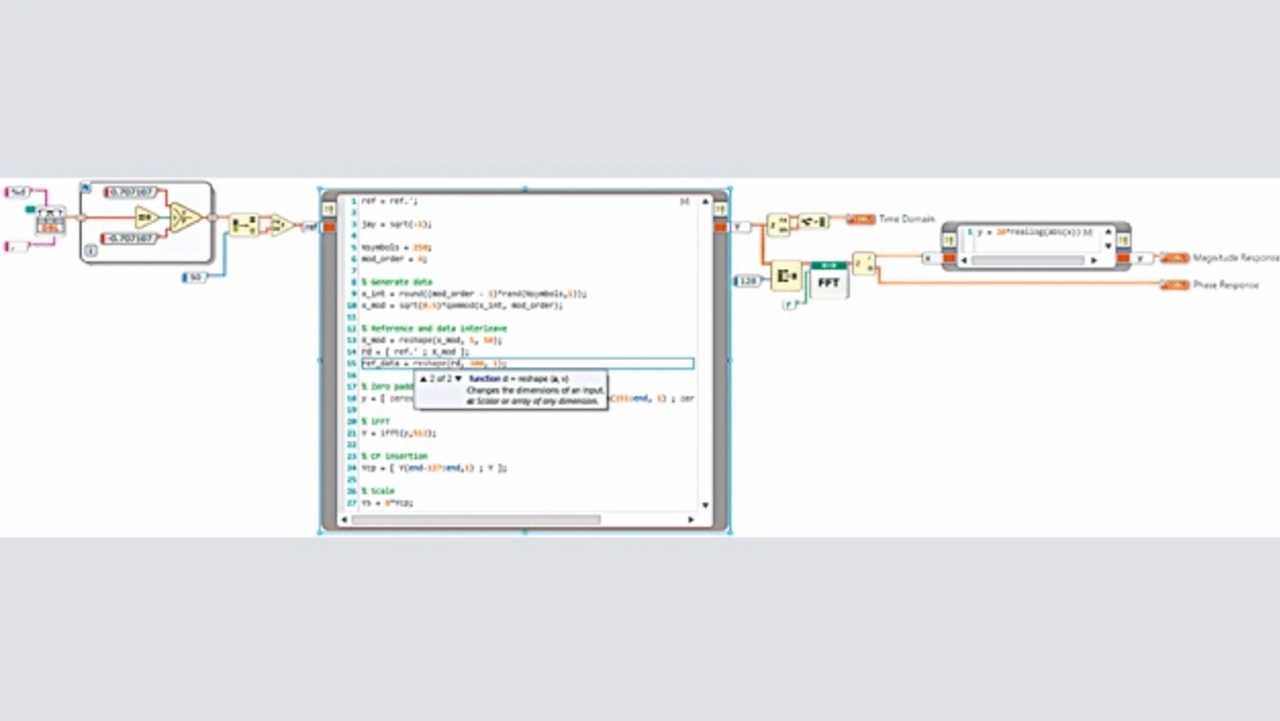

Häufig ist eine bereits vorhandene Simulation eines Systems oder Algorithmus‘ der Ausgangspunkt für den Prototypenentwurf. LabView Communications bietet auch selbst eine umfangreiche Palette von Funktionen zur Algorithmensimulation. Bereits vorhandener Matlab- oder Ansi-C-Code lässt sich einfach in ein Projekt integrieren.

Jobangebote+ passend zum Thema

Für diese Sprachen gibt es separate Integrationsknoten mit Syntaxhervorhebung und Diagnosefunktionen. Dies vereint grafischen und textbasierten Code zu einem einzigen Algorithmusentwurf. Die eigentliche Stärke von LabView Communications offenbart sich im FPGA-Design: Mit der grafischen Programmierung werden Code-FPGAs wie auf einem Host-Rechner erstellt und zu Bit-Files kompiliert. VHDL-Expertenwissen ist nicht nötig. Der Xilinx-Compiler bezieht automatisch generierte VHDL-Dateien aus dem Top-Level-Blockdiagramm des FPGA-Ziels. Damit können Algorithmenentwickler eigenen Code auch ohne Experten in die Hardware implementieren und die Vorteile echtzeitfähiger Hardwareprototypen nutzen.

Optimiertes FPGA-VI

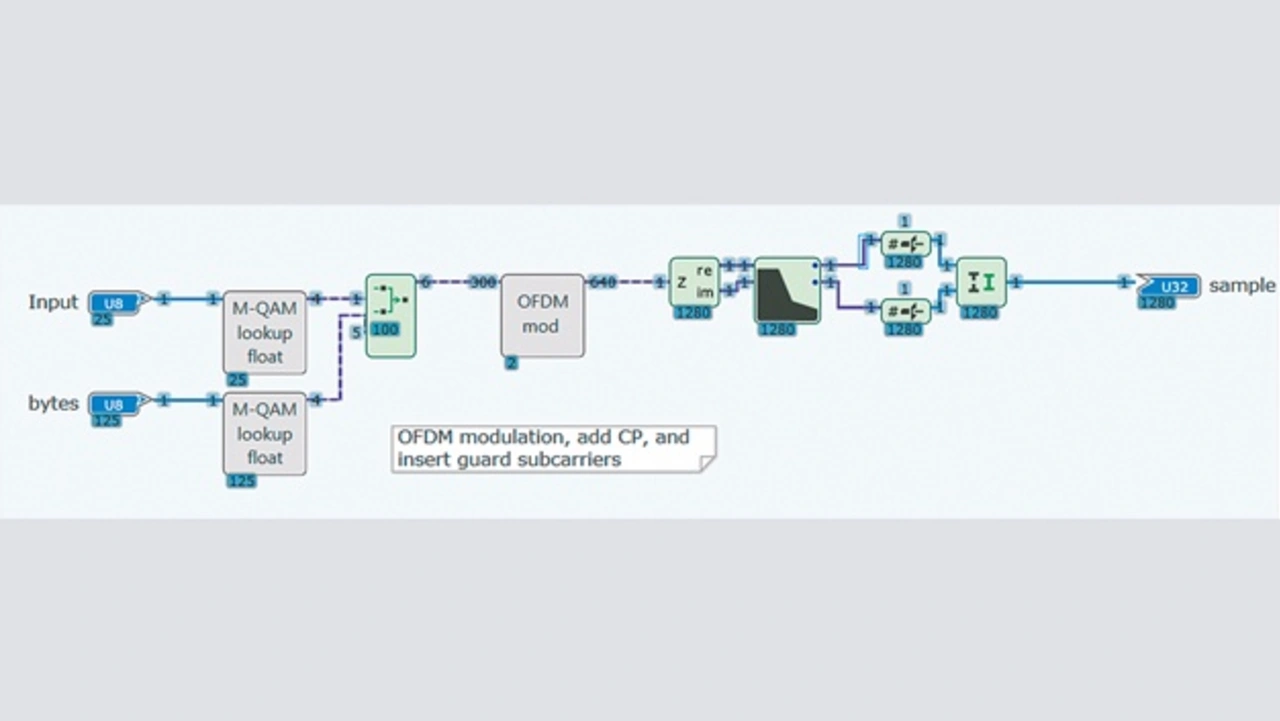

Auch für den FPGA stehen mehrere Varianten der Implementierung zur Verfügung. Eine auf dem Host in nativem Code hinterlegte Funktion wird im System Designer einfach auf das verbundene FPGA-Ziel (z. B. USRP-2952R) gezogen. Dort ist sie dann als optimiertes FPGA-VI in das FPGA-Design integriert.

FPGAs unterstützen ausschließlich Integer- und Festkomma-Arithmetik. Zur FPGA-Implementierung einer Funktion nach der Simulation auf dem Host ist daher eine Konvertierung der Fließkommadaten in Integer oder Festkomma erforderlich. Dies kann von der Entwicklungsumgebung automatisch durchgeführt werden. Die Anzahlbegrenzung für die Bits der Festkomma-Implementierung orientiert sich unter anderem am Signal/Rausch-Verhältnis.

»Multirate«-Diagramm

Eine neue Implementierung bietet das Multirate-Diagramm. Die Algorithmen werden hier ebenfalls als Sequenzen grafischer Blöcke definiert. Eine Sequenz kann normalerweise nur als Ganzes ausgeführt werden. Oftmals sind jedoch einzelne Knoten einer Kette mehrmals auszuführen, bevor ein gültiges Ergebnis am Funktionsausgang vorliegt. Eine Fourier-Transformation etwa wird so aus einem Wertearray berechnet.

Erst mit dem, den letzten Wert des Arrays verarbeitenden Taktzyklus, kann auch ein gültiges Ergebnis ausgegeben werden. Das macht Handshaking zwischen den einzelnen Knoten notwendig. Es signalisiert die Kommunikationsbereitschaft der Eingänge. Zur Zwischenspeicherung müssen »FIFOs« angelegt werden. Das Multirate-Diagramm implementiert diese Funktionalität im Hintergrund. Es abstrahiert die Berechnung von FIFO-Größen und -Durchsatz sowie das Benutzerhandshaking. Der Entwickler gibt lediglich einen Zieldurchsatz in Samples/s und die Kompilierungstaktrate des Diagramms an. Dies spart beträchtlich Entwicklungszeit ein. Multirate-Diagramme können zuerst auf dem Host-Rechner simuliert und dann ohne Änderung in den FPGA-Code integriert werden.

- Grafische FPGA-Entwicklung

- Arbeitsfluss mit LabView Communications

- Clock-Driven Logic