Hohe EMV-Hürden erfordern Technologie-Umstieg

SOI für den LIN-Bus #####

Fortsetzung des Artikels von Teil 2

SOI für den LIN-Bus

DPI-Verfahren zur Ermittlung der EMV-Festigkeit

Im Gegensatz zum Fahrzeug-Kabelbaum und – abhängig von der Leitungsführung – auch zur Leiterplatte sind die sehr kleinen Strukturen im Inneren von ICs und die Pins mit ihren kleinen Abmessungen keine effizienten Antennen für unerwünschte HF-Einstrahlung im Frequenzbereich unterhalb von 1 GHz. Die durch den Kabelbaum oder von Leiterplatten eingefangenen HFStörungen gelangen also leitungsgebunden über die Pins in das IC. Um dies im Labor nachzubilden, wurde das DPI-Verfahren entwickelt. Damit lässt sich jeder einzelne Pin eines Bauteils separat auf seine Störanfälligkeit überprüfen (Bild 1).

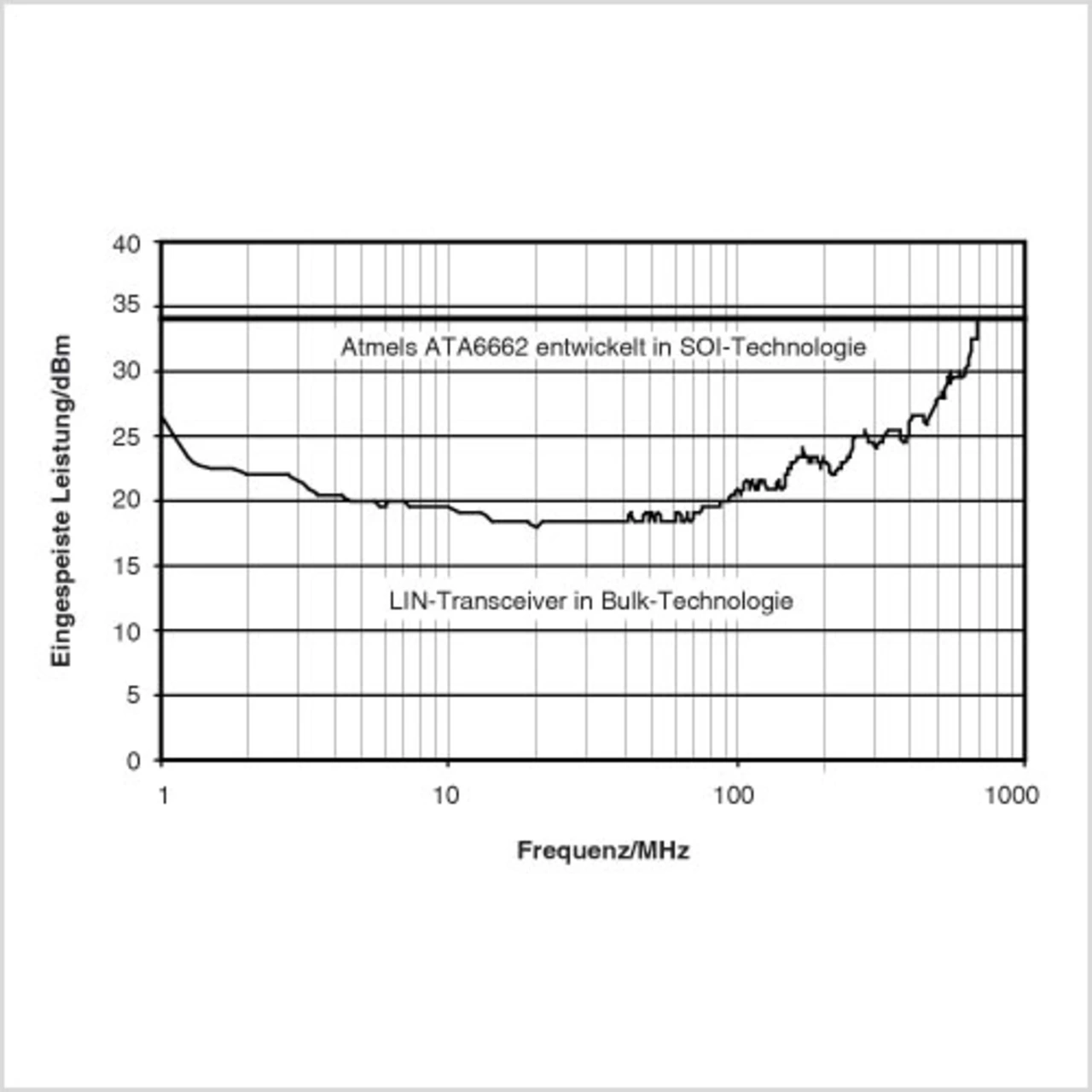

Hierzu wird ein frequenzveränderlicher HF-Generator verwendet, der eine HF-Störung erzeugt, die mit einem nachgeschalteten HF-Verstärker verstärkt wird. Hinter dem Verstärker wird ein Richtkoppler eingefügt, um die in den LIN-Bus eingespeiste Vorwärtsleistung zu messen. Um das Verhalten verschiedener ICs miteinander reproduzierbar vergleichen zu können, wird für den Test ein LIN-Bus mit drei sternförmig angeordneten LIN-Knoten aufgebaut, so dass jeder LIN-Knoten und somit jeder LIN-Transceiver den gleichen Abstand und die gleichen HF-Eigenschaften (bezogen auf die Einspeise-Stelle) hat. Ein LIN-Knoten wird als Sender betrieben; das auf dem LIN-Bus zu übertragende Signal wird mit einem Pattern-Generator erzeugt. Die beiden anderen LIN-Knoten arbeiten als Empfänger. Eingespeist werden Störsignale im Frequenzbereich von 1 MHz bis 1 GHz. Das Störsignal wird für jede zu testende Frequenz langsam von 0 bis 34 dBm erhöht. Als Fehler wird gewertet, wenn sich das Timing des Signals am Empfängerausgang (RxD) um mehr als 15 % oder die Spannungspegel um mehr als 0,9 V gegenüber dem ungestörten Signal verändern. Dies sind die Werte, die in der LIN-EMVTestspezifikation als maximale Abweichung erlaubt sind. Die einzelnen Werte für einen Ausfall werden dann über der Frequenz in einem Diagramm aufgetragen. Als Grenzwerte für diesen Test werden von den führenden Fahrzeugherstellern Werte zwischen 25 dBm und 30 dBm genannt.

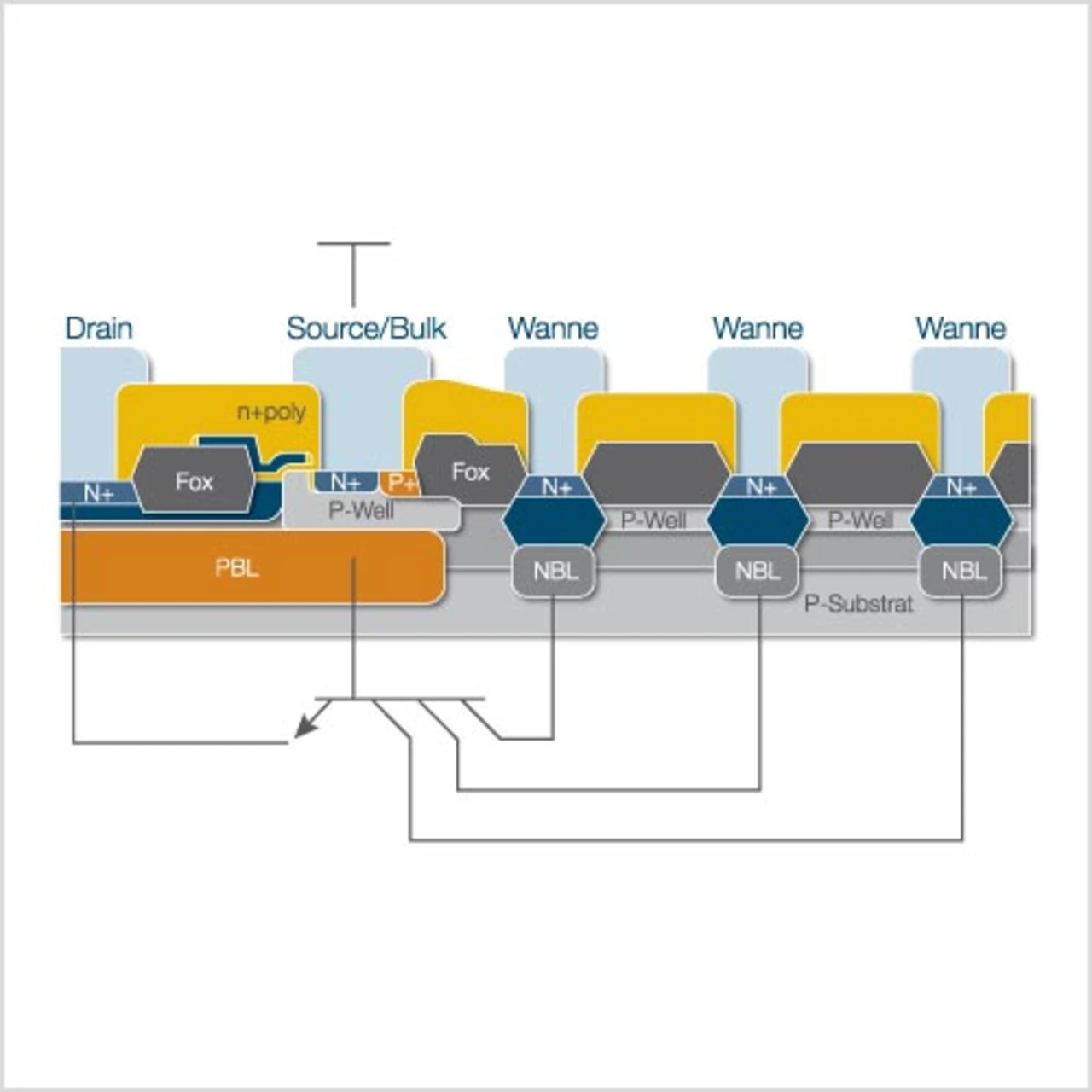

SOI-Technologie für den LIN-Bus

Bei diesen Tests zeigen vor allem Schaltkreise ihre Schwächen, die in einer Technologie entwickelt sind, bei der die einzelnen Bauelemente durch Sperrschichten isoliert sind. Hier hat sich ein Verfahren bewährt, das stattdessen auf eine Oxid-Isolation setzt: SOI (Silicon on Insulator). Der Vorteil dieser Technologie liegt auf der Hand: Durch elektromagnetische Einstrahlung überlagert ein hochfrequentes Signal das Bussignal, das auch negativere Werte als das Masse-Potential annehmen kann. Hierdurch werden parasitäre Transistoren, die sich an diesen Pins befinden, aktiviert und verursachen Störungen in weiten Bereichen der ICs (Bild 2).

Die SOI-Technologie verhindert dieses Verhalten zuverlässig: Bedingt durch die Oxid-Isolation, gibt es keine parasitären Transistoren zu den Nachbarwannen. Dies zeigen auch DPITests von ICs, die in SOI-Technologie gefertigt wurden. Der LIN-Transceiver ATA6662 (Atmel) etwa zeigt bis zur Testgrenze von 34 dBm keine Ausfallerscheinungen (Bild 3).

- SOI für den LIN-Bus #####

- SOI für den LIN-Bus

- SOI für den LIN-Bus

- SOI für den LIN-Bus