Effiziente Kommunikation zwischen Steuergeräten im Automobil

Micro Link Interface: leistungsfähig von Chip zu Chip

Fortsetzung des Artikels von Teil 3

Micro Link Interface: leistungsfähig von Chip zu Chip

Durch die Verwendung von parallelen Kommunikationsbussen lässt sich das Problem der Bandbreite in den Griff bekommen, aber die Anzahl der erforderlichen Signale und das aufwendigere Layout erhöhen die Kosten. Zur Lösung des Problems wurde bei Infineon [1] in den vergangenen Jahren ein neues Kommunikationsprotokoll entwickelt und in der TriCore-Controller-Familie eingesetzt: das „Micro Link Interface“ (MLI). Dieses wurde vor kurzem für die Standardisierung offengelegt. Die „Micro Link“-Spezifikation wurde Anfang 2003 von Infineon im Rahmen eines Kundenprojektes entwickelt. Seit Mitte 2007 steht sie – gegen Registrierung – bei Infineons IP-Partner IPextreme [2] kostenfrei zum Download zur Verfügung.

Funktionsweise des „Micro Link Interface“

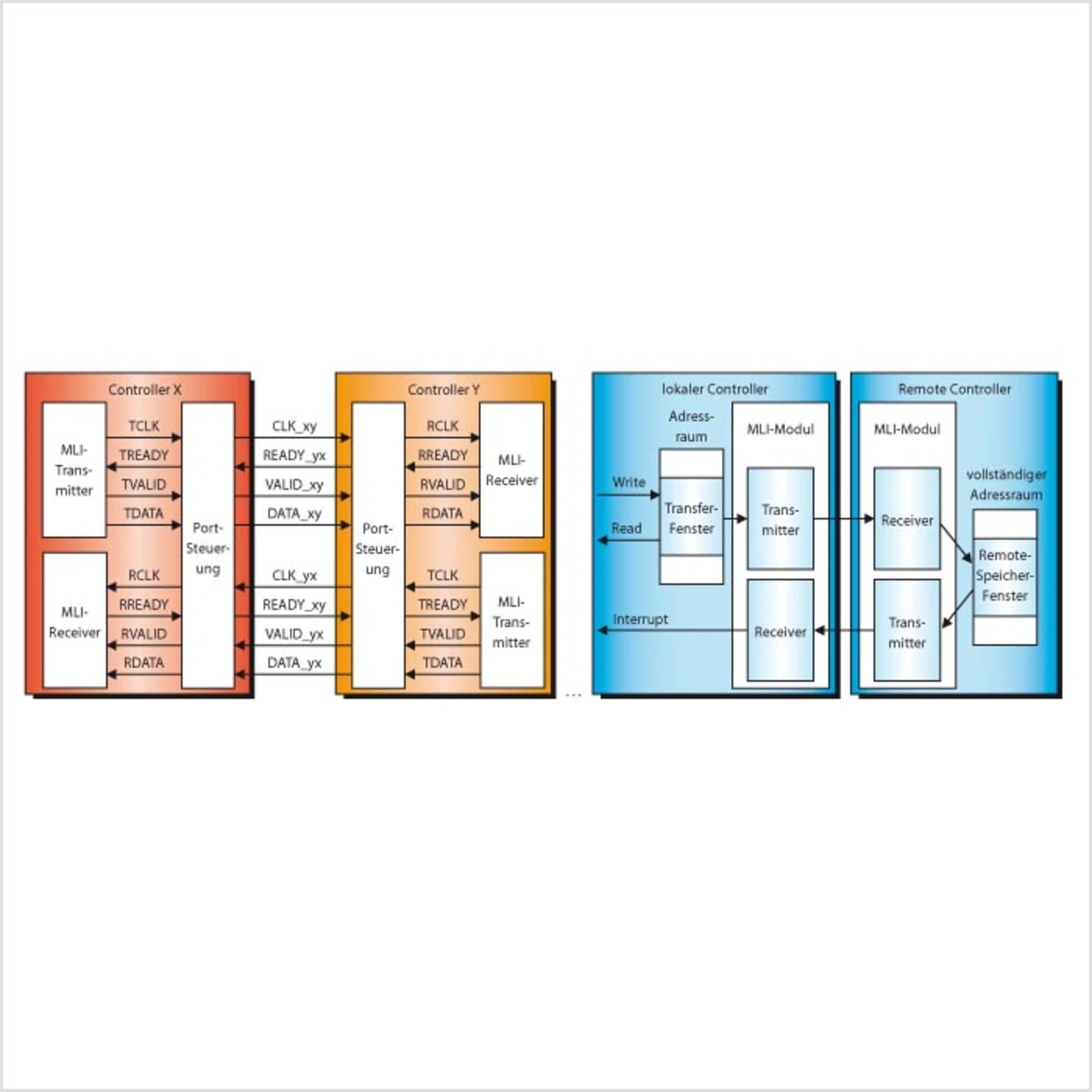

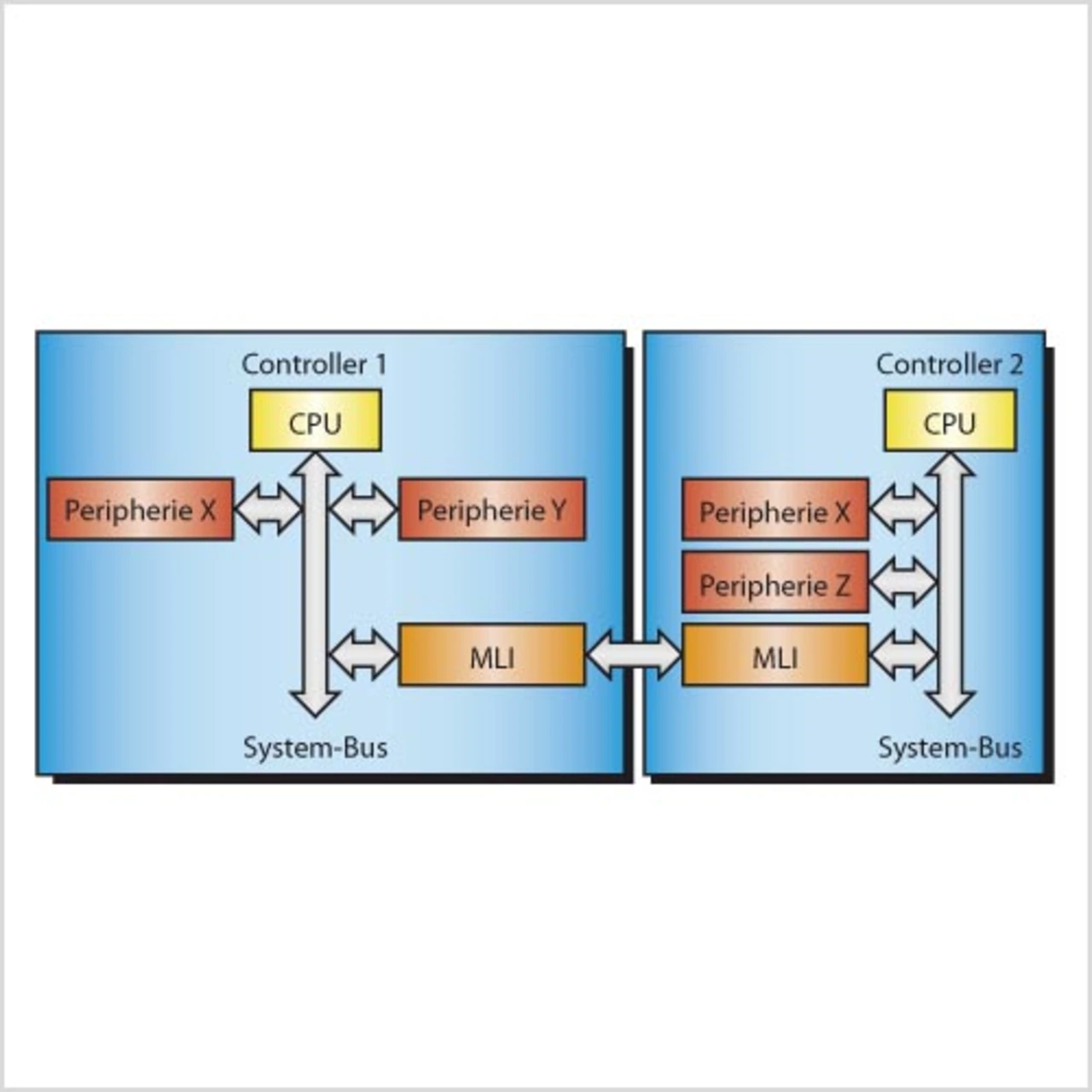

Das MLI ermöglicht eine flexible System-Aufteilung und hohe Datenübertragungsraten und benötigt am Chip nur wenige Pins. Zusätzlich bietet es Mechanismen für die Entlastung der Steuer-CPU von der Datenkommunikation (Bild 2). Das MLI ist eine serielle, vollduplex arbeitende Schnittstelle, die auf die Chip-zu-Chip-Kommunikation hin optimiert ist. Sie arbeitet für jede der beiden Übertragungsrichtungen mit vier Leitungen: Takt (CLK), Daten (DATA) sowie den beiden Handshake-Signalen READY und VALID. MLI ermöglicht Datentransfers mit 45 Mbaud, die Datenübertragungsrate ist dabei programmierbar.

Bei SPI wird der Haupttakt (Master Clock) für den Sende- und den Empfangsbetrieb genutzt. Die Übertragung ist für „Senden“ bzw. „Empfangen“ jeweils auf eine Takt-Periode beschränkt. Die Laufzeitverzögerung auf der Leitung begrenzt die maximale Datenübertragungsrate auf einen Wert, bei dem Master- und Slave-SPI-Geräte die Synchronisierung noch aufrechterhalten können (Loop Delay). Mit MLI lassen sich höhere Datenübertragungsraten erzielen, weil jeder MLI-Transmitter seinen eigenen Übertragungstakt (Transmit Clock) zur Verfügung stellt. Das MLI-Protokoll sieht hier zusätzlich Handshake-Signale vor, um eine Übertragung zu signalisieren. Die Handshake-Signale zwischen „Transmit“ und „Receive“ können daher länger als eine Taktperiode auf der Leitung laufen. MLI bestimmt die Signallaufzeit zwischen Transmitter und Receiver während der Initialisierung und verwendet diesen Parameter bei der späteren Übertragung.

MLI erlaubt die parallele Datenverarbeitung und die Aufteilung der Rechenleistung (Resource Sharing) zwischen Funktionsbausteinen, die mit unterschiedlichen Taktraten oder Spannungsbereichen arbeiten, wie z.B. A/D-Umsetzer. Es können Prozessoren verschiedenen Typs oder anwendungsspezifische Controller über MLI direkt miteinander ohne spezielle Anpassungs-Logik verbunden werden (Bild 3). Die Schreib- und Lesebefehle können zwischen vier angeschlossenen Komponenten in beide Richtungen gleichzeitig und autonom durchgeführt werden. Sowohl Daten als auch Adressen mit 8, 16 oder 32 bit können über das MLI-Interface übermittelt werden. Darüber hinaus lassen sich auch Befehle übertragen, etwa um Interrupts auszulösen oder „Software Tasks“ der Nachbar-CPUs zu steuern.

Der Datentransfer zwischen Sender und Empfänger erfolgt, ohne dass die daran beteiligten CPUs der an die MLI-Schnittstellen angeschlossenen Komponenten unterbrochen würden. Der Datentransfer wird über eine Schreib/Leseoperation beim Sender initiiert. Daraufhin werden die zu übertragenden Adressen in einen speziell für die MLI-Übertragung reservierten Adressbereich (Transferfenster) geschrieben bzw. von dort gelesen. Die Handshake-Signale und das physikalische Übertragungsprotokoll werden hierzu automatisch von den beteiligten MLI-Controllern generiert, ohne dass die CPU damit belastet wird (Bild 4).

- Micro Link Interface: leistungsfähig von Chip zu Chip

- Micro Link Interface: leistungsfähig von Chip zu Chip

- MLI in der praktischen Anwendung

- Micro Link Interface: leistungsfähig von Chip zu Chip