Effiziente Kommunikation zwischen Steuergeräten im Automobil

Micro Link Interface: leistungsfähig von Chip zu Chip

Fortsetzung des Artikels von Teil 1

Micro Link Interface: leistungsfähig von Chip zu Chip

Diese Vorteile können auch in anderen Anwendungen genutzt werden. MLI bietet mit seiner effizienten Datenübertragung einen einfachen Weg, die Rechenleistung einer Anwendung zu skalieren. Das ist interessant für Anwendungen, die hohe Anforderungen an die Rechenleistung stellen. Dabei kann heute zwischen mehreren Multi-Core-Ansätzen gewählt werden. Es kann ein symmetrisches System sein, in dem zwei identische Controller ähnliche Aufgaben parallel ausführen, um den Durchsatz zu erhöhen. In einem Motor mit acht, zehn oder zwölf Zylindern etwa könnte jeder Mikrocontroller eine Zylinderreihe ansteuern und dabei z.B. Kalibrierungsdaten oder Berechnungsergebnisse über die MLI-Verbindung mit dem anderen Controller austauschen. Es lassen sich aber auch asymmetrische Ansätze realisieren. Dabei führen zwei Controller jeweils unterschiedliche Aufgaben aus, wie z.B. eine Getriebesteuerungseinheit und eine Motorsteuerungseinheit in einer einzigen ECU.

Schließlich lassen sich mit der MLI-Schnittstelle programmierbare Logikbausteine für Industrie-Steuerungen, wie z.B. FPGAs, mit MLI-basierten Standard-Komponenten oder weiteren FPGA-Bausteinen verbinden. Infineon bietet hier entsprechende MLI-Peripherie an wie den FlexRay-Controller CIC310 oder den 5-V-A/D-Umsetzer CIC751 [4, 5]. Die MLI-Schnittstelle selbst kann, ebenso wie der Tricore-CPU-Core, als Design-Block in Verilog/ VHDL über IPextreme bezogen werden. (Dr. Jens Würtenberger)

| Dipl.-Ing. Laurent Beaurenaut hat an der ENSEEIHT (Ecole Nationale Superieure d’Electronique, Electrotechnique, Informatique, Hydraulique et Telecommunications) in Toulouse, Frankreich, studiert. Seit 2004 arbeitet er als Applikationsingenieur für Automotive Microcontrollers bei Infineon. info@infineon.com |

| Dipl.-Ing. Benedikt Schmänk hat an der Universität Duisburg Elektro- und Informationstechnik studiert. Seit 2004 arbeitet er als Projekt-Manager bei IPextreme in München. In dieser Position ist er technisch verantwortlich für verschiedene IP-Produkte, z.B. Bluetooth, CR16, C166, MSC und MLI. Vor seinen Wechsel zu IPextreme startete er seine Berufslaufbahn als Consultant- und Entwicklungs-Ingenieur bei Synopsys. info@ip-extreme.com |

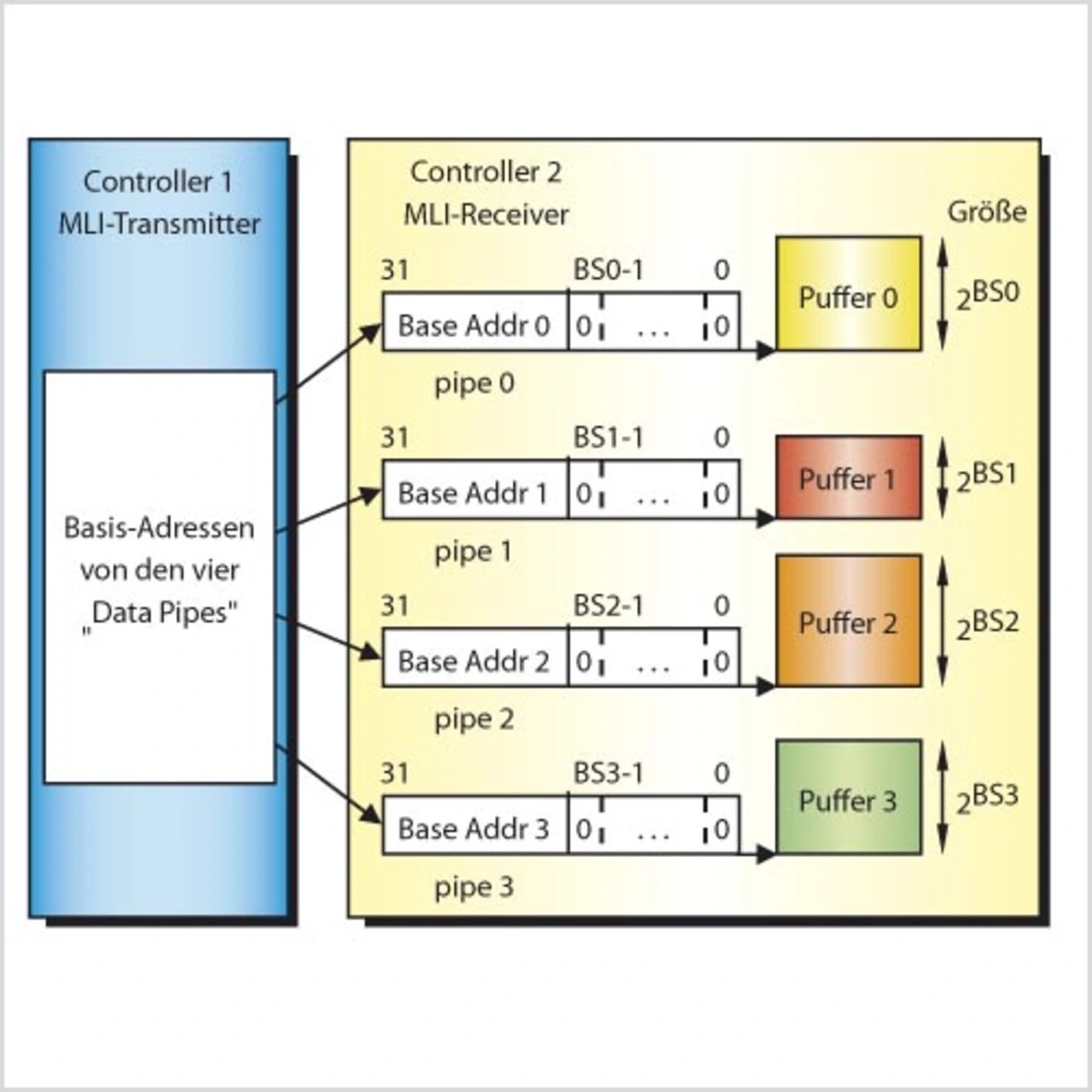

Das MLI-Datenprotokoll verwendet „Message Frames“. Darin werden neben den eigentlichen Daten Zieladdresse, Offset und evtl. zu übermittelnde Steuerbefehle dem Partner signalisiert. Die unterschiedlichen „Message“-Typen werden über einen 4 bit langen „Header“ am Anfang klassifiziert, der um ein Paritätsbit ergänzt wird. Die Datenkommunikation erfolgt über so genannte „Data Pipes“. Jede „Data Pipe“ kann als eine logische Verbindung zwischen Sender (Transmitter) und Empfänger (Receiver) aufgefasst werden. Es lassen sich pro MLI-Schnittstelle vier „Data Pipes“ einrichten. Diese verweisen auf programmierbare Adressbereiche auf der Seite des Receivers. Der Transmitter überträgt statt der vollständigen 32-bit-Adresse nur den Wert des Offsets relativ zur Basisadresse sowie eine Referenz zu der Pipe, die verwendet werden soll. Dies hat den Vorteil, dass bei aufeinander folgenden Transfers mit aufsteigender Adresse nur der Offset, nicht aber die komplette Adresse jedes Mal neu übertragen werden muss.

- Micro Link Interface: leistungsfähig von Chip zu Chip

- Micro Link Interface: leistungsfähig von Chip zu Chip

- MLI in der praktischen Anwendung

- Micro Link Interface: leistungsfähig von Chip zu Chip