Entwurf von Vernetzungstopologien (In-Vehicle Networks)

Das Virtuelle Fahrzeug (Teil 1)

Fortsetzung des Artikels von Teil 2

StateAMS für die Modellierung von Analog/Mixed Signal Statemachines

Drosselmodelle von Herstellern wie Epcos bzw. TDK sind ebenfalls im Bibliotheksumfang enthalten. Für den CAN-Communication-Controller wurde ein Modell entwickelt, das über die für die Signalintegrität relevanten Funktionen verfügt. Das Modell beinhaltet das Bit-Timing inklusive der Synchronisation (Hard- und Softsynchronisation), Arbitrierung und Acknowledgement. Ein kompletter Communication-Controller wäre für diese Untersuchungen nicht sinnvoll, da nur ein Teil des Funktionsumfangs für diese Betrachtungen relevant ist. Das Modell ist über eine digitale Statemachine implementiert worden.

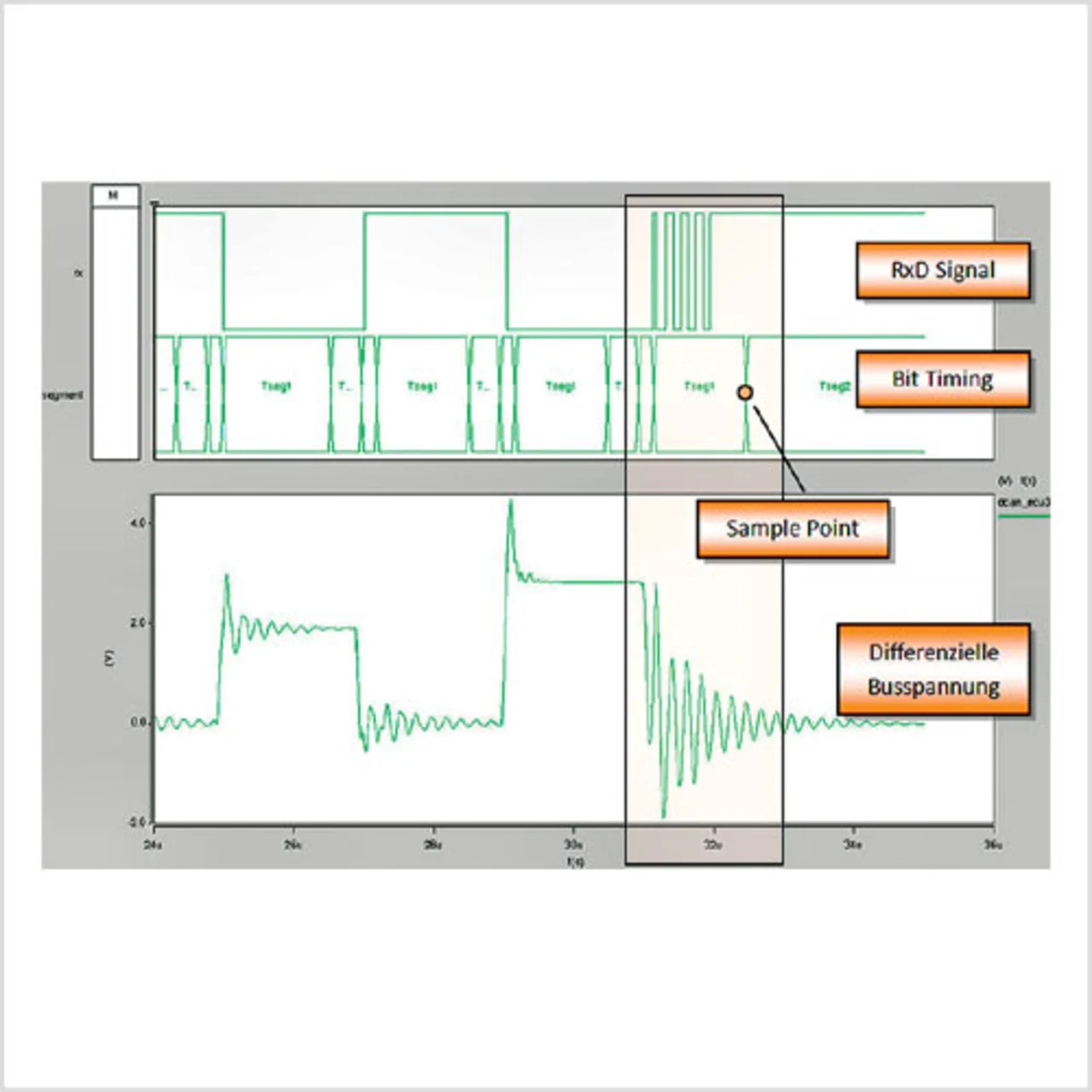

Saber bietet hierzu das Tool StateAMS, das die Modellierung von Analog/ Mixed Signal Statemachines ermöglicht. Während übliche digitale Zustandsdiagramme nur die zeitgesteuerte Modellierung ermöglichen, erlaubt StateAMS auch die Modellierung analoger Anteile. Wichtige Bestandteile der Modellbibliothek sind auch die Kabelmodelle, die über einen integrierten Fieldsolver generiert werden können. Das Kabelmodell ist der wichtigste Bestandteil bei der Untersuchung der Signalintegrität. Das Kabelmodell in Saber basiert auf dem W-Element-Ansatz und berücksichtigt auch frequenzabhängige Verluste. Mit dem virtuellen Prototypen gemäß Bild 2 kann z.B. eine Round-Robin-Kommunikation simuliert werden. In diesem Fall agiert jedes Steuergerät einmal als Sender und alle anderen Steuergeräte als Empfänger. Für den Fall von 14 Steuergeräten würden somit 14 Simulationen durchlaufen werden. Bild 4 zeigt exemplarisch einige Ergebnisse aus einem Simulationsdurchlauf für ein Steuergerät. Die Ergebnisse zeigen die Differenzspannung (Differenz zwischen CANH und CANL) am physikalischen Bus bzw. direkt am Transceiver.

Mit Hilfe der Simulation liegen dem Entwickler nun unmittelbar die benötigten Daten vor, um die Topologie in ihrer Qualität bewerten zu können. Das ist möglich, obwohl noch kein Hardware-Prototyp vorliegt. Aus den simulierten Daten lassen sich nun Punkte wie Flankensteilheit, Propagation Delays oder auch Einschwingdauer bewerten. Ein weiteres Highlight, welches über den rein analogen Anteil der simulierten Busspannungen hinausgeht, sind die Daten aus dem Bit-Timing. Mit Hilfe des Controller-Modells ist es dem Entwickler auch möglich, das Bit-Timing zu verifizieren. Letzteres kann bequem im Controller-Modell eingestellt und unmittelbar mit der gesamten Topologie validiert werden. Neben der analogen Busspannung hat der Entwickler Zugriff auf das digitale Receive-Signal (RxD), den Verlauf des Bit-Timings und sämtliche controllerinternen Signale. Hieraus lässt sich z.B. unmittelbar ablesen, wie nah sich der Abtastzeitpunkt des Controllers am kritischen Gebiet befindet, in dem signifikantes Ringing auftritt. In Bild 4 sind deutlich die mehrfachen Signalwechsel des Receive-Signals zu erkennen. Der Abstand der letzten Flanke zum Abtastzeitpunkt (Sample-Point) liefert eine genaue Information, wieviel Reserve noch vorhanden ist. Gerät der Sample-Point zu nah an dieses Gebiet, können Fehlabtastungen auftreten.

- Das Virtuelle Fahrzeug (Teil 1)

- Das Virtuelle Fahrzeug (Teil 1)

- StateAMS für die Modellierung von Analog/Mixed Signal Statemachines

- Virtuelle Prototypen von Topologien ermöglichen detaillierte Analysen

- Das Virtuelle Fahrzeug (Teil 1)