Der Micro-Second-Bus in Powertrain-Anwendungen

Kommunikation in automotiven Applikationen

Fortsetzung des Artikels von Teil 2

Kommunikation in automotiven Applikationen

In heutigen Systemen wird üblicherweise die SPI-Schnittstelle für die Initialisierung, das Senden von Kommandos und das Lesen des Fehlerzustandes eingesetzt. Je nach Topologie werden mehrere SPI-Schnittstellen benötigt, die vom Mikrocontroller zur Verfügung gestellt werden. Zusätzlich werden Standard-I/O-Ports verwendet, um die Echtzeit-Steuerung der Lasten über PWM-Signale zu realisieren.

Es soll angenommen werden, dass 25 Aktoren verteilt über drei Treiber-ICs in Echtzeit zu steuern sind: Dies erfordert 37 Pin-zu-Pin-Verbindungen: 25 I/O-Pins und drei SPI-Schnittstellen mit jeweils vier Pins. Dies erhöht die Komplexität der PCB deutlich mit negativem Einfluss auf den benötigten Platz, die Kosten und die Zuverlässigkeit.

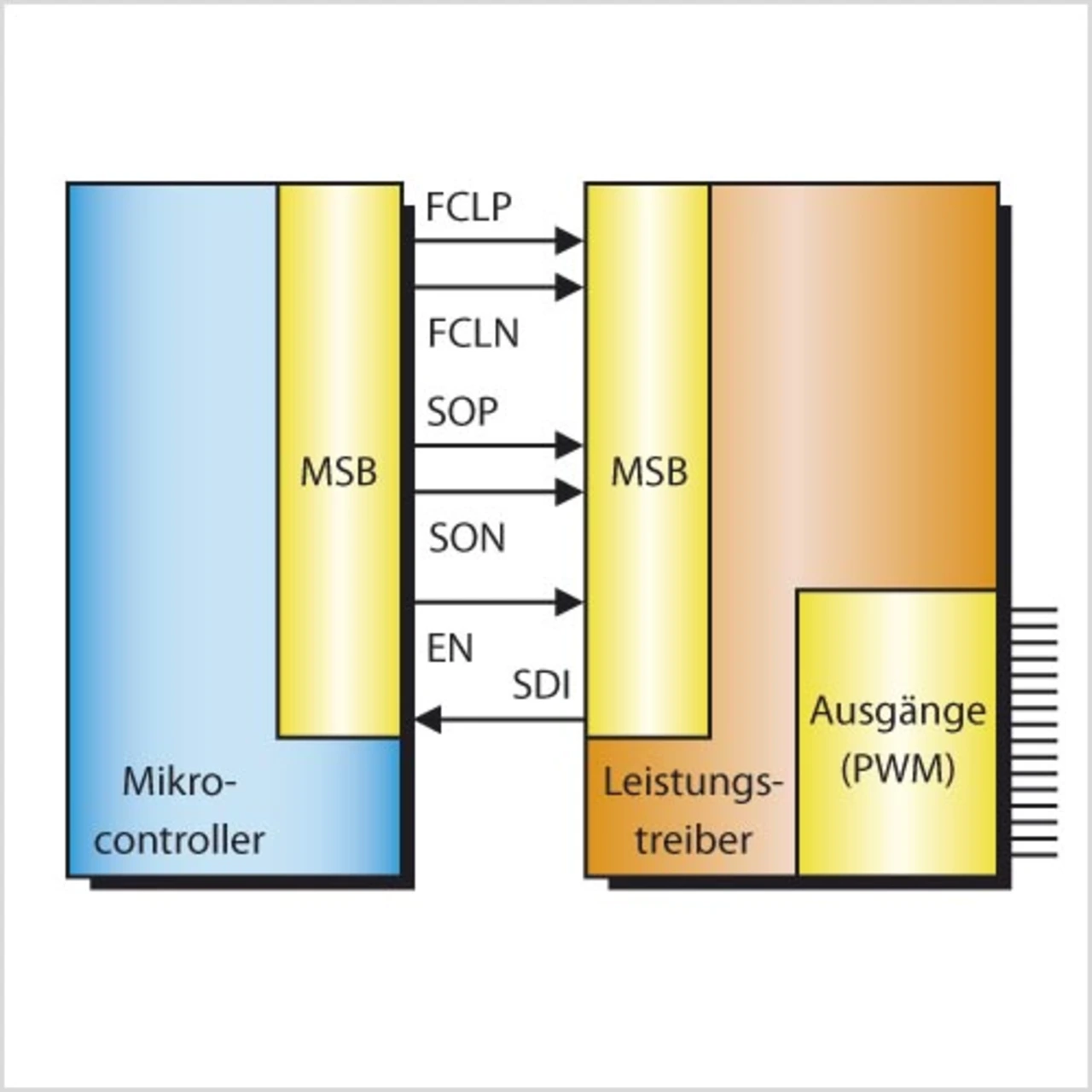

Der MSB optimiert den Datenaustausch und die Pin-Anzahl zwischen Mikrocontroller und Leistungstreiber-Baustein. Mit sechs Pins (bei LVDS) können verschiedene Arten von Informationen (PWM-Daten und Steuerdaten) über die gleiche Schnittstelle transferiert werden. Die Skalierbarkeit der Schnittstelle ist ein weiterer Vorteil. Mehrere Leistungstreiber-Bausteine können über einen MSB-Peripheriebaustein gesteuert werden. Ein weiterer Leistungstreiber-Baustein benötigt dabei nur einen weiteren Chip-Select-Pin.

Bei der Nutzung von MSB mit LVDS werden im genannten Beispiel nur 13 Pin-zu-Pin-Verbindungen benötigt. Hier benutzt ein Mikrocontroller zwei MSB-Ports (mit jeweils sechs Pins) und insgesamt drei verschiedenen Chip-Select-Pins. Durch weitere Integration auf dem Leistungs-IC kann dies noch weiter reduziert werden: Ein 40-MHz-MSB erlaubt, innerhalb 1 μs bis zu 40 Lasten anzusteuern und deren Zustand zu ändern. Somit könnte bei einer entsprechend optimierten Partitionierung (z.B. eine Integration der o.g. 25 Leistungstreiber in einen Leistungs-IC) eine Ansteuerung über nur sechs Pin-zu-Pin-Verbindungen erfolgen.

Der MSB kann mit einer höheren Frequenz als SPI betrieben werden. SPI verwendet denselben Takt für sendende und empfangende Daten, daher ist die Baudrate in der Praxis durch die Signallaufzeit, das sogenannte „Loop Delay“, begrenzt. Die typische Grenze liegt hier bei 10 MBaud. Beim MSB sind jedoch Hin- und Rückkanal voneinander entkoppelt. Daher kann der MSB mit Transferraten von bis zu 40 MBaud vom Mikrocontroller zum Leistungstreiber-Baustein betrieben werden (Downstream-Kanal). Ein asynchroner Rückkanal mit geringerer Datenrate (10 KBaud bis 1 MBaud) erlaubt Status- und Diagnosefunktionen.

MSB in der praktischen Anwendung

Der MSB ist entwickelt worden, um die Mikrocontroller-Ressourcen, die nötig, sind um die Leistungstreiber-Bausteine zu bedienen, auf ein Minimum zu reduzieren. In den AUDONext-Generation- und AUDO-Future-Mikrocontrollern von Infineon, die auf der TriCore-Architektur basieren, erzeugt der Timer-Baustein laufend das von der Applikation benötigte PWM. Diese Signale werden intern zum MSBModul geleitet und in einem Schieberegister serialisiert. Das MSB-Modul ist programmiert, den Inhalt des Schieberegisters automatisch, d.h. ohne Mikrocontroller-Intervention, auszugeben. Die Übertragungsrate der Daten ist programmierbar. Durch hohe Baud-Raten kann trotz der Daten-Serialisierung (weniger als 1 μs) eine hohe zeitlicher Auflösung erreicht werden. Außerdem können auf Grund der flexiblen Generation der Chip-Select zwei Leistungstreiber-Bausteine innerhalb eines einzigen Downstream-Frame adressiert werden. In High-End-Anwendungen, wo mehr als zwei Slaves mit dem Mikrocontroller verbunden sind, kann am Ende der Downstream-Frame-Übertragung ein Interrupt erzeugt werden, so dass der Mikrocontroller die Chip-Select dynamisch neu konfiguriert. Mit dieser Vorgehensweise können bis zu vier Slaves von einem einzigen MSB-Link gesteuert werden. Der Mikrocontroller kann jederzeit von dem Leistungstreiber-Baustein Diagnose-Informationen durch die Übermittlung von Steuer-Frames (Command Frames) anfordern. Ein Steuer-Frame wird durch einen einzigen Schreib-Vorgang in einem internen Register generiert. Die MSB-Hardware kümmert sich um das Einbringen des Steuer-Frames innerhalb der Daten-Frames. Der Leistungstreiber-Baustein, welcher den Steuer-Frame erhält, antwortet durch die Übermittlung eines Upstream-Frames, der die angeforderte Information enthält (z.B. Status-Informationen oder Fehlerkennzeichen). Ein Interrupt wird beim Empfang des Upstream-Frame im Mikrocontroller ausgelöst. Innerhalb der Interrupt-Service-Routine kann der Frame-Inhalt evaluiert werden.

Die zweite MSB-Generation hat einen hochgeschwindigkeits-synchronen Kanal (Downstream) und einen asynchronen Kanal (Upstream). Beide Kanäle sind voneinander entkoppelt. Die zweite MSB-Generation hat sechs (LVDS, Bild 2) oder vier Pins (TTL). Es können über sechs Pins bis zu 32 PWMKanäle übertragen werden. Im Folgenden wird nur noch die zweite Generation des MSB betrachtet.

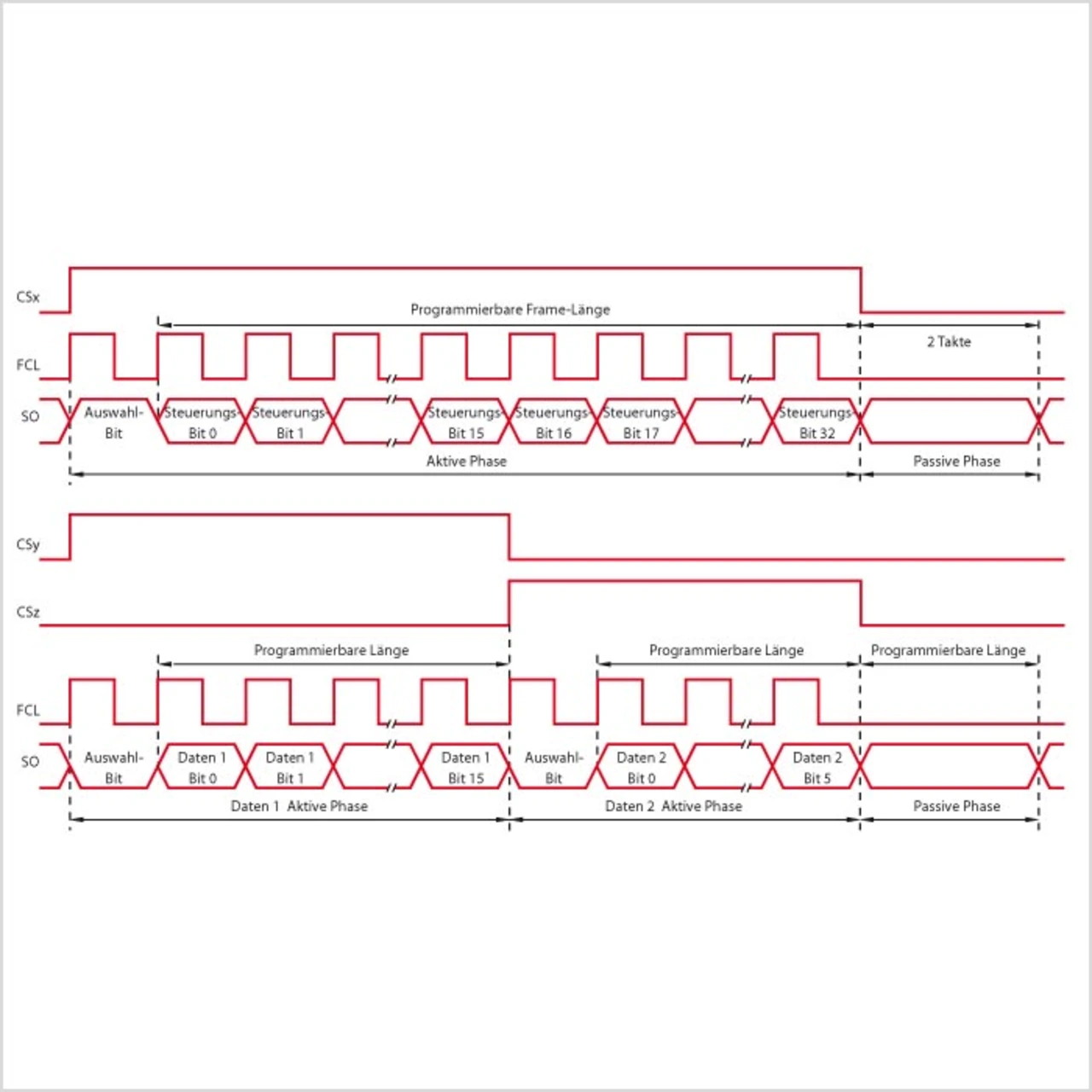

Der schnelle synchrone Downstream besteht aus einem SPI-kompatiblen programmierbaren Datenstrom mit einer Länge zwischen 2 und 34 bit. Ein Frame kann zwischen Daten und Befehlen unterscheiden (Bild 3). Die Unterscheidung erfolgt mit dem ersten gesendeten Auswahl-Bit (Select-Bit). Die Frames bestehen aus Daten, welche die PWM-Informationen von den Timer-Bausteinen zum Leistungstreiber-Baustein transferieren. Die Befehle werden benutzt, um den Leistungstreiber-Baustein zu initialisieren und zu konfigurieren.

Das MSB-Protokoll erlaubt, innerhalb eines Frames bis zu 32 bit an einen Leistungstreiber-Baustein zu senden oder jeweils bis zu 16 bit an zwei verschiedene. Dazu werden verschiedene Auswahl-Bits (Chip-Select; CSx) verwendet. Zwischen den aktiven Phasen zweier Frames (wenn Daten oder Kommandos gesendet werden) müssen mindestens zwei passive Takt-Phasen eingefügt werden, um die aufeinanderfolgenden Frames zu trennen.

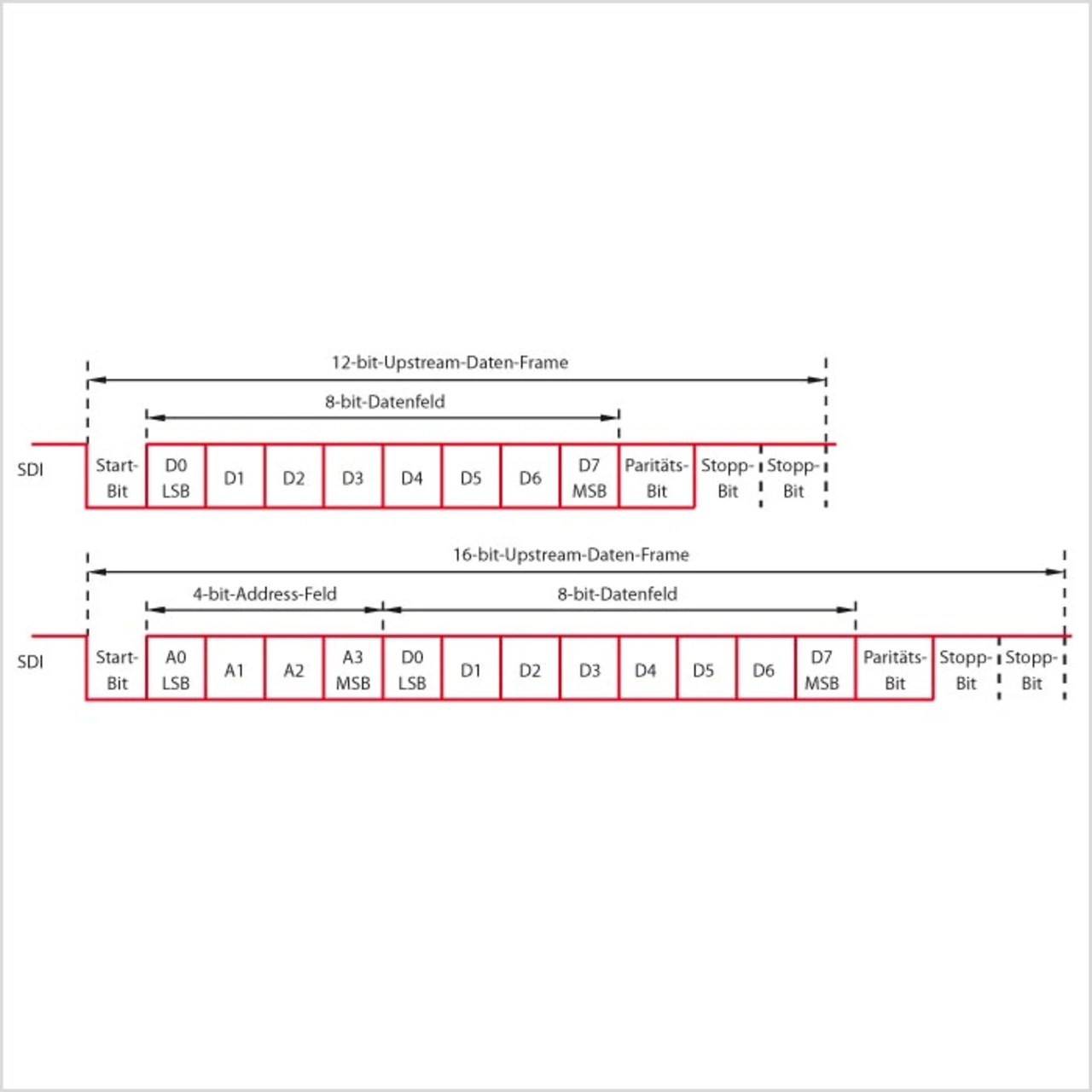

Der asynchrone Upstream-Kanal ist ein UART-kompatibler Datenstrom (Universal Asynchronous Receiver Transmitter). Er dient dazu, einen seriellen Datenstrom vom Leistungstreiber-Baustein zu empfangen. Die MSB-Upstream-Daten-Frames besteht aus den folgenden vier Teilen:

- Ein Start-Bit, das immer logisch Null ist.

- Einem optionalen 4-bit-Adressfeld.

- Einem 8-bit-Datenfeld.

- Einem Paritäts-Bit und zwei Stopp-Bits, die immer logisch Eins sind.

Der MSB besteht aus einem 12-bit-Frame, der zu dem Standard-UART-Protokoll kompatibel ist, falls das optionale Adress-Feld nicht benutzt wird. Mit dem Adress-Feld besteht der Frame aus 16 Bits. Das Adress-Feld kann genutzt werden, um den Urheber oder den Typ der Nachricht zu erhalten. Zusätzlich sind die Upstream-Daten-Frames mit einem Paritäts-Bit gesichert. Bild 4 zeigt den Aufbau des MSB.

Physikalische Transportschicht

Die MSB-Spezifikation selbst definiert keine physikalische Transportschicht für den MSB. In der Praxis sind LVDS-Signale (Low-Voltage-Differential-Bus) oder Standard-CMOS-kompatible Spannungen (3,3 V) möglich. LVDS hat sich bei Hochgeschwindigkeitsanwendungen in der Praxis durchgesetzt. LVDS hat den Vorteil, EMI zu reduzieren und längere Leitungen zwischen Mikrocontroller und Leistungstreiber-Baustein zu erlauben.

- Kommunikation in automotiven Applikationen

- Kommunikation in automotiven Applikationen

- Kommunikation in automotiven Applikationen

- Anforderungen an den MSB

- Kommunikation in automotiven Applikationen

- Motorsteuerungs-Applikationen