Entwicklung einer domänenspezifischen Mikrocontroller-Familie

Freescale und STMicroelectronics entwickeln gemeinsam domänenspezifische Mikrocontroller-Familie

Fortsetzung des Artikels von Teil 3

Crossbar-Matrix statt Parallel-Bus-Struktur

Die Systemarchitektur basiert auf Punkt-zu-Punkt-Verbindungen (skalierbare Crossbar-Matrix), womit mehrere Master (Rechenkerne, DMA, FlexRay-Controller, zusätzliche e200-Kerne) mit Slaves (Speicher, Peripherie-Blöcke) verbunden werden können. Diese Vernetzungsvariante bietet maximale Systemeffizienz und einfache Erweiterungsmöglichkeiten. Dabei wird die Basisarchitektur mit einem Skeleton-Konzept erweitert. Mit dieser Strategie zur Wiederverwendung von Modulen, wie Clock, Reset, Power und Test-Strukturen, kann die Vielfalt der Derivate über die verschiedenen Produktlinien vereinheitlicht werden.

Es erwies sich als hilfreich, dass diese Bausteine neu definiert wurden und Anforderungen aus den adressierten Applikationsbereichen berücksichtigt werden konnten. So sind die jeweils am besten geeigneten IP-Blöcke aus dem Portfolio der beiden Hersteller verwendet und teilweise modifiziert worden. Außerdem war es möglich, in dieser Familie die aktuellen Trends zur Kompatibilität zu berücksichtigen.

Alle Derivate verfügen beispielsweise über identische CAN-Zellen mit einem einheitlichen Registersatz, der sich immer im gleichen Speicherbereich befindet. So ist, unabhängig von der Anzahl der CAN-Zellen, CAN0 inklusive aller Funktionsregister immer an der gleichen Adresse und hat die gleiche Struktur. Dies gilt auch für andere Funktionsblöcke wie SPI, LIN, FlexRay oder SCI.

Ein erweiterter DMA-Controller mit der Unterstützung von Scatter/Gather-Transfers und 16 Kanälen sowie ein programmierbarer Interruptcontroller mit 16 Prioritätsstufen und über 200 Hardware- und Software-Quellen sind ebenso vorhanden wie ein Nexus-Interface, das je nach Gehäuseform bis zu Stufe 2+ ausgebaut ist.

Eine PLL mit optionaler Frequenzmodulation erzeugt im Normalbetrieb den Takt aus einem 4- bis 16-MHz-Quarz. Als Notlösung kann ein On-chip-16-MHz-RC-Oszillator genutzt werden. Für spezielle Anwendungen ist ein zusätzlicher 128-kHz-RC-Takt vorhanden, der auch ein automatisches Aufwachen des Bausteins aus den programmierbaren „low power“-Zuständen initiieren kann.

Die Flash- und RAM-Speicher werden mit ECC inklusive „single bit“-Korrektur und „double bit“-Erkennung zur Erhöhung der Datensicherheit ausgestattet. Je nach Derivat ist ein Daten-Flashspeicher mit EEPROM-Emulationsmöglichkeit vorhanden. Die Memory Protection Unit (MPU), die bei fast allen Derivaten verwendet wird, wurde nach Vorgaben des AUTOSAR-Standards angepasst.

Eine Architektur – vier Domänen

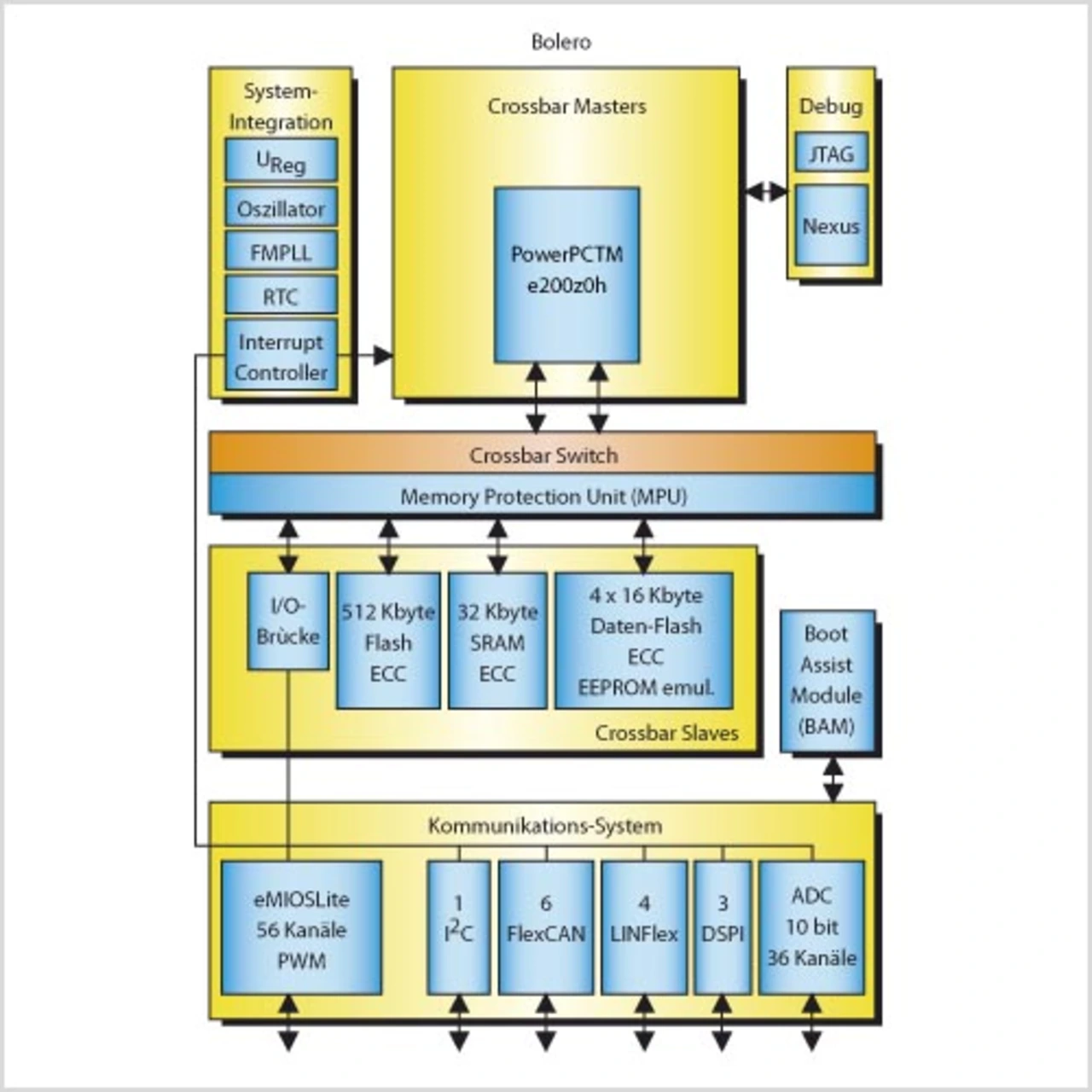

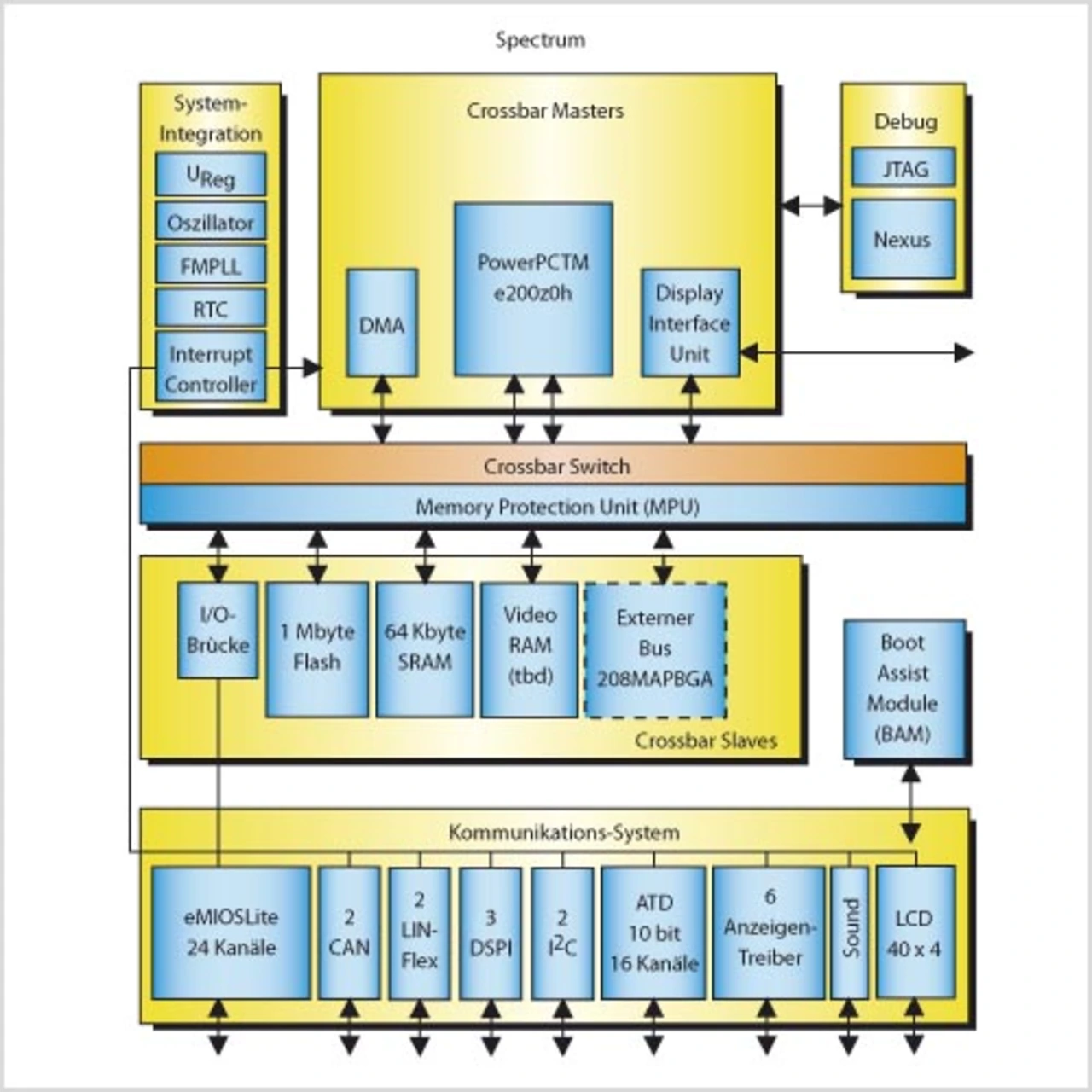

Basierend auf der beschriebenen Architekturplattform, wurden entsprechend der applikationsspezifischen Anforderungen der einzelnen Fahrzeugdomänen die vier folgenden JDP-Produktfamilien definiert (Bilder).

Karosserie

Für den Karosseriebereich wurde die Bolero-Familie entwickelt. Die Speicherausstattung liegt im Bereich zwischen 256 und 1024 Kbyte eFlash, 64 Kbyte Daten-Flash. Bis zu 32 Kbyte RAM sind als Datenspeicher vorhanden. Je nach Gehäuse (100-pin-TQFP bis 208-pin-BGA) stehen bis zu 56 Timer/PWM-Kanäle sowie bis zu 36 interne ADC-Kanäle zur Verfügung. Speziell für Gateway-Anwendungen wurden bis zu sechs CAN-Schnittstellen integriert. Bis zu vier LIN-SCI-, drei SPI- und eine I²-Schnittstelle bieten umfangreiche Kommunikationsmöglichkeiten. Stromspar-Modi, mit vollständigem oder teilweisem Datenerhalt, gestatten zusammen mit der Echtzeit-Uhr und speziellen Timern zyklisches Aufwachen und Abarbeiten von Programmsequenzen bei niedriger Gesamtstromaufnahme.

Hintergründe des Joint Development Program

Interview mit den beiden Geschäftsführern des JDP, Ross McOuat (Freescale) und Fabio Marchio (ST).

- Freescale und STMicroelectronics entwickeln gemeinsam domänenspezifische Mikrocontroller-Familie

- Freescale und STMicroelectronics entwickeln gemeinsam domänenspezifische Mikrocontroller-Familie

- Freescale und STMicroelectronics entwickeln gemeinsam domänenspezifische Mikrocontroller-Familie

- Crossbar-Matrix statt Parallel-Bus-Struktur