ARM erweitert MCU-Core für sicherheitskritische Anwendungen

Fehlertoleranter Cortex-M3

Fortsetzung des Artikels von Teil 3

Fehlertoleranter Cortex-M3

Auch die Diagnosefähigkeiten verbessern sich, da sicherheitsrelevante Informationen über die ECU gespeichert werden und vorhersehbare Befehls- Opcodes und Verhaltensweisen geprüft werden. Die fRCPU besteht somit aus einer „Schatten-Verarbeitungseinheit“, die die gleichen Befehle verarbeitet wie die CPU, einem Sequencer als Ablaufsteuerung, einer Registerbank mit denselben Inhalten wie die Hauptregister und einer Management- Einheit zum Generieren von Daten und Adressen. Um die Befehle des Cortex- M3 ausführen zu können, hat Yogitech einen ARMkompatiblen Prozessor entwickelt, der allerdings nur eine Untermenge aller ARM-Befehle verarbeiten kann, nämlich die, die für die Fehleranalyse notwendig sind. Da die frCPU auf komplett anderer RTL basiert und eigene Logik, Pipeline-Design und Takt mitbringt, ist das Modul unempfindlicher gegen Cortex-M3-spezifische Fehler, die gegebenenfalls auch bei einem redundanten Zwei-Core-System auftreten würden.

Die fRCPU vergleicht ihre Ergebnisse mit denen der CPU. Hierfür dienen unabhängige Checker, die die verschiedenen Ports überwachen (z.B. Daten/Befehls- und Adress-Ports sowie Steuersignale aus der CPU). Die System Control Unit (fRSCU) sammelt und synchronisiert sämtliche Alarme aus der CPU-Checking-Unit und den dezentralen Fault-Supervisor- Einheiten. Auf Basis dieser Informationen entscheidet die fRSCU, ob sich das System aus CPU und Peripherie in einem zulässigen Betriebszustand befindet. Falls nicht, werden aufgrund der architekturbezogenen Sicherheitsanforderungen Maßnahmen eingeleitet wie etwa Meldung an das Betriebssystem oder Wechsel in eine Hardware- Rückfallebene.

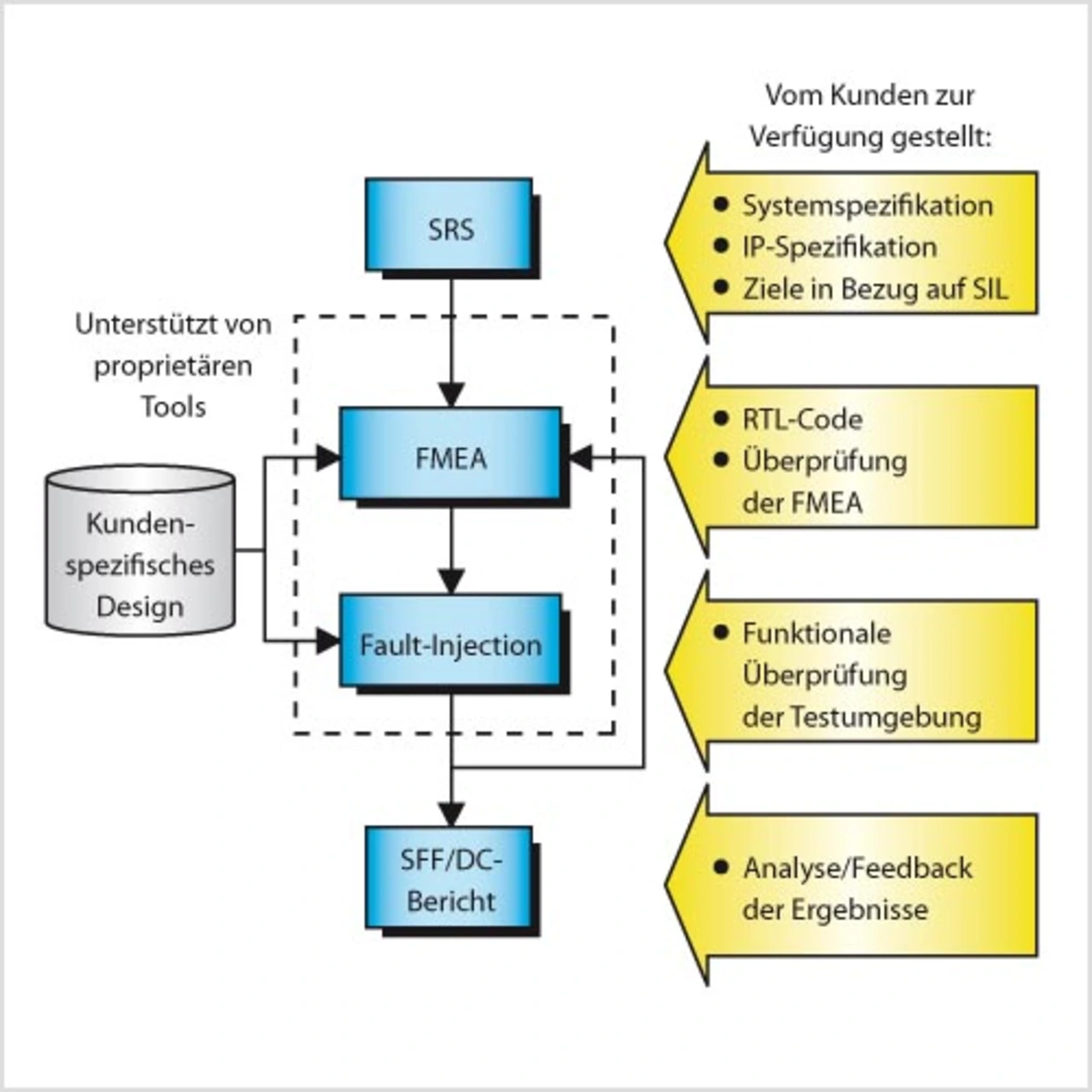

FaultRobust ist ein plattformbasiertes Konzept aus einer IEC-61508-konformen Design- und Validierungs-Methodik auf der Basis von FMEA (Failure Mode and Effects Analysis) und Fehlerinjektion. Weitere Bestandteile sind eine flexible, konfigurierbare Bibliothek aus Hardware und Software-IP ergänzend zu den SoC-Subsystemen und eine Tool-Suite auf der Grundlage existierender Compiler für die Hardware/ Software-Integration und den Konfigurationsablauf. Jedes faultRobust- IP (fRIP) kann eigenständig genutzt oder mit anderen fRIPs zu einer Komplettlösung kombiniert werden. Das Rückgrat des Konzepts ist die faultRobust-Methodik (Bild 2). Mit Scripts auf Basis kommerziell verfügbarer EDA-Tools extrahiert das fRFMEA-Tool Informationen aus der Safety Requirements Specification (SRS) und dem Design-Datenbestand und gibt sie in ein sehr detailliertes Failure-Mode- and Effects-Analysis- Worksheet ein. Fehlermodelle und Ausfallmodi werden dann nach IEC-Richtlinien begutachtet. SFF (Safe Failure Fraction) und Diagnose-Abdeckung werden anschließend mit statistischen Formeln im FMEA-Worksheet automatisch berechnet.

- Fehlertoleranter Cortex-M3

- Fehlertoleranter Cortex-M3

- Fehlertoleranter Cortex-M3

- Fehlertoleranter Cortex-M3

- Fehlertoleranter Cortex-M3