ARM erweitert MCU-Core für sicherheitskritische Anwendungen

Fehlertoleranter Cortex-M3

Fortsetzung des Artikels von Teil 1

Fehlertoleranter Cortex-M3

Ein weiteres Element zum Energiesparen ist eine neue Artisan-Standard-Zellenbibliothek, um den Cortex-M3 in einem 0,18-μm-Prozess zu implementieren, der die Leckströme minimiert. Laut ARM kann diese Physical-IP Leckströme im Vergleich zu konventioneller IP in einem generischen Fabrikationsprozess um den Faktor 20 reduzieren und nebenbei die Die- Fläche um 20 % verringern. Bild A zeigt das Blockdiagramm des Cortex-M3. Wenn er mit 16 Interrupts, einem Debug-Port, allen Hardware-Breakpoints, der Trace- Makrozelle (ETM) und der Speicherschutz- Einheit (MPU) konfiguriert wird, benötigt er etwas mehr als 80 000 Gatter. Durch Verzicht auf die MPU lassen sich 17 000 Gatter, auf die ETM 7500 Gatter und auf die Breakpoints 4000 Gatter einsparen.

Obwohl der Cortex-M3 nicht derartig konfigurierbar ist wie Cores von ARC International, MIPS Technologies und Tensilica, ist er für einen Prozessor, der keinen benutzerspezifisch konfigurierbaren Befehlssatz hat, erstaunlich flexibel. Bemerkenswert ist, dass er in einer Minimalkonfiguration rund 20 % kleiner ist als ein ARM7TDMI-S.

Die Norm IEC 61508

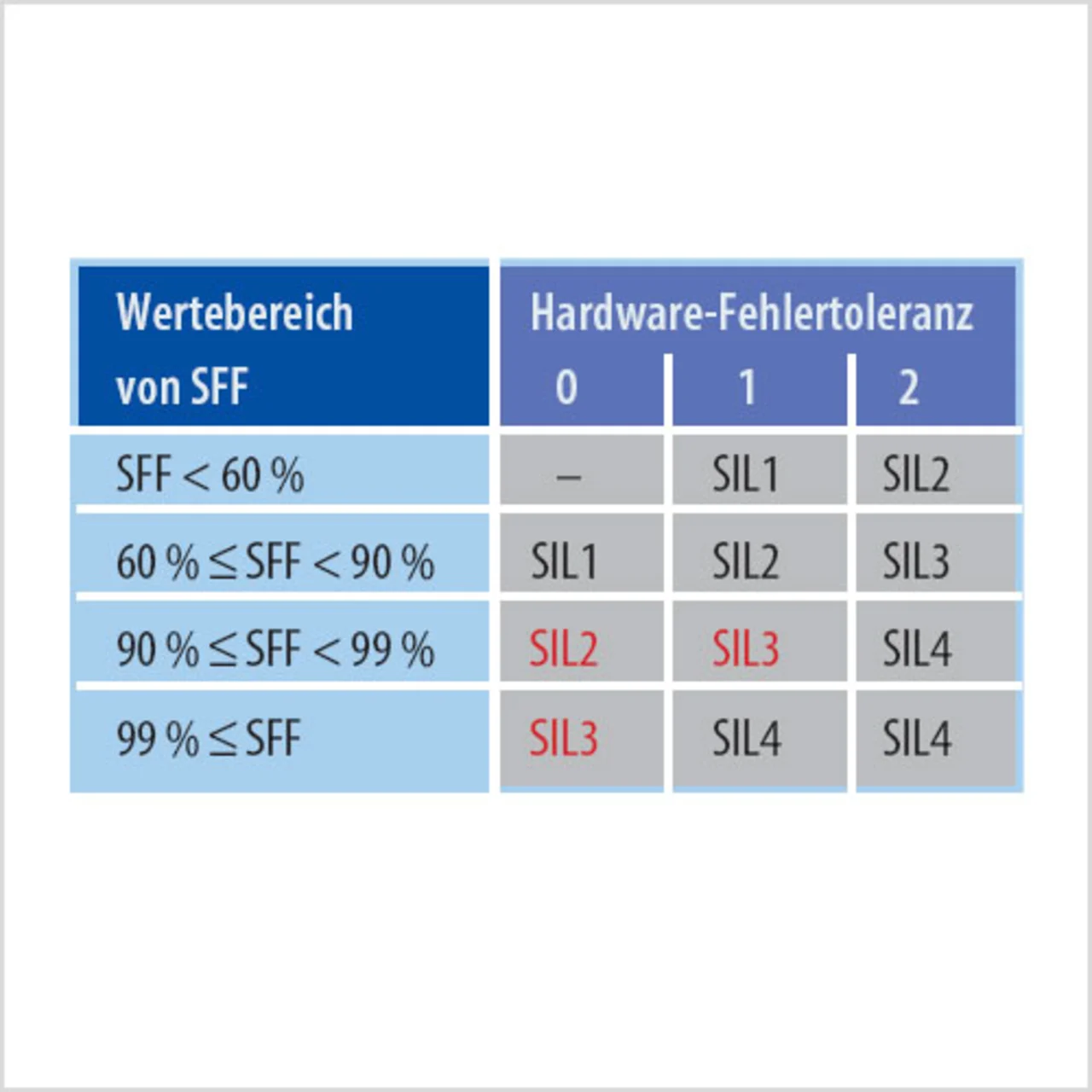

Die internationale Norm IEC 61508 bezieht sich auf die funktionale Sicherheit elektrischer, elektronischer oder programmierbarer, sicherheitsrelevanter Systeme. In der Tabelle ist zusammengefasst, welcher „Safety Integrity Level“ (SIL) einem System je nach seiner SFF (Safe Failure Fraction) und seiner Hardware- Fehlertoleranz (HFT) zugeschrieben werden kann.

Unter der SFF eines Systems versteht man das Verhältnis der Rate sicherer Fehler (ein Fehler, der zu keiner sicherheitskritischen Fehlfunktion führen kann) plus der Rate gefährlicher detektierter Fehler zur gesamten Ausfallrate des Systems. Die HFT gibt die Zahl der von einem System verkrafteten Fehler an.

Höhere HFT bedeutet höhere Verfügbarkeit. Bei HFT = 0 ist es akzeptabel, dass ein fehlerbehaftetes System in einen „sicheren Modus“ eintritt. Soll es fehlertolerant sein und immer verfügbar bleiben, sind höhere HFT-Werte erforderlich.

SIL kann die Werte 1 bis 4 annehmen, wobei SIL2 als Mindestwert für ABS-Anlagen gefordert wird. SIL3 wird für aktive Sicherheitssysteme wie X-by-Wire, aktive Bremssysteme oder ESP verlangt. SIL4 wird für Single- Chip-Lösungen als nicht erreichbar angesehen und gilt für Automotive-Systeme als nicht erforderlich.

- Fehlertoleranter Cortex-M3

- Fehlertoleranter Cortex-M3

- Fehlertoleranter Cortex-M3

- Fehlertoleranter Cortex-M3

- Fehlertoleranter Cortex-M3