Einfluss der Pinbelegung auf Symmetrie und Störabstrahlung

EMV-Untersuchungen an einem FlexRay-Steckermodell

Fortsetzung des Artikels von Teil 4

Literatur

Seamless stellt Software-Profile wahlweise als Gantt-Diagramm dar, das die Reihenfolge und die Dauer von Funktionsaufrufen zeigt, oder als Balkendiagramm, das angibt, wieviel Zeit (kummulativ) in jeder einzelnen Funktion verbracht wird (Bild 3). Die Gantt-Diagrammdarstellung unterstützt den Designer bei der Klärung der Frage, ob kritische Funktionen zu einer bestimmten Zeit auftreten. Dies erleichtert die Vermeidung von Fehlern wie unvollständige Datenübermittlungen oder verlorene Pakete. Die dargestellten Informationen zum Zeitbedarf der einzelnen Funktionen kann der Entwickler nutzen, um die Leistungsfähigkeit des Gesamtsystems zu steigern, indem er für eine Beschleunigung der zeitkritischen Funktionen sorgt. Hierfür können Techniken wie das Implementieren von C-Code-Routinen in Assembler-Code oder von Software-Funktionen in Hardware verwendet werden.

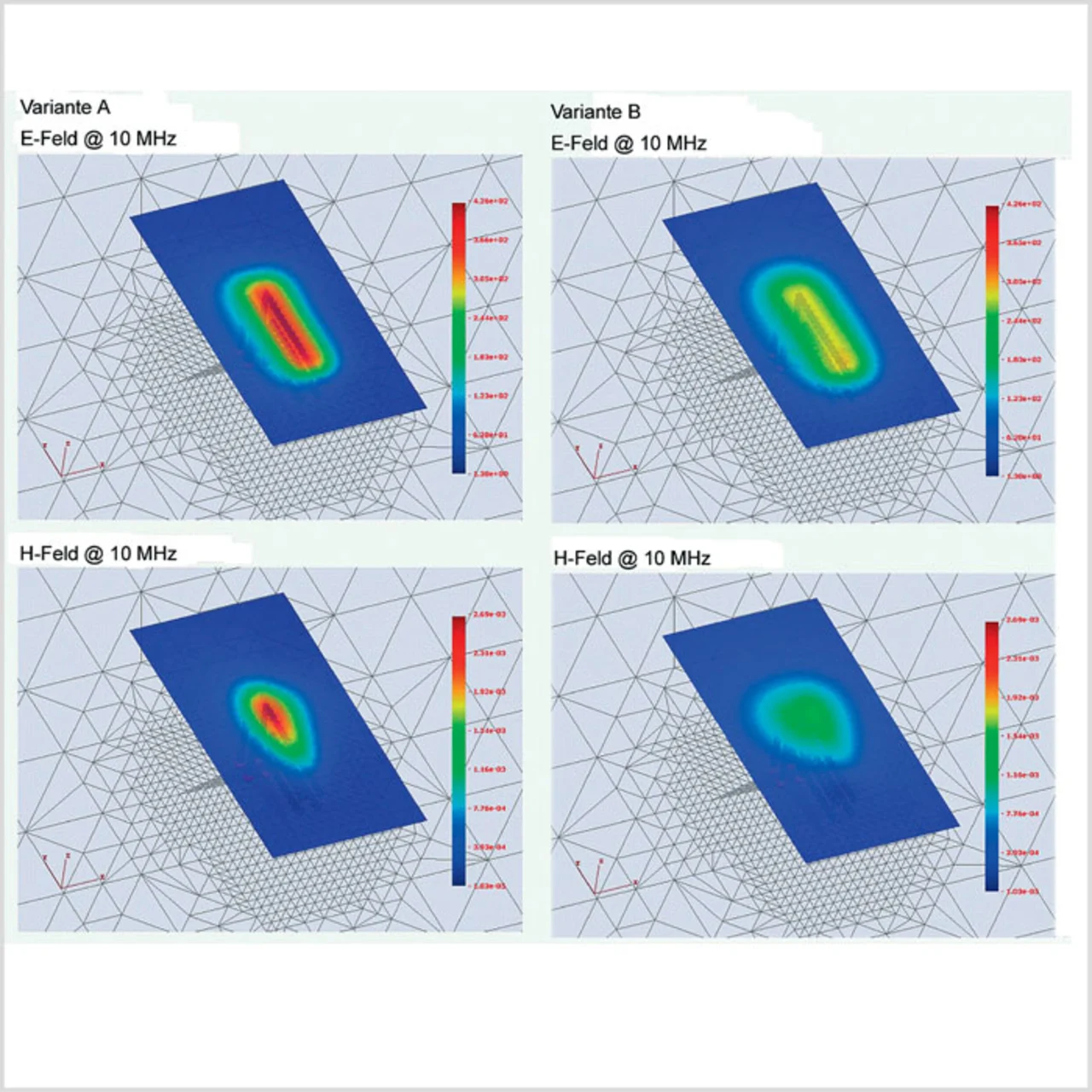

Abschließend ist festzuhalten, dass bei der Untersuchungsvariante die Sternkreuzung der Pins die beste Symmetrieeigenschaft zeigt. Wesentliches Merkmal der Untersuchungsmethodik ist die gute Übereinstimmung zwischen Messung, Feld- und numerischer Berechnung. Mit Hilfe des entwickelten Modells bietet sich die Möglichkeit für weitere Analysen. go

[1] Diaz Ortega, L.: Physical-Layer-Modellierung der Bussysteme CAN und FlexRay im Kraftfahrzeug. Dissertation an der TU Braunschweig, Shaker Verlag, Aachen 2005.

[2] Diaz Ortega, L.; Kraft, K.H.; Claus, L.; Döring, M.: Mit 10 Mbit/s über den FlexRay-Bus. Elektronik automotive 2006, H. 6, S. 47 bis 51.

[3] Kraft, K.H.: Störimpulse auf gekoppelten Leitungen. International Symposium on Electromagnetic Compatibility, Magdeburg 1999.

[4] Bockelmann, D.E.; Eisenstadt, W.R.: Combined differential and commonmode scattering parameters: Theory and simulation. IEE Trans. Microwave Theory Tech., Vol. 43, S. 1530 bis 1539, (1995).

[5] Bockelmann, D.E.; Eisenstadt, W.R.: Pure-More Network Analyzer for Onwafer Measurements of Mixed-Mode S-Parameters of Differential circuits. IEEE Trans. Microwave Theory Tech., Vol 43, S. 1071 bis 1077, (1997).

[6] Feldberechnungsprogramm EMCSTUDIO von EMCOS.

[7] Frei, S.; Jobava, R.; Karkashadze, D.; Gheonjian, A.; Yavolovskaya, E.: Calculation of Low Frequency EMC Problems in Large Systems with a Quasi-Static Approach. IEEE-Symposium 2004, Santa Clara.

Eine Grafik, die die Speicher-Transaktionen über der Zeit darstellt, kann genutzt werden, um die Spitzenzeiten der Speicherauslastung und die Lösungsansätze für eine bessere Speichernutzung anzuzeigen (Bild 3, Mitte). Diese Darstellungsweise eignet sich auch für die Anzeige der Lese-, Schreib- und Befehlsaufrufspeicherzugriffe des ARM-Prozessors und für eine detaillierte Anzeige der Treffer und Fehlzugriffe auf den Befehls- und Daten-Cache. Mit Hilfe dieser Informationen lassen sich die Cache-Größe und die Konfiguration optimieren, um die Ausführung der Firmware zu beschleunigen und die Belastung des Hauptspeichers durch die CPU zu minimieren. Werden die Speicher-Transaktions- und Software-Profil-Graphen in Kombination verwendet, kann der Zusammenhang zwischen Speicherengpass und der Firmware bzw. der Funktion, die auf den Speicher zugreift, ermittelt werden.

Die Bus-Analyse-Darstellung erleichtert die Beobachtung der Bus-Auslastung und der Bus-Arbitrierung. In modernen SoCs ist Busbandbreite besonderes wichtig, da Prozessoren, DMA-Controller, Peripherieelemente und Datensuch-Engines um diese Ressource konkurrieren. Eine Anzeige, bei der die Busbelastung gegenüber der Zeit aufgetragen und auf 100 % normiert ist, macht bandbreitenlimitierte Operationen sichtbar. Tritt dies auf, kann der Anwender Änderungen zur Behebung des Bandbreitenengpasses unter Zuhilfenahme der entsprechenden Software-Profil-Darstellung vornehmen. Letztere zeigt ihm an, welche Funktionsaufrufe während des Bandbreitenengpasses auftreten.

Ein Bus-Arbiter steuert den Zugriff auf einen bestimmten Bus. Seamless kann eine Grafik erzeugen, welche die Wartezeit eines Bus-Masters zwischen Busanforderung und Buszuweisung anzeigt. Diese Information kann der Anwender dazu nutzen, das effizienteste Bus-Arbitrierungsschema und die beste Reihenfolge der Funktionsaufrufe für das in Entwicklung befindliche System zu wählen.

| Dr.-Ing. Lorena Diaz Ortega lorena.diaz.ortega@volkswagen.de |

| Prof. Dr.-Ing. Karl Heinz Kraft k-h.kraft@fh-wolfenbuettel.de |

Beschleunigung des Entwicklungsprozesses

Die Gesamtheit dieser leistungsfähigen Werkzeuge bildet zusammen mit den Anbindungsmöglichkeiten an andere skalierbare Verifikations-Tools eine intuitive und leistungsfähige Umgebung für Schaltungseingabe, Verifikation und Analyse von ARM-basierten Designs. Durch die Bereitstellung von Werkzeugen, die alle Phasen des Designs und der Verifikation der System-Hardware und der System-Software abdecken, sorgt Mentor Graphics für eine Verkürzung der Systementwicklungszeiten, sodass das optimale Design erreicht und das Projektrisiko reduziert werden kann.

Autor

Jim Kenney ist Product Marketing Manager bei der Mentor Graphics Corp. in Wilsonville, Oregon, USA.

Alfred Goldbacher, Elektronik SoC

Feldberechnung für verschiedene Pinkombinationen

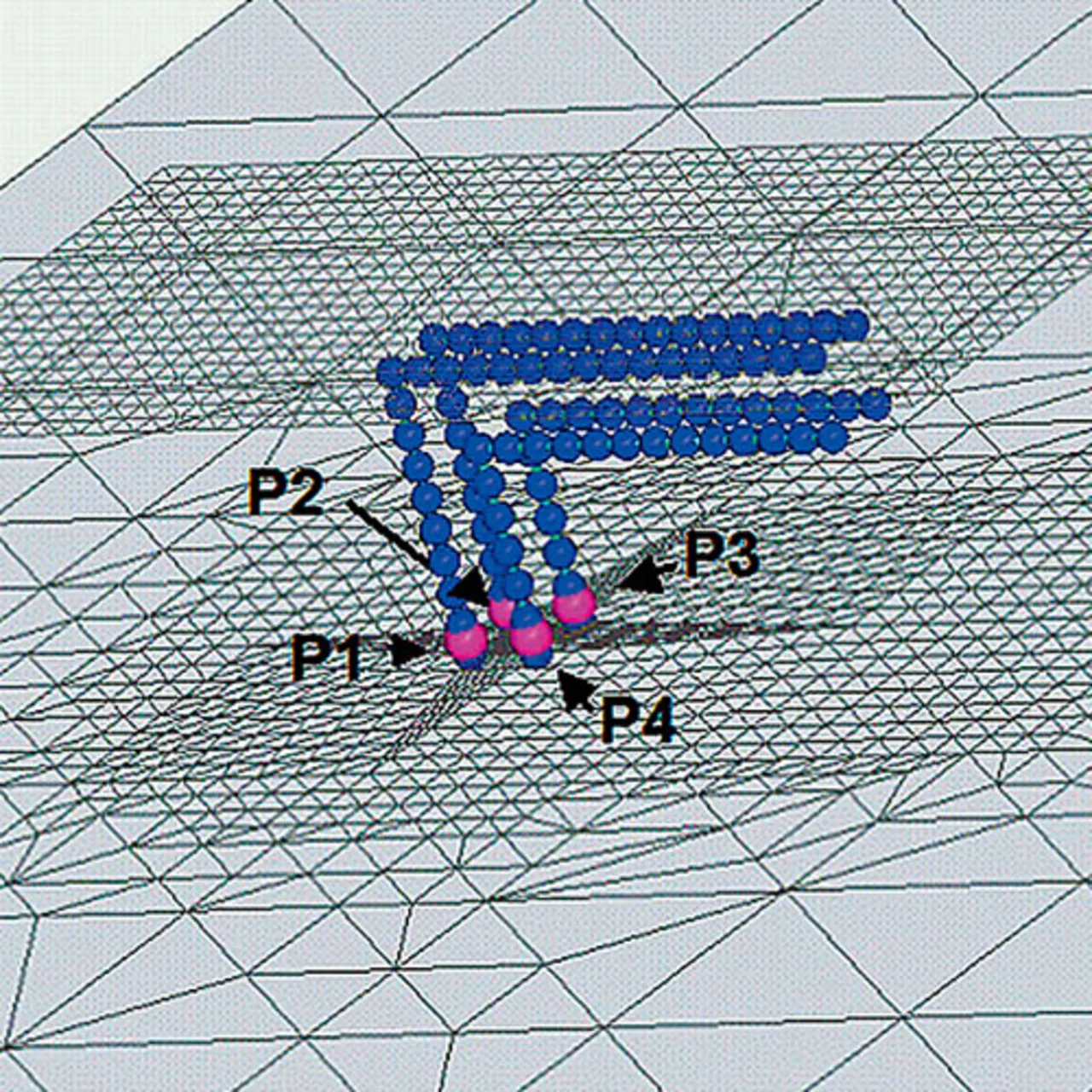

Zur Untersuchung der geeigneten Pinbelegung des FlexRay-Steckers wird das abgestrahlte Feld für verschiedene Pinkombinationen des Steckers berechnet. Als erster Schritt wird der Stecker als geometrisches Netz nachgebildet. Bild 2 zeigt die dreidimensionale Modellierung des Steckers, welcher vier Pins (zwei BP und zwei BM) enthält, die über einer Massefläche liegen. In diesem Fall werden zwei Szenarien (Bild 3) untersucht:

- EMV-Untersuchungen an einem FlexRay-Steckermodell

- „Mixed-Mode-Streuparameter“

- Verifikation und Analyse des Designs mit Seamless

- Als Gantt- oder als Balkendiagramm darstellbar

- Literatur

- Modellierung der Schaltung