Einfluss der Pinbelegung auf Symmetrie und Störabstrahlung

EMV-Untersuchungen an einem FlexRay-Steckermodell

Fortsetzung des Artikels von Teil 2

Verifikation und Analyse des Designs mit Seamless

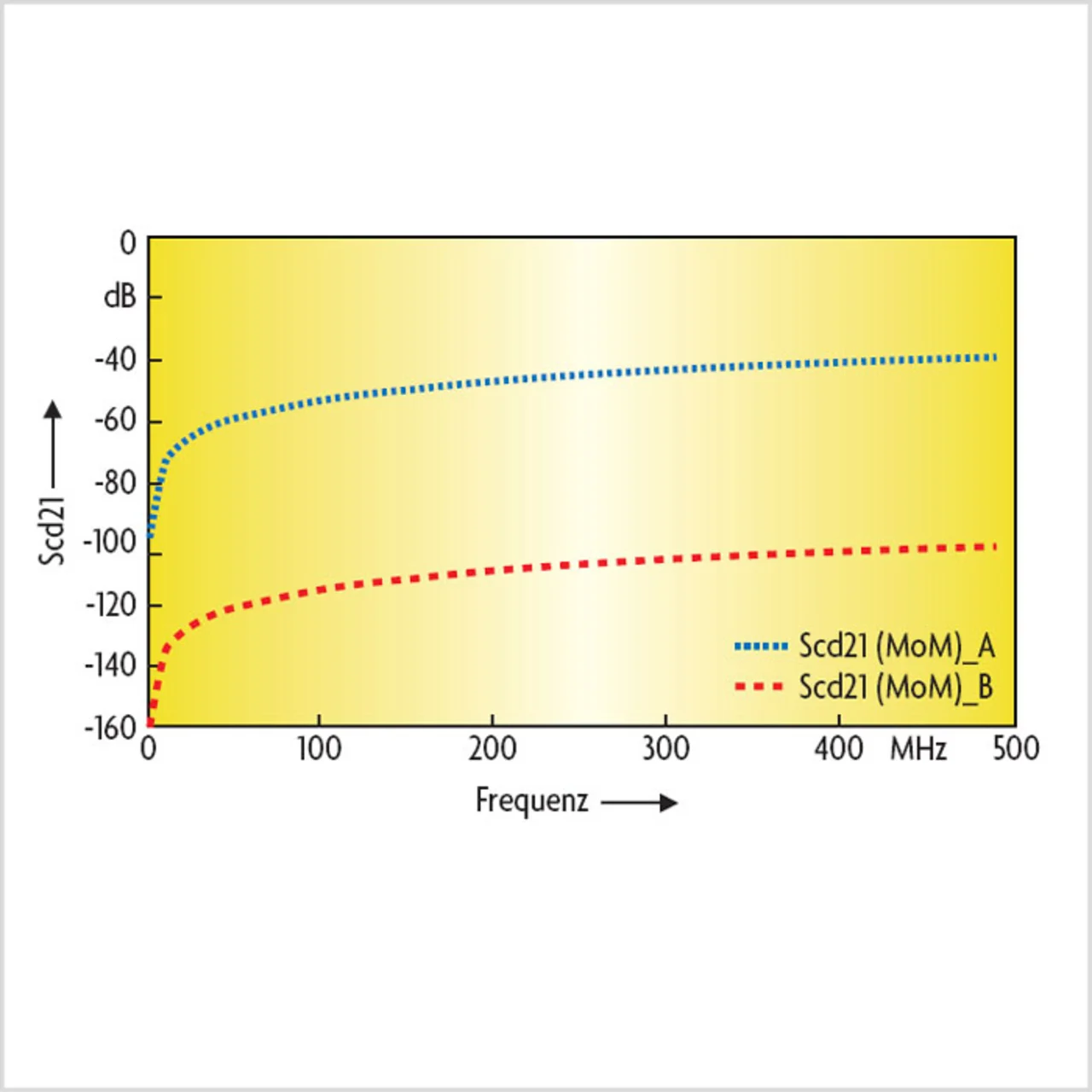

Nach einer erfolgreichen Modellierung des FlexRay-Steckers lassen sich weitere Untersuchungen mittels der Simulation durchführen. Bild 7 zeigt die MoM-Simulationsergebnisse des Scd21-Streuparameters bei Variante A und B. Man sieht in diesem Fall, dass die gekoppelte Gleichtaktwelle in den benachbarten Pins bei Variante A deutlich höher ist als bei Variante B. Die hinreichenden EMV-Simulationsergebnisse zeigen, dass es hohe Anforderungen zur Vermeidung von Störemissionen und zur Erhöhung der Störfestigkeit des FlexRay-Systems bei Schaltungsunsymmetrien gibt.

Zur Bewertung der zwei verwendeten Simulationswege sind Aspekte wie die Komplexität in der Modellierung des Systems, die Berechnungszeit, die Flexibilität bei der Analyse hinsichtlich Änderung und Anwendung neuer Komponenten zu betrachten. Die MoM-Simulation ist im Vergleich mit der Schaltungssimulation sehr zeitaufwendig und hat den Nachteil, dass bei Änderung der Geometrie des Systems eine komplett neue Berechnung erforderlich ist. Dagegen lässt sich die Schaltungsanalyse nach der Extraktion der Ersatzschaltung des Systems durch den „3D-Static-Solver“ in einer annehmbaren Zeit realisieren.

Nach der Eingabe bzw. Modifizierung des Embedded-Systems kann der Entwickler mit der Hardware/Software-Co-Verifikationsumgebung Seamless bereits vor dem Vorliegen eines physikalischen Musters einen virtuellen Prototyp der ARM-Plattform erstellen. Durch die Ausführung der Embedded-Software auf simulierter Hardware lassen sich Fehler im Zusammenspiel von Hardware und Software schon sehr früh im Entwicklungsprozess erkennen. Dies reduziert die Wahrscheinlichkeit, dass ein Fehler erst bei der Systemintegration mit der endgültigen Software entdeckt wird, was zusätzliche Zeit für die Fehlerbehebung und damit eine verzögerter Fertigstellung des Designs bedeuten würde. Seamless sorgt dafür, dass dem Entwickler eine umfassende Darstellung und die vollständige Kontrolle der Hardware- und Software-Ausführung zur Verfügung stehen. Dies beschleunigt den Debugging-Vorgang, der sich häufig beim abschließenden Systemdesign als limitierender Faktor erweist.

Dynamische Optimierung

Bei der Hardware/Software-Co-Verifikation entscheidet die Menge des Codes, die auf der virtuellen Hardware ausgeführt werden kann, über den Nutzwert der Verifikation. Während der Programmausführung erzeugt ein ARM-Embedded-Prozessor mehrere Millionen Speicherzugriffe, die sowohl Befehlsaufrufe wie auch Speicherschreib- bzw. -lesezugriffe umfassen. Mehrere Millionen an Transaktionen mit einem Logiksimulator zu bewältigen, der mit 10 bis 20 Takten pro Sekunde arbeitet, würde mehrere Tage dauern. Das Booten des Echtzeit-Betriebssystems LynxOS benötigt 16,8 Mio. Speichertransaktionen. Bei einer Geschwindigkeit von 20 Takten pro Sekunde würde sich der Bootvorgang von LynxOS über einen Zeitraum von 9,7 Tagen hinziehen. Seamless schafft diese Aufgabe Dank einer patentierten Technologie in etwa zwei bis drei Minuten.

Seamless enthält den Coherent Memory Server, ein einzigartiges Speicher-Array für den Speicheraum, auf den der ARM-Prozessor häufig zugreift. Der Anwender kann wählen, ob der Logiksimulator den Zugriff auf einen bestimmten Speicherbereich bedient oder ob diese Aufgabe Seamless übernehmen soll. Beide Möglichkeiten resultieren in einem Zugriff auf das gleiche Speicher-Array, nur dass Seamless eine Anfrage 10 000-mal schneller abarbeiten kann als ein Logiksimulator.

Der Anwender kann jederzeit während der Simulation zwischen den Speicherzugriff-Modi wechseln, um je nach Situation entweder eine detaillierte Simulation der Speicherzyklen oder eine schnelle Programmausführung zu erreichen. Am Anfang des Designprozesses ist es beispielsweise wichtig, die Funktion des Speichersubsystems des Designs zu überprüfen, um das Hochfahren des physikalischen Prototyps im Labor sicherzustellen. Ist die Simulation einer gewissen Zahl von Zugriffszyklen abgeschlossen, können die Speicheroptimierungen von Seamless aktiviert werden, um die Ausführung zu beschleunigen. Soll ein Bereich z.B. wegen eines Problems näher untersucht werden, das erst im Laufe einer längeren Simulation auftritt, können die Seamless-Optimierungen genutzt werden, um schnell zu der interessanten Stelle zu gelangen. Sie können dann für eine detaillierte Simulation deaktiviert werden, um das Problem zu lokalisieren.

Da die Speicherinhalte nur an einer zentralen Stelle (Coherent Memory Server) abgelegt werden, ist die Datenintegrität gewährleistet, unabhängig davon, welche Betriebsart genutzt und wie häufig zwischen diesen Zugriffsmethoden gewechselt wird. Der Coherent Memory Server unterstützt Multi-Prozessor-Designs, Prozessoren mit mehreren Speicherbereichen und eine breite Palette an Speichermanagementtechniken. Seamless nutzt mehr als 4000 Denali-Speichermodelle. Innerhalb von Seamless nicht verfügbare Modelle können einfach aus dem Verilog- oder VHDL-Quellcode in ein Seamless-Modell überführt werden. Die Umwandlung erfordert keine Änderungen des Embedded-Codes des Systems.

Prozessor-Support-Modelle

Mentor Graphics ist weiterhin der führende Anbieter von ARM-Prozessor-Co-Verifikationsmodellen und kooperiert mit ARM bei der Entwicklung leistungsfähiger, besonders präziser Lösungen. Seamless umfasst Processor Support Packages für die Prozessorfamilien ARM7, ARM9, ARM9E, ARM10 und ARM11. Zu jedem Prozessormodell gehören drei Komponenten: ein Instruction Set Simulator (ISS), ein grafischer Software-Debugger und ein Bus Interface Model (BIM), das die Interaktion von Seamless und der Logiksimulationsumgebung ermöglicht, die die Hardware-Beschreibung in Verilog, VHDL oder SystemC ausführt.

C-Model-Support

Die „Seamless C-Bridge“-Technologie unterstützt die C-Hardware-Modellierung und bietet so den Zugang zu den Vorteilen der gegenüber HDL-Modellen höheren Simulationsgeschwindigkeiten von C-Modellen. Ein einfaches API stellt die Verbindung zwischen Seamless und den C-Modellen her. Entwickler können entweder mit einer reinen C-Hardware-Modellierungsumgebung oder mit einer Mischung aus C- und HDL-Designbeschreibungen arbeiten. Die C-Hardware-Modelle können in C, C++ und SystemC implementiert sein.

Wenn sich ein Design-Team entscheidet, Teile oder die ganze Hardware in C zu modellieren, muss es einmal den Übergang zu HDL durchführen und das Design vor dem Tape-out erneut verifizieren. Seamless C-Bridge ist dafür ein optimales Tool. Es unterstützt eine einfache Integration von C-Hardware-Beschreibungen und ermöglicht durch eine simple Änderung in der Memory Map den Wechsel zwischen einem C- und einem HDL-Modell für eine bestimmte Funktion.

Performance-Analyse

Ein wichtiges Feature von Seamless liegt in der Möglichkeit, Metriken von performancekritischen Daten grafisch aufbereiten zu können. Diese Funktion erlaubt es dem Anwender, Leistungsengpässe grafisch darzustellen und die Auswirkungen von Designmodifikationen zur Beseitigung dieser Engpässe zu verstehen. Seamless bietet Software-Profiling-, Speicher-Transaktions- (einschließlich Cache-Analysen) und Bus-Transaktionsdarstellungen an sowie eine Darstellung der Verzögerungen der Bus-Arbitrierung.

- EMV-Untersuchungen an einem FlexRay-Steckermodell

- „Mixed-Mode-Streuparameter“

- Verifikation und Analyse des Designs mit Seamless

- Als Gantt- oder als Balkendiagramm darstellbar

- Literatur

- Modellierung der Schaltung