Chipsatz für die Punkt-zu-Punkt-Datenübertragung im Auto mit 1 Gbit/s

Datenautobahn für Multimedia auf vier Rädern

Fortsetzung des Artikels von Teil 1

Videovernetzung im Auto

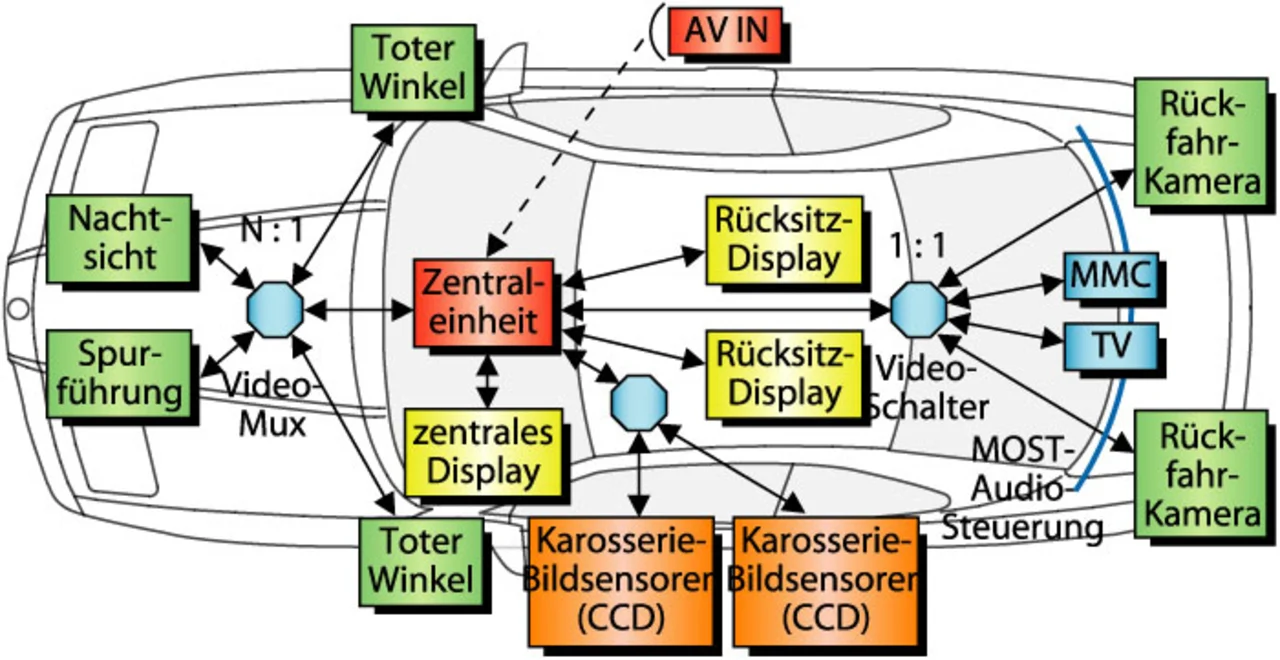

Neben den reinen Display-Links etwa für Armaturenbrett, „Head-Up“-Display und Rücksitz-Displays wird es im Auto auch zahlreiche Kamera-Links als Teil moderner Assistenz-Systeme geben. Wie ein solches Netzwerk-Konzept aussehen könnte, zeigt .

Eine wesentliche Anforderung solcher Video-Netzwerke ist das flexible Routing und die Verteilung der Grafiksignale an verschiedene Stellen, oft quer durch das ganze Fahrzeug. So besteht etwa bei der Rückfahr-Kamera der Wunsch, die Bildinformation nicht nur auf den Rechner zur Objekt-Erkennung zu übertragen, sondern das Bild auch dem Fahrer im Display des Armaturenbretts anzuzeigen. Auch die 3D-Grafiken moderner Navigationssysteme mit ihrer Fülle an Informationen sind längst nicht mehr nur für den Fahrer interessant, mehr und mehr finden auch die Passagiere im Fonds Gefallen an diesem Programm. Hier bahnt sich ein ähnlicher Trend wie im Flugzeug an, wo die aktuellen Informationen über Route, Position, Flughöhe und Ankunftszeit längst zu den meist gesehenen „Video-Programmen“ gehören.

Gerade diese Anwendungen – Auskopplung und Verteilung von Videosignalen über mehrere Stufen – ist mit synchronen Taktsystemen nicht zu lösen. Mit dem ursprünglichen Pixel-Takt als Referenz verschlechtert sich die Signalqualität mit jedem Segment, da sich Verzerrungen im Kabel und der Jitter der kaskadierten PLLs über die einzelnen Teilsegmente akkumulieren, bis an einer Stelle ein Empfänger das bitserielle Signal nicht mehr eindeutig erkennen kann. Bildaussetzer oder Instabilitäten im Netzwerk sind die Folge.

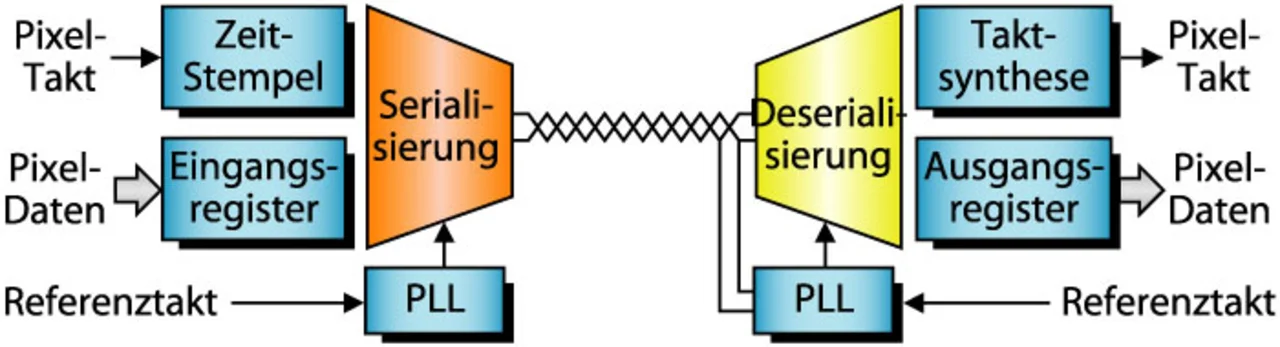

Anders beim asynchronen Taktsys-tem des APIX-Links, das sich in gleicher Form schon beim GigaSTaR mehr als bewährt hat: Der ankommende Pixel-Takt, egal ob von einer Grafikkarte oder einem vorgeschalteten Videolink, wird nicht als Referenz für die weitere Taktaufbereitung verwendet, sondern dient nur als Bezugswert für die ankommenden Videodaten. Dessen Qualität – Signalform und Jitter – wirkt sich daher nicht auf nachfolgende Stufen aus, da im Taktsystem des APIX ein „neuer“, sehr genauer und praktisch jitterfreier Pixel-Takt für die ausgehenden Pixeldaten synthetisch generiert wird (Bild 5).

Einsatzmöglichkeiten bis hin zur Medizin- und Sicherheitstechnik

Selbst mit komplexeren Video-Netzwerken sind die Möglichkeiten der neuen APIX-Technologie längst nicht erschöpft. Seine Fähigkeit, einen Datenstrom in Echtzeit, mit niedriger Latenzzeit und – anders als beim Ethernet – kontinuierlich zu übertragen, eröffnet die Möglichkeit, neben den eigentlichen Videodaten auch andere Daten praktisch „huckepack“ und ohne Zwischenspeicher mit zu übertragen. Alleine die integrierten Seitenband-Kanäle mit ihrem 2-bit-Interface bieten ei-ne Bandbreite von bis zu 24 Mbit/s im Downlink und bis zu 18 Mbit/s im Uplink; ausreichend Kapazität, um andere Bus-protokolle mit niedrigeren Bitraten über den gleichen „Physical Layer“ zu übertragen, der im Falle des APIX-Bausteins nichts anderes als ein dünnes, hochflexibles Kupferkabel mit einem oder zwei Leitungspaaren sein kann.

Die Einsatzbereiche des APIX gehen über das Fahrzeug hinaus. Seit der ersten öffentlichen Vorstellung auf der „Embedded World“ in Nürnberg zeigen sich immer neue Anwendungsbereiche für diese Produkte: Medizin-Ausrüster etwa wollen den APIX bei neuen Endoskopen einsetzen, bei denen der kleine Chip – APIX misst gerade mal drei Quadratmillimeter – direkt mit dem Kamera-Sensor in der Endoskop-Spitze verbunden wird und die Signale über ein dünnes, flexibles Kabel direkt zum Computer leitet. Auch die Sicherheits-Indus-trie ist an dem Produkt interessiert: Mit APIX können Kamera-Bilder erstmals pixelgenau übertragen und mit entsprechender Objekterkennungs-Software präzise ausgewertet werden. Selbst Hersteller von „weißer Ware“ denken darüber nach, in ihre Haushaltsgeräte kleine Displays einzubauen, die über APIX bidrektional an den eingebauten Minicomputer angebunden werden.

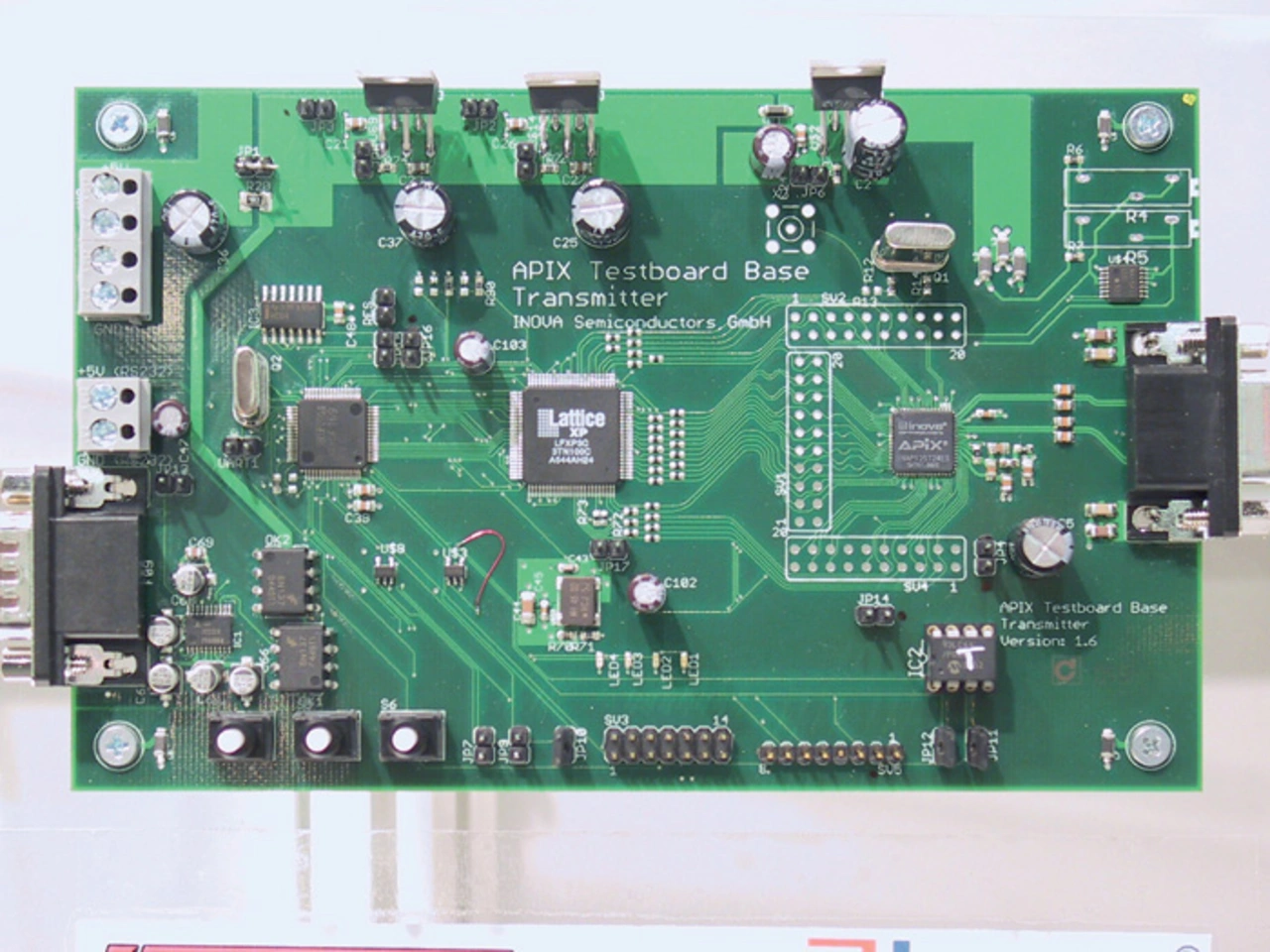

Last but not least, interessiert sich auch die Handy-Industrie für dieses Konzept. Auch wenn es hier nicht um Entfernungen von 10 bis 15 Metern geht, sondern eher um 10 bis 15 Zentimeter, wird bei modernen Klapp-Handys die Verkabelung immer besser auflösender Displays und Kameras inzwischen zum Thema. Die APIX-Bausteine sind in Musterstückzahlen bereits verfügbar; zur Erleichterung der Entwicklungsarbeit gibt es eine Evaluierungs-Plattform mit PC-Anbindung (Bild 6).

| [1] | Paper von ERTICO: Open Architecture For An Automotive Multimedia Bus System. A Strategy For Convergence. August 1999, www.ertico.com |

| [2] | The Hansen Report On Automotive Electronics, www.hansenreport.com |

| [3] | Kraus, R.: Schneller, weiter und sicherer. Der GigaSTaR-Link – Hohe Datenraten störsicher übertragen. Elektronik 2002, H. 7, S. 48ff. |

| [4] | Kraus, R.: Mit Volldampf durch die Leitung. GigaSTaR – Ein „intelligentes“ Kabel für hohe Datenraten. Elektronik 2000, H. 2, S. 48ff. |

| [5] | Stelzer, G.: Gigabit-Übertragung auf vier Rädern. Elektronik automotive 2006, H. 1, S. 28f. |

Dipl.-Ing. Robert Kraus ist Mitgründer und Geschäftführender Gesellschafter der Inova Semiconductors GmbH. Nach dem Studium der Nachrichtentechnik begann er im Jahre 1986 seine berufliche Karriere als Produkt-Ingenieur bei Motorola Halbleiter (heute Freescale Semiconductor) in München. Nach verschiedenen Stationen im Bereich Produkt-, Manufacturing-, Applikations- und Design-Engineering für Logik Produkte leitete er ab 1990 sämtliche Logik-Engineering-Aktivitäten in Europa. In diesen Jahren entstanden auch die ersten Konzepte für hochbitratige serielle Bausteine, erste Produkte folgten dann im Jahre 1994. Nach dem Fall der Mauer war er darüber hinaus auch verantwortlich für den Aufbau von Design-Zentren und strategischen Kooperationen mit Halbleiter-Herstellern in Osteuropa. Ab 1997 leitete er als Senior Manager die weltweiten System-Engineering-Aktivitäten der Transportation Business Unit, die neue Standard-Logikprodukte für den Automotive-Bereich definierte und entwickelte. Nach 14-jähriger Tätigkeit verließ er Motorola dann Anfang 1999, um die Inova Semiconductors aufzubauen.

rkraus@inova-semiconductors.de

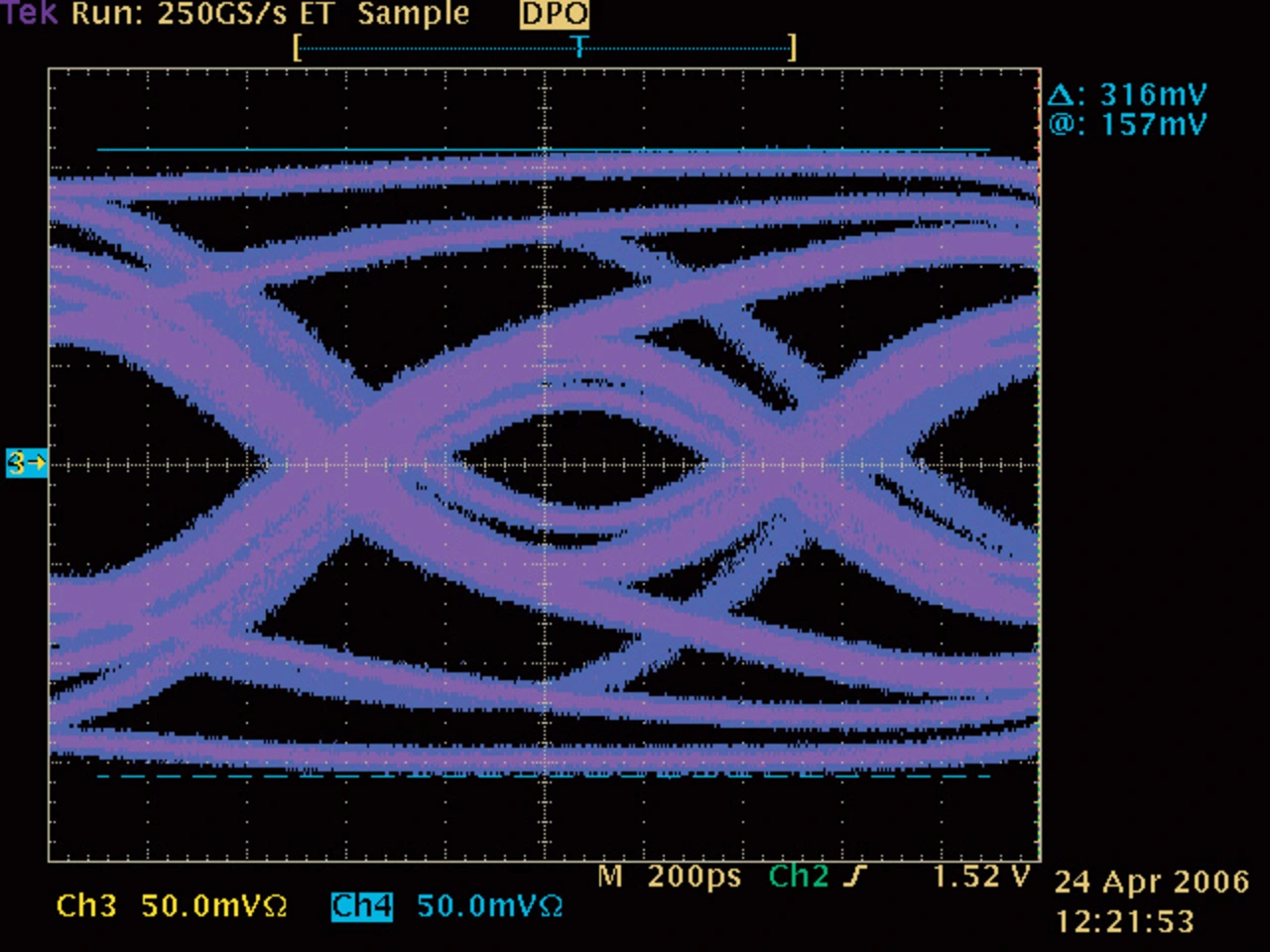

Der von Grund auf neu entwickelte Transceiver ist das eigentliche Kernstück der APIX-Bausteine. Hier werden neue Schaltungstechniken umgesetzt – darunter eine völlig neu entwickelte Ausgangsstufe –, die für die Applikation eine Vielzahl von Möglichkeiten eröffnet. Selbst bei maximaler Datenrate, hochkapazitiven Kabeln und großer Entfernung sorgt etwa die fein abstufbare Regelung für Ausgangstrom und Preemphasis (Vorverzerrung) für eine hohe Signalintegrität – eine wesentliche Voraussetzung für die zuverlässige Datenübertragung und optimales EMV-Verhalten.

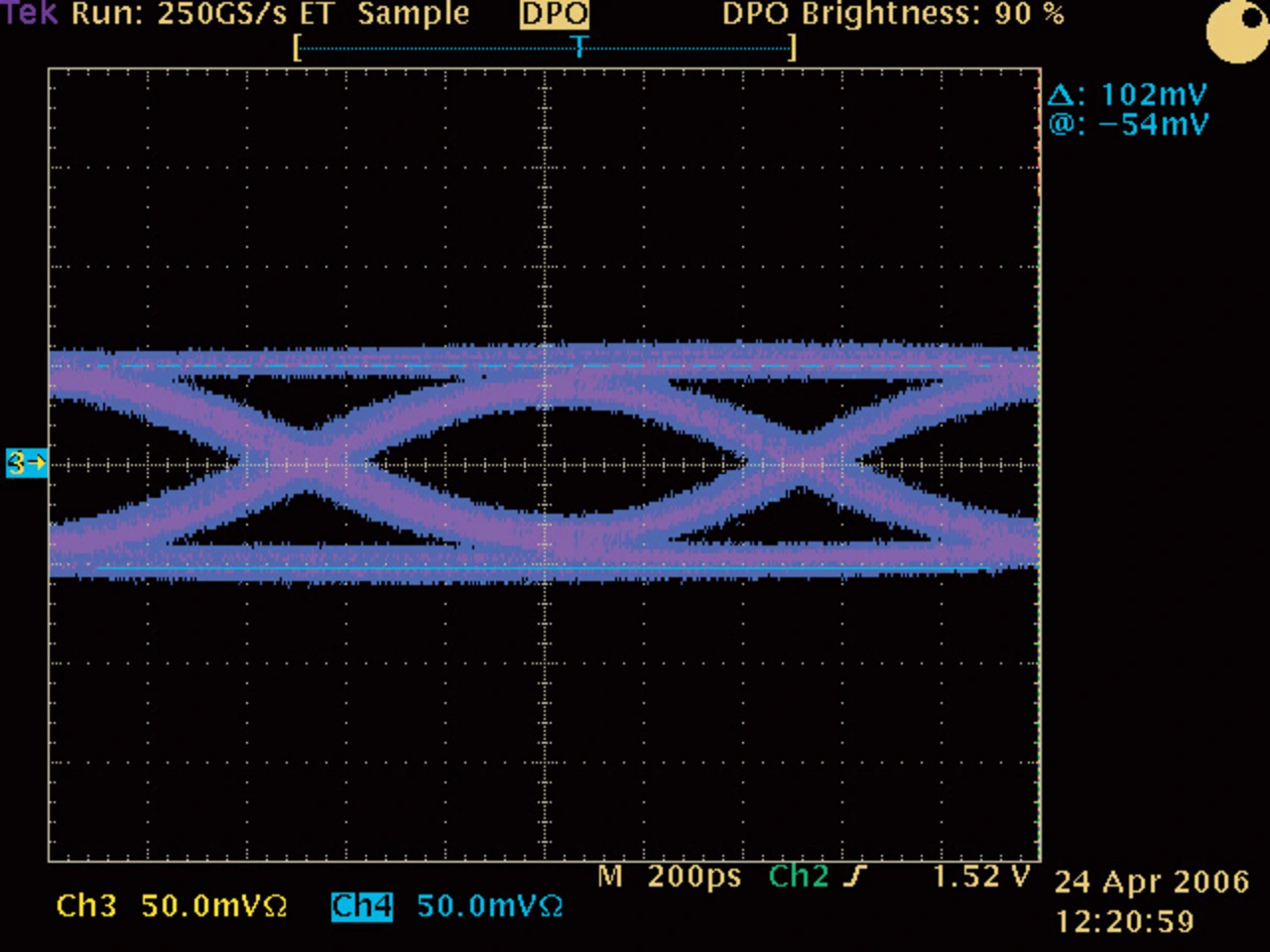

Bild 1 zeigt das Signal der APIX-Ausgangsstufe ohne Preemphasis mit einer Datenrate von 1 Gbit/s am Ende einer 20 m langen verdrillten Zweidrahtleitung (Twisted Pair). Man sieht die extre-me Intersymbol-Interferenz von nieder- und hochfrequenten Signalanteilen, bedingt durch die unterschiedlichen Gruppenlaufzeiten. Der gesamte Spannungshub des Signalgemisches beträgt über 300 mV, wobei als echter Nutzpegel nur 50 mV zur Verfügung stehen. Hohe Interferenzen bzw. Modulationsprodukte sorgen für schlechte EMV-Werte, von Signalintegrität kann hier kaum noch gesprochen werden.

Bild 2 zeigt den gleichen Aufbau (1 Gbit/s Datenrate und 20 Meter Kabel), allerdings bei eingeschalteter Preemphasis. Mit optimierter Preemphasis lassen sich die Intersymbol-Interferenzen nahezu eliminieren, für den gleichen Nutzsignalpegel von 50 mV kann jetzt der Spannungshub von über 300 mV auf rund 100 mV abgesenkt werden – ein praktisch perfektes Signal mit optimaler Augenöff-nung bei hoher Signalintegrität.

Die Werte für Preemphasis und Nominalstrom können an den APIX-Bausteinen einfach über Widerstände eingestellt werden; mit einer speziellen Mimik (Mikrocontroller) ist es dank integrierten Rückkanals sogar möglich, eine vollautomatische Einmessung auf das jeweilige Kabel zu realisieren.

Ein schaltbares „Spread Spectrum Clocking“ vervollständigt die Maßnahmen zur EMV-Optmierung: Der serielle Bitstrom kann in bestimmten Grenzen buchstäblich „gewobbelt“ werden, um Frequenzspitzen um bis zu 8 dB im Spektrum zu reduzieren.

Hin- und Rückkanal konfigurierbar

Die APIX-Bausteine sind mit einer konfigurierbaren „Pixel“-Schnittstelle ausgestattet, die sich je nach Anwendung – Display- oder Kamera-Link – als 10, 12, 18 oder 24 bit breite RGB-Schnittstelle mit einem Pixel-Takt von 6 bis 60 MHz und Triggerung auf steigende oder fallende Flanke konfigurieren lässt.

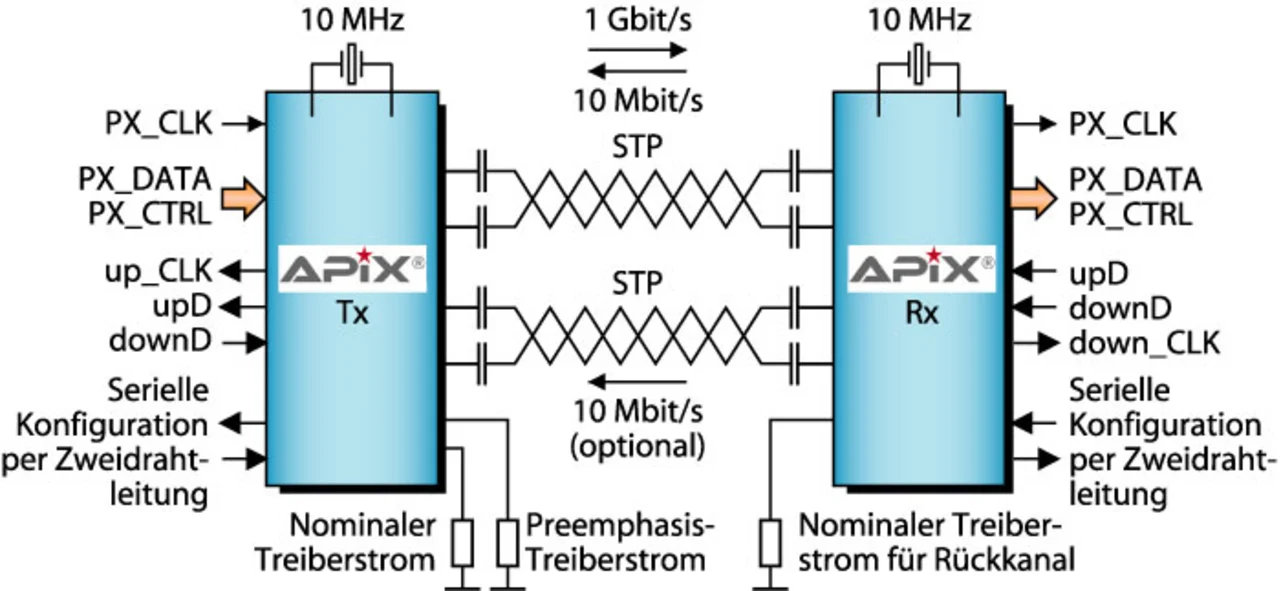

So ist es etwa möglich, über den APIX-Link nicht nur die Pixel-Daten eines abgesetzten Kamera-Sensors mit voller (1 Gbit/s) oder reduzierter Datenrate (0,5 Gbit/s) direkt an die Auswerte-CPU zu übertragen, sondern gleichzeitig auch die Kamera von der CPU aus zu überwachen und zu steuern. Möglich macht dies der fest eingebaute Rückkanal. Dieser überträgt mit bis zu 18 Mbit/s (typisch: 10 Mbit/s) und kann alternativ als im Hinkanal eingebetteter Link (= bidirektionale Übertragung über ein Adernpaar) oder über ein zweites separates Adernpaar zwischen Sender und Empfänger realisiert werden (Bild 3).

Dieser Seitenband-Kanal existiert nicht nur für den Rückkanal (Uplink). Auch der „Downlink“ bietet neben dem eigentlichen Pixeldaten-Interface eine weitere 2 bit breite Schnittstelle, über die Daten mit bis zu 12 Mbit/s parallel, aber unabhängig vom Pixelstrom übertragen werden können.

Der Baustein bietet auch die Möglichkeit, bestimmte Fehlerzustände wie etwa Übertragungsfehler, PLL-Störungen etc. über einen konfigurierbaren „Error-Pin“ gezielt auszugeben: eine wichtige Funktion bei der Erprobung komplexerer Systeme oder bei extremen Fahrzeugtests, bei denen die Ingenieure keine entsprechenden Messgeräte zur Verfügung haben.

Kernstück der APIX-Bausteine ist allerdings ein lokales Taktsystem, wie es in ähnlicher Weise auch im GigaSTaR verwendet wird. Anders als bei parallelen- oder auch bitseriellen LVDS-Lösungen wird hier nicht der Pixel-Takt der Grafikkarte oder der Kamera verwendet, um mit Hilfe einer PLL die erforderlichen internen Taktsignale zu erzeugen (synchrones Taktsystem). Bei APIX sorgt ein eingebauter 10-MHz-Taktoszillator, der durch einen externen Quarz getriggert wird, für einen hochstabilen Systemtakt, der unabhängig von der Qualität des angelieferten Pixel-Takts alle erforderlichen Taktsignale mit hoher Stabilität erzeugt. Voll zur Geltung kommt diese Lösung, wenn im Auto nicht nur kurze Punkt-zu-Punkt-Strecken überbrückt, sondern komplexere Systemstrukturen realisiert werden müssen: In den nächsten Jahren werden die Fahrzeug-Hersteller ihre Autos nicht nur mit einzelnen Video-Links, sondern mit kompletten Video-Netzen ausstatten.

- Datenautobahn für Multimedia auf vier Rädern

- Videovernetzung im Auto

- GigaSTaR stand Pate