Die verfügbare Rechenleistung optimal nutzen

Effiziente Implementierung einer Verkehrszeichen-Erkennung

Fortsetzung des Artikels von Teil 3

Prozessorkerne als „Arbeitsbienen“

Die Prozessorkerne steuern das Software-Gerüst und führen die mathematischen Berechnungen durch. Jeder Prozessorkern verfügt über zwei Recheneinheiten, die bis zu vier Berechnungen zeitgleich ausführen können. Wie bereits angeführt, hat der hier verwendete Prozessor zwei Kerne. Es können also bis zu acht Berechnungen ausgeführt werden. Parallel dazu können Lese- und Schreiboperationen angehängt werden. Diese holen die zur Berechnung benötigten Daten aus dem Speicher und legen die Ergebnisse wieder dort ab. Im Kasten ist als Beispiel 1 eine Anweisung mit maximaler Breite gezeigt. Sie erlaubt es, pro Prozessorkern zwei unabhängige Multiplikationen mit anschließender Akkumulation plus zwei Ladevorgänge zeitgleich auszuführen. Kann dies aus Gründen von Adresskonflikten nicht eingesetzt werden, sind auch Bruchteile dieser parallelen Anweisung möglich (Beispiel 2 im Kasten). In eingeschränktem Umfang können diese Anweisungen auch variiert werden.

Prozessor-DMA-System regelt den „Verkehr“

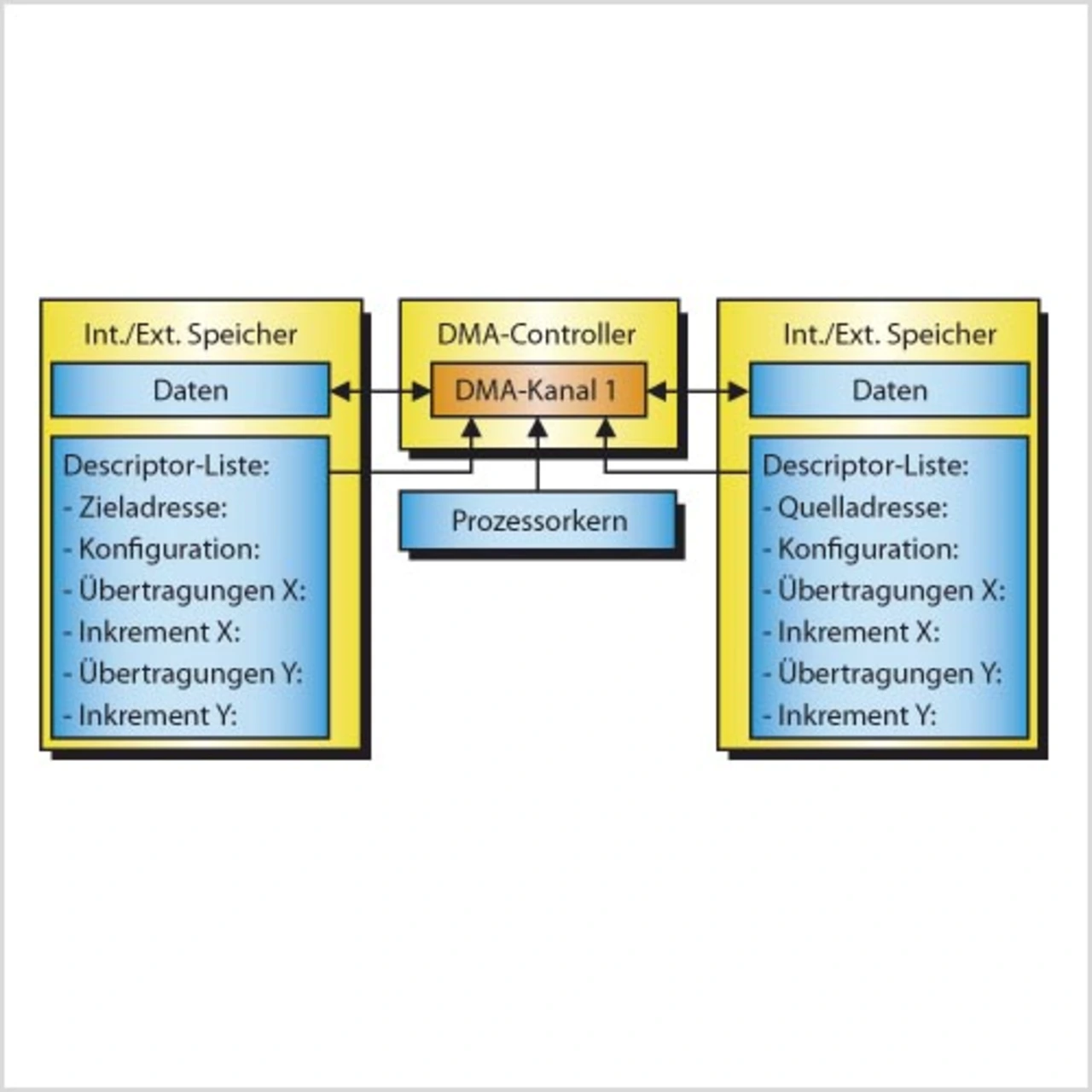

DMA-Kanäle sorgen dafür, dass Daten aus dem internen oder externen Speicher übertragen und bei Bedarf neu organisiert werden können. Da die Aktionen der Kanäle unabhängig vom Rechenkern ausgeführt werden, kann die Übertragung der Folgedaten bereits während der Berechnung der momentanen Daten stattfinden: Das spart Zeit. Es dürfen sogar mehrere DMA-Kanäle zeitgleich arbeiten, selbst wenn sie auf den gleichen Speicher zugreifen. Eine interne Logik stellt die Synchronisation der Kanäle sicher. Wie Bild 3 zeigt, wird die Übertragung durch das Beschreiben von minimal zwei Registern des DMA-Controllers aktiviert. Dies führt dazu, dass der DMA-Controller eine zuvor angelegte Beschreibungsliste (Descriptor Liste) einliest. Diese beschreibt die auszuführenden Aktivitäten. So enthält sie zum Beispiel eine Ziel- oder/und Quell-Adresse der Daten sowie die Anzahl der zu übertragenden Elemente und mögliche Adresssprünge, falls nur kleine Bildausschnitte übertragen werden sollen. Durch die Nutzung des DMA-Controllers können Übertragungen von mehreren hundert Megabyte durch Beschreiben von nur zwei Registern gestartet werden.

Prozessorspeicher nach Ebenen unterteilt

Der Blackfin-Prozessor unterteilt seinen Speicher in drei Ebenen (Level): Der Level-Eins-Speicher (L1) wird hierbei mit der Taktrate des Prozessorkerns betrieben und kann, abhängig vom verwendeten Derivat, Werte bis 600 MHz erreichen. Damit wird sichergestellt, dass der Prozessor Anweisungen, die das Laden von Daten aus dem Speicher beinhalten, in einem Takt ausführen kann. Level-Zwei-Speicher (L2) wird mit halber Taktrate des Prozessorkerns betrieben. Folglich werden mindestens zwei Prozessortakte benötigt, um Daten zu laden. Als Level-Drei-Speicher (L3) schließlich bezeichnet man den externen Speicher, der im Falle eines SDRAMs mit bis zu 133 MHz getaktet wird. Der Zugriff auf diesen Speicher benötigt also mehrere Prozessortakte. Es liegt auf der Hand, dass die zeitkritischsten Daten und Anweisungen stets im schnellsten Speicher liegen sollten.

Die zentrale Einheit des Systems bildet der Blackfin-Prozessor von Analog Devices (www.analog.com). Dieser wurde für die Bildverarbeitung entwickelt und enthält spezielle Recheneinheiten, mit denen man Algorithmen parallel berechnen kann. Da alle benötigten Schnittstellen integriert wurden, kann die Applikation per Software flexibel beschrieben werden.

Für die nachstehend beschriebene Applikation wurde ein Blackfin-Derivat mit zwei symmetrischen Prozessorkernen ausgewählt (Dual-Core-Prozessor). Da mit diesem doppelt so viel Rechenleistung zur Verfügung steht, konnten zusätzliche Erweiterungen implementiert werden. Dazu gehören verschiedene Interfaces wie Videoschnittstellen sowie für den Betrieb in Fahrerassistenzsystemen häufig verwendete Busstandards wie CAN-Bus, I2C-Bus und MOST.

Anweisungs-Beispiele

Beispiel 1:

R4.L=(A0+=R0.L*R1.L), R4.H=(A1+=R0.H*R1.H) || R0=[I0++] || R1=[I1++];

Beispiel 2:

R4.L=(A0+=R0.L*R1.L), R4.H=(A1+=R0.H*R1.H) || R0=[I0++] || NOP MNOP || R0=[I0++] || R1=[I1++];

A0+=R0.L*R1.L || R0.L=w[I0++] || R1.L=w[I1++];

- Effiziente Implementierung einer Verkehrszeichen-Erkennung

- Siehe auch:

- Effiziente Implementierung einer Verkehrszeichen-Erkennung

- Prozessorkerne als „Arbeitsbienen“

- Software-Gerüst als „Steuermann“