Design quasiresonanter Sperrwandler

Nicht nur Verluste minimiert

Geringe Kosten und hohe Zuverlässigkeit sind zwei der wichtigsten Ziele bei der Entwicklung von Schaltnetzteilen. Diese lassen sich mit einer quasiresonanten Topologie erreichen. Dieser Artikel beschreibt die Theorie hinter dieser Architektur und geht auf ihre Vorteile ein – weniger Verluste und geringere Störabstrahlung.

Quasi« bedeutet »teilweise« oder »so in etwa«. Bei der Implementierung eines quasiresonanten Designs wird der vorhandene LC-Schwingkreis in einer PWM-Spannungsversorgung strategisch genutzt. Dies führt dazu, dass die Resonanzeffekte dieses Schwingkreises die Schaltflanken »abschwächen« können.

Diese weniger schnellen Übergänge reduzieren dann wiederum die Schaltverluste und die Störabstrahlung (EMI), welche bei hart schaltenden Wandlern auftreten. Da der Resonanzkreis nur während der Schaltübergänge an einem ansonsten herkömmlichen Rechtecksignalwandler eingesetzt wird, ergab sich der Ausdruck »quasiresonant«.

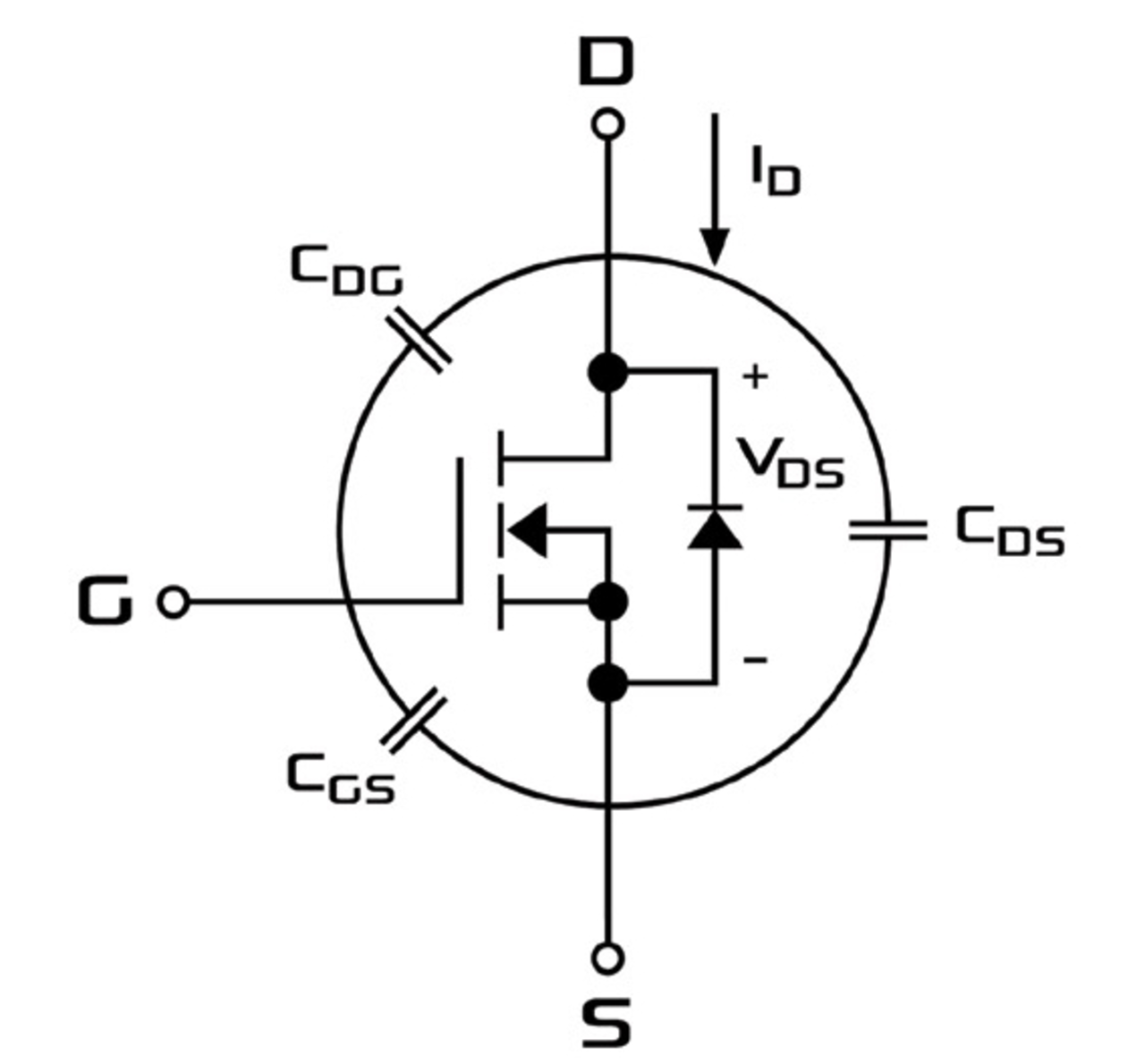

Um diese Topologie verstehen zu können, muss man sich über die parasitären Eigenschaften von MOSFETs und Transformatoren im Klaren sein. Ein MOSFET enthält verschiedene parasitäre Kapazitäten. Diese entstehen primär aus dem physischen Aufbau des Bauteils.

Sie lassen sich mathematisch vereinfacht ausdrücken als Eingangskapazität CISS und Ausgangskapazität COSS. Dabei ist CISS die Summe aus der Gate-Source-Kapazität CGS und der Gate-Drain-Kapazität CGD, COSS die Summe aus der Drain-Source-Kapazität CDS und der Drain-Gate-Kapazität CDG (Bild 1). Bei hart schaltenden Wandlern trägt im Wesentlichen die Ausgangskapazität COSS zu den Schaltverlusten bei.

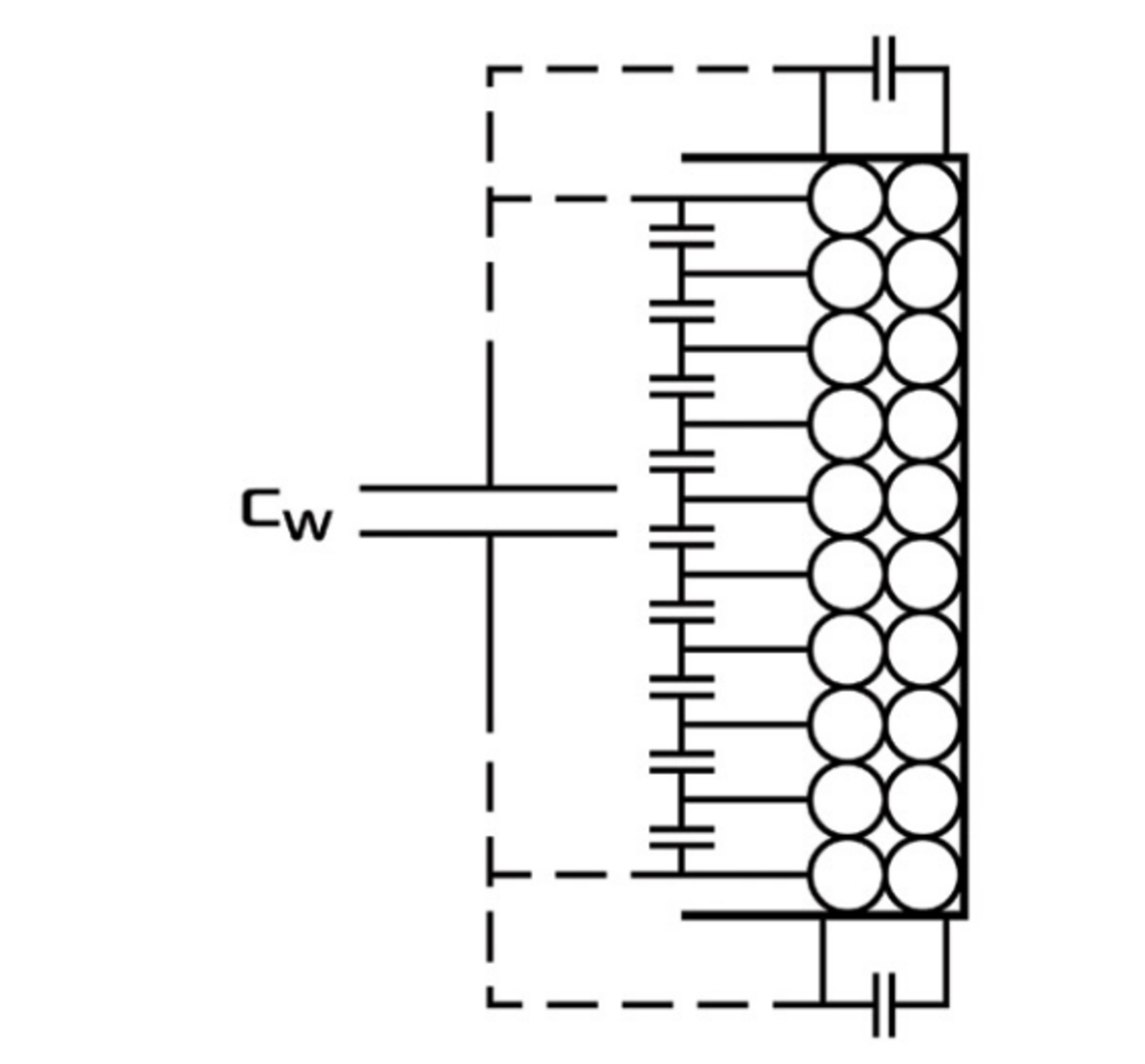

Auch Transformatoren enthalten parasitäre Kapazitäten, zu denen die Wicklungs- und Lagenkapazität gehören. Diese lassen sich zusammen als einzelner Kondensator CW modellieren und tragen ebenfalls zu Schaltverlusten bei hart schaltenden Wandlern bei (Bild 2).

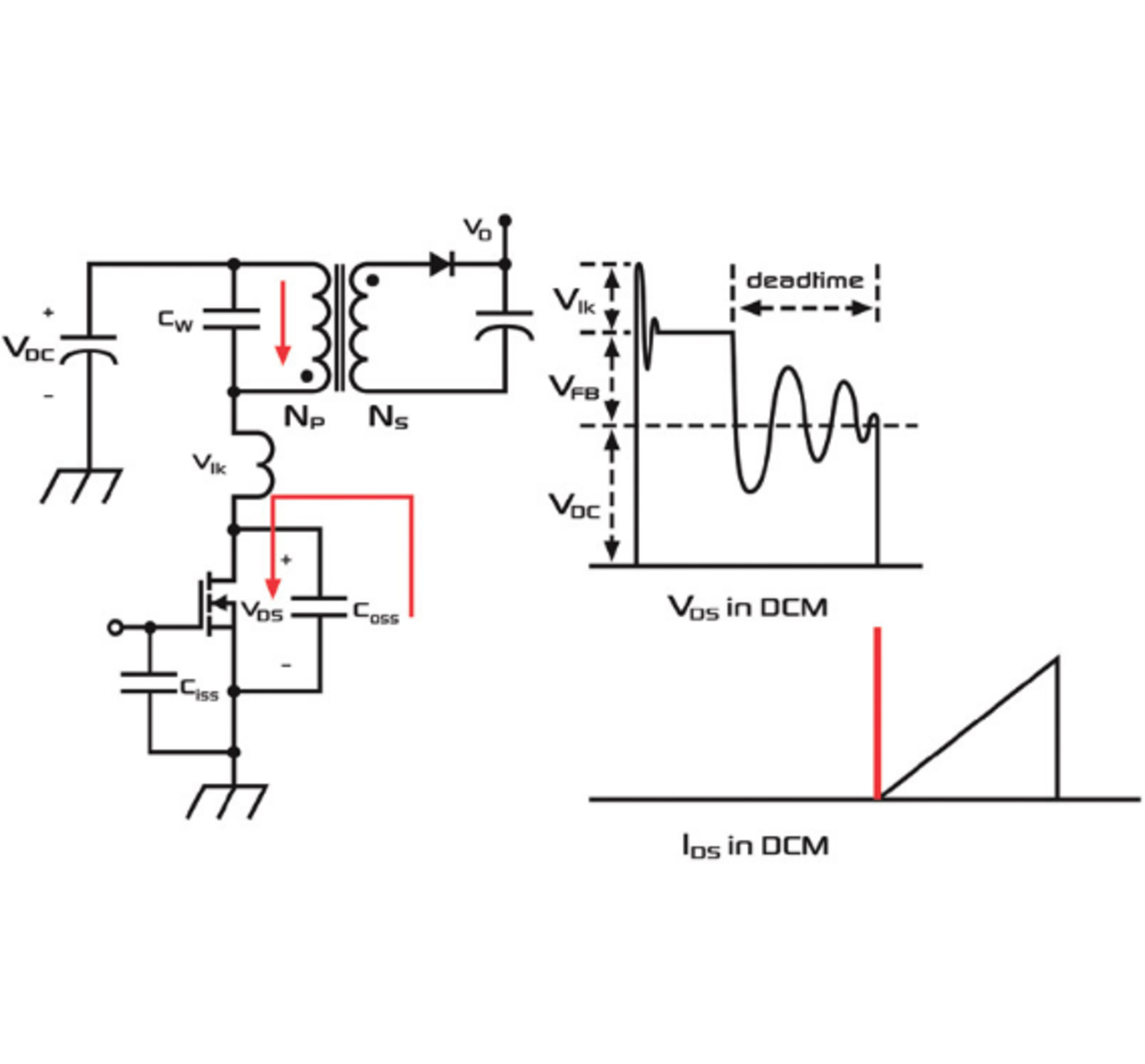

Bild 3 stellt einen herkömmlichen, hart schaltenden Sperrwandler dar. Während der Totzeit im diskontinuierlichen Modus (DCM) schwingt die parasitäre Kapazität mit der primären Induktivität um die Zwischenkreisspannung VDC. Die Spannung an den parasitären Kapazitäten variiert mit der Schwingung, weist aber durchgehend signifikante Werte auf.

Wenn der MOSFET im nächsten Taktzyklus einschaltet, werden die parasitären Kondensatoren COSS und CW über den Transistor entladen und erzeugen dabei eine hohe Stromspitze. Da diese auftritt, wenn am MOSFET eine hohe Spannung anliegt, erzeugt sie Schaltverluste. Darüber hinaus ist die Stromspitze reich an Oberwellen, was die EMI erhöht.

Statt mit einem festen Takt zu schalten, könnte auch ein Erkennungskreis das erste Minimum oder »Tal« der Drain-Source-Spannung des MOSFET (VDS) effektiv »erfassen « und den Transistor erst zu diesem Zeitpunkt einschalten. Dadurch würde die Einschaltstromspitze minimiert, da die parasitäre Kapazität auf die Mindestspannung geladen war.

Diese Erkennung wird allgemein als »Talschaltung« oder quasiresonante Schaltung bezeichnet. Es ist sogar möglich, dass ein Schaltungsentwickler unter bestimmten Bedingungen eine Nullspannungsschaltung (ZVS) erreicht, bei der keine Drain-Source-Spannung anliegt, wenn der MOSFET aktiviert wird.

In diesen Fällen treten keine Stromspitzen auf, da die parasitären Kapazitäten nicht geladen sind.

- Nicht nur Verluste minimiert

- Vorteile der Quasiresonanz