Programmierbare Logik spart Strom

CPLD fürs Licht

Fortsetzung des Artikels von Teil 1

Die PWM implementieren

Die CPLD-Architektur der »MAX II«-Bausteine von Altera unterstützt arithmetische Funktionen, sodass sich Zähler und Addierer mit nur einem Logikelement pro Bit Wortbreite implementieren lassen. Die programmierbare Natur dieser CPLDs macht es sehr einfach, Zähler mit jeder nur erdenklichen Breite und Zähllänge zu realisieren.

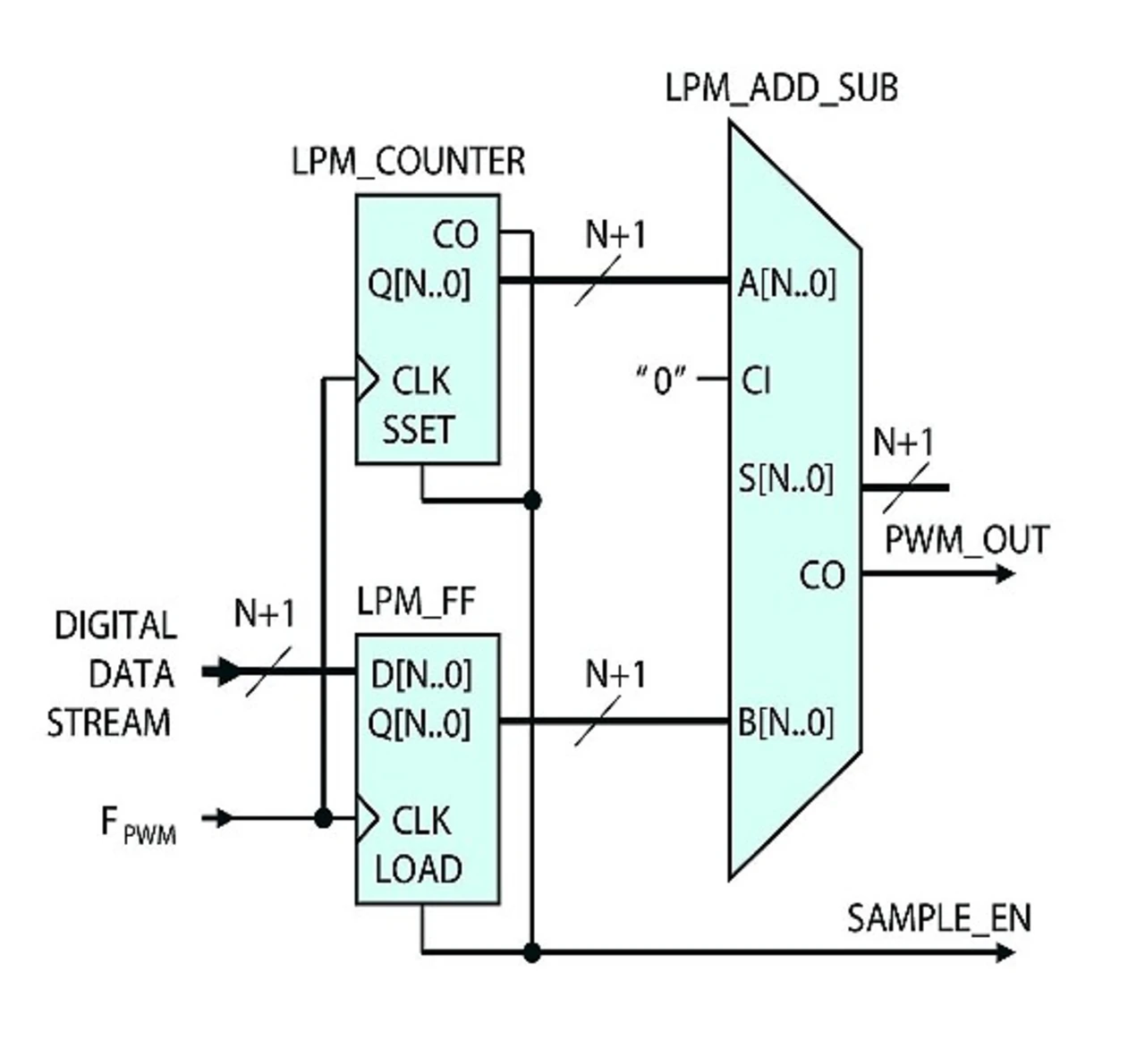

Bild 3 zeigt die drei Teile einer PWM, erstellt mithilfe der Bibliothek von parametrisierten Makros (LPM) der »Quartus II«-Software. Diese LPM-Blöcke - LPM_FF, LPM_Counter und LPM_ADD-SUB - sind mit dem GUI-Tool der Entwicklungssoftware erzeugt worden, das Verilog-, VHDL- und AHDL-Datenformate generiert.

Die PWM wird über die Taktquelle FPWM getaktet. LPM_FF hält den digitalen Wert, den die PWM in einen analogen Wert umwandelt. LPM_FF wird geladen, wenn das SAMPLE_EN-Signal »1« ist. Die Breite legt die Bitbreite des digitalen Datenstroms fest. Der LPM_Counter ist ein Binärzähler, der synchron vom SSET-Signal auf jeden Startwert gesetzt werden kann, typischerweise liegt er aber auf »0«. Der Carry-Output des LPM_Counters (CO) ist »1«, sobald der Zähler seinen maximalen Zählwert erreicht hat.

Der CO erzeugt das Sample-Enable-Signal »SAMPLE_EN«. Typischerweise ergibt sich eine Sample-Periode aus 2(N +1)⁄FPWM. Kundenspezifische Werte für den synchronen Wertesatz lassen sich in den LPM_Counter-Parametern spezifizieren. Eine PWM mit M verschiedenen Auflösungsniveaus wird durch folgenden synchronen Wertesatz erreicht: 2(N +1) - M - 1. Ein Beispiel, in dem eine »Nicht-2N-Auflösung« hilfreich wäre, ist die Steuerung der LED-Helligkeit in Ein-Prozent-Schritten von 0% bis 100%.

Dafür wäre ein 7-Bit-Zähler mit einem M = 27 notwendig. Der LPM_ADD_SUB ist ein binärer Addierer, der die Ausgänge von LPM_COUNTER und LPM_VV als »A«- und »B«-Eingänge benutzt. Der Carry-Input (CI) von LPM_ADD_SUB ist die Konstante »0«, der Ausgang von LPM_ADD_SUB SUM wird nicht benutzt und der PWM-Ausgang (PWM_OUT) ist der Carry-Output (CO) von LPM_ADD_SUB. Die folgenden Beispiele erklären, wie diese einfache Struktur für eine 4-Bit-PWM funktioniert.

- Wenn das LPM_FF-Sample »1« ist, erfolgen 16 Additionen, weil der LPM_COUNTER von 0 bis 15 hochzählt. Der CO des Addierers ist »0« für 15 von 16 Zählwerten (0 bis 14) und »1«, wenn der Zählwert 15 ist. Damit entsteht ein 1/16-Prozent-Tastverhältnis.

- Wenn das LPM_FF-Sample »8« ist, ist der CO des Addierers für die Werte 0 bis 7 »0« und »1« für die acht restlichen Zählwerte (8 bis 15). Damit wird ein 8/16-Prozent-Tastverhältnis erzeugt.

- Wenn der LPM_FF-Sample »15« ist, ist der CO des Addierers nur beim Zählwert 0 »0«. Für die restlichen 15 Werte (1 bis 15) beträgt er »1«. Damit ergibt sich ein 15/16-Prozent-Tastverhältnis.

Die PWM benötigt nur wenige Ressourcen. PWMs mit gängiger Abtastzeit und Auflösung können sich einen einzigen LPM_COUNTER teilen, während eine Nicht-2N-Auflösung die Effizienz nicht negativ beeinträchtigt.

- CPLD fürs Licht

- Die PWM implementieren