Design-Praxis: Systemsimulation (Teil 1)

Zur Versorgungsintegrität von Embedded Hardware

Fortsetzung des Artikels von Teil 3

Versorgungsimpedanzen verstehen

Der DC-Drop bedeutet aber nur einen Teil der Analyse, da die meisten ICs getaktet Strom beziehen: die IC-Logik ist durch CMOS-Transistorschaltungen implementiert, bei jedem Schaltvorgang werden Kapazitäten umgeladen. (Z.B. zwischen Gate und Bulk, den verschiedenen Signalnetzen und den Versorgungs- bzw. Masse-Netzen.) Das Versorgungssystem muss dazu, kapazitätsabhängig, kurzzeitige Ladeströme bereitstellen. Aufgrund der immensen Transistoranzahl im IC (viele Millionen) und der sehr kleinen, benötigten Ladungen für die meisten logischen Operationen, sind diese Ströme aus Versorgungssicht der Leiterplatte zeitunabhängig. Signalleiterbahnen und speziell Pads auf einer Leiterplatte tragen jedoch Kapazitäten im Pikofarad-Bereich. Wenn also Ausgangsleitungstreiber (Output Buffer Driver) auf digitalen Signalleitungen den logischen Wert umschalten, werden mit dem Spannungsschritt von GND auf VCC entsprechende Ströme notwendig (Bild 3 rechts oben, skizziert einen Ausgangstreiber). Bei 3,3 V VCC und 500 ps Schaltflanke fallen somit einige Milliampere an. []

Jobangebote+ passend zum Thema

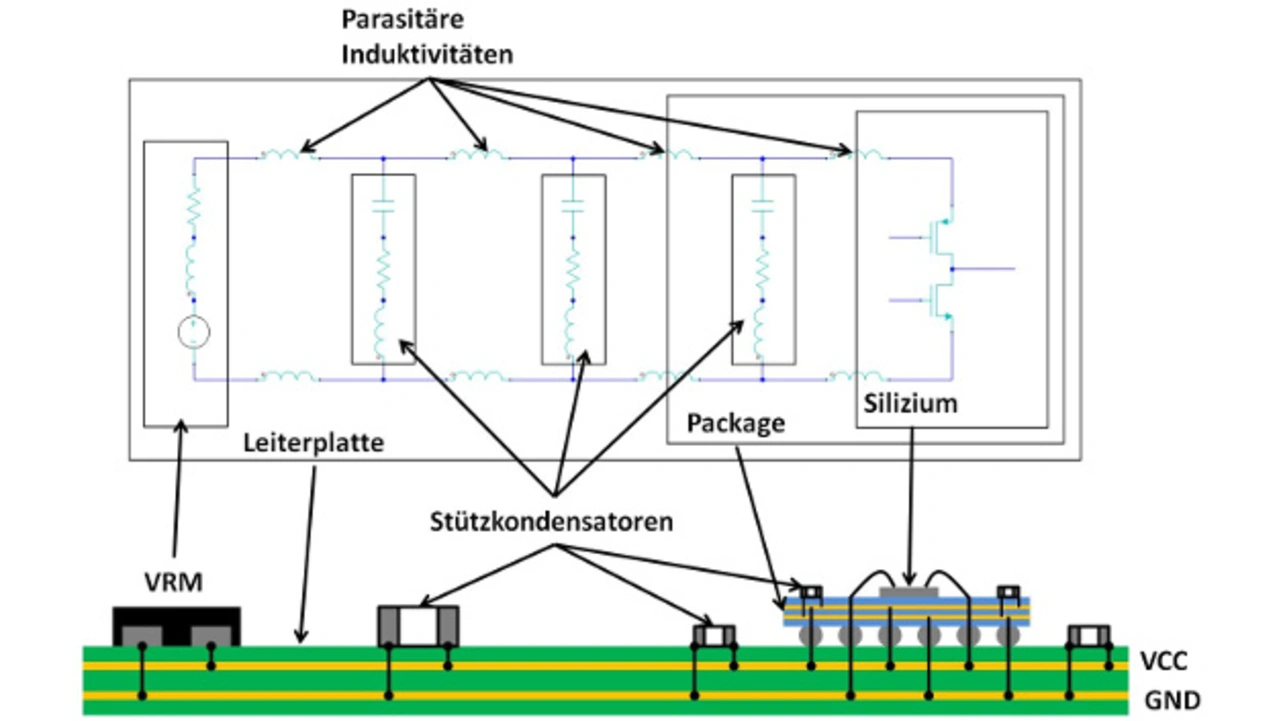

Andererseits liefert das Versorgungssystem nur eingeschränkt, beliebig latent, beliebig variable Ströme. Bild 3 skizziert ein Versorgungsnetzwerk vom VRM über Vias, die Versorgungslagen, weitere Vias, Lötkugeln und ein Package bis zum Siliziumchip. Das VRM ist meist ein DC-DC-Wandler, z.B. ein Buck Converter, der am Ausgang eine gegebene Spannung setzt. Das leistet eine PWM an einer Induktivität mit Regelkreis, der eine möglichst konstante Ausgangsspannung in einem gegebenen Fenster von Lastströmen bereitstellt. Das Wechselspiel des Reglers mit den Induktivitäten und dem Ausgangsfilter, bestimmt das VRM-Verhalten am Ausgang unterhalb der halben PWM-Frequenz. Bei der Auslegung des VRM ist auf ein möglichst flaches Impedanzprofil (ein frequenzunabhängiger Widerstand) zu achten.

Ab der PWM-Frequenz kann der Regelkreis die Lastwelligkeit nicht mehr kompensieren, das Ausgangsverhalten wird durch die Wandlerinduktivität und den Ausgangsfilter dominiert. In der Praxis kann das VRM, bei einem guten Design, im Arbeitsbereich durch eine frequenzabhängige Ausgangsimpedanz beschrieben werden: ein effektiver Widerstand der ab etwa der halben PWM-Frequenz in eine Induktivität übergeht (Bild 3 links oben). Zwischen VRM und dem IC führt der Strompfad nur über passive Strukturen, d.h. Vias und Leiterbahnen die in einem dielektrischen Substrat (vorwiegend FR-4) eingebettet sind, Lötkugeln und das Package. Dieser Strompfad besitzt eine Induktivität, die auf den DC-Widerstand addiert wird und somit eine AC-Impedanz ergibt. Je nach Leiterplattenlayout macht sich diese Induktivität ab ca. 100 kHz bemerkbar und behindert die AC-Stromversorgung des ICs.

- Zur Versorgungsintegrität von Embedded Hardware

- DC-Versorgungsintegrität als Designproblem

- DC-Versorgungsintegrität verifizieren

- Versorgungsimpedanzen verstehen

- Versorgungsimpedanzen optimieren

- Emissionen untersuchen