Embedded Instrumentierung kann Testprobleme lösen

Bauelemente übernehmen Testfunktionen

Fortsetzung des Artikels von Teil 1

Lösung für manches Problem: Embedded-Instrumentierung im Chip

Was soll nun ein Testingenieur machen angesichts der Tatsache, dass die Testabdeckung von Strukturtest-Technologien wie ICT abnimmt und dass die Diagnosefähigkeiten von traditionellen Funktionstest-Technologien nicht mehr ausreichen? Die Antwort ist Embedded-Instrumentierung im Chip. Eine Funktionstest-Technik wie PCT (Processor-Controlled Test) beispielsweise nutzt die CPU auf einer Leiterplatte zur Durchführung von Registertests und einer Komplettprüfung ihrer angeschlossenen Komponenten und Busse. Da sie auf einer tieferen Ebene ansetzen, können solche Tests in den meisten Fällen Fehler in defekten Teilen, Netzen und sogar Pins erkennen.

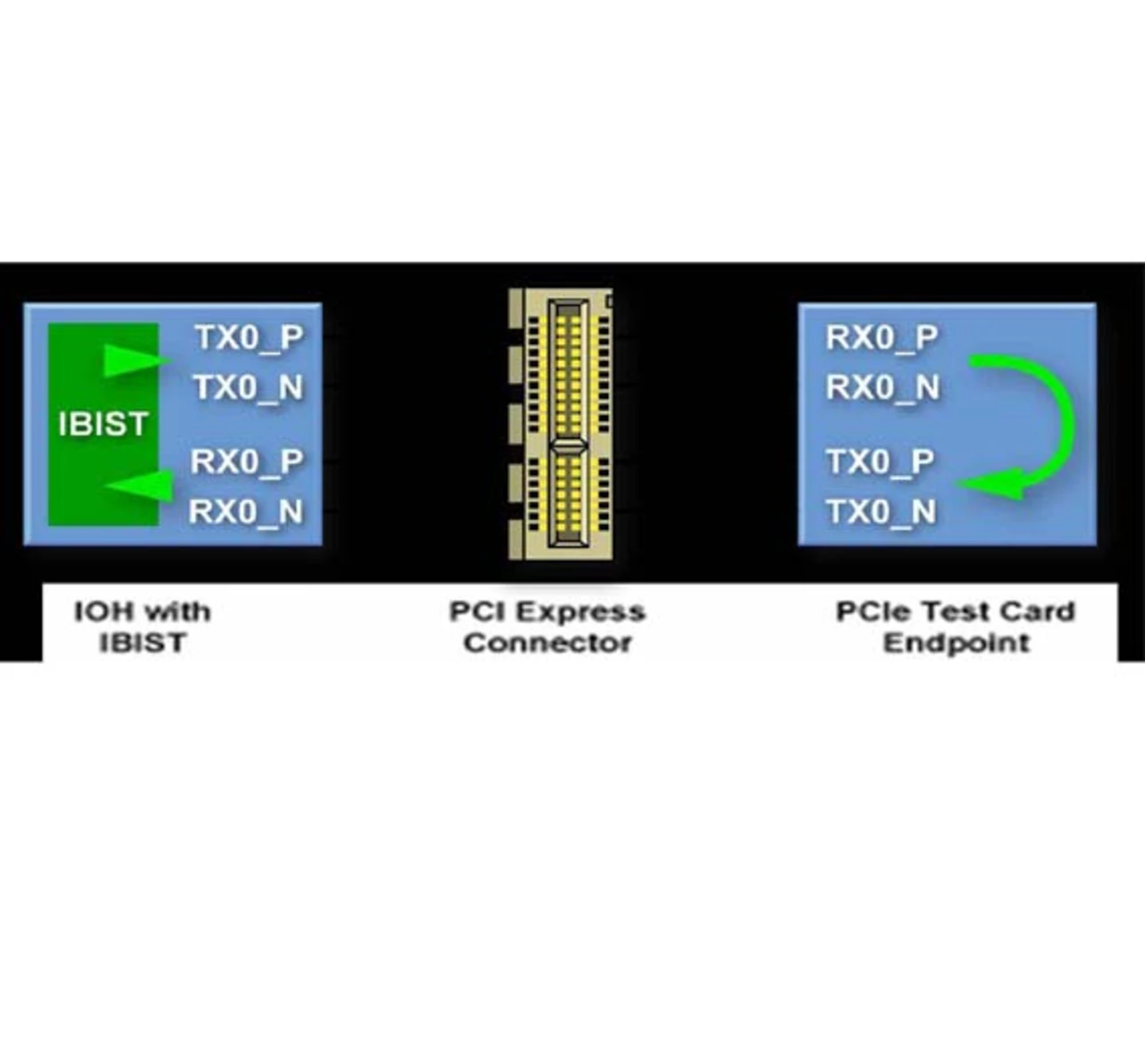

Bei Intel-Leiterplattendesigns bietet zum Beispiel der eingebettete IBIST-IP (IBIST: Interconnect Built In Self Test) in der Regel ein extrem hohes Maß an FAM- und PCOLA/SOQ-Testabdeckung (mit Erfassung eines Fehlerspektrums, das sich mit anderen Technologien unmöglich erreichen lässt), wobei sich die Defekte bis hinunter zur Teile- und Leiterbahn-Ebene zurückverfolgen lassen (Bild 2).

Letztendlich werden Verfahren auf Basis von "Embedded-Instrumentierung“ den Testzugang ersetzen, der für herkömmliche reine Strukturtester mehr und mehr verloren geht – und das zu wesentlich niedrigeren Kosten. Und da On-Chip-Instrumentierung auch Funktionsprüfungen der Verbindungsleitungen unterstützt, bietet sie den zusätzlichen Vorteil, dass sie neben PCOLA/SOQ auch noch FAM-Abdeckung bietet. Angesicht der hohen Testabdeckung, der exzellenten Diagnosefähigkeiten und der niedrigen Kosten geht der Trend in diese Richtung.

Der Autor:

Jobangebote+ passend zum Thema

| Alan Sguigna |

| hat mehr als 20 Jahre Erfahrung in den Bereichen Management, Marketing, Technik, Vertrieb, Fertigung, Finanzen und Kundenservice. Er ist bei Asset InterTech Vice President of Sales and Marketing. Vor seinem Wechsel zu diesem Unternehmen war er in verschiedenen Positionen bei Spirent Communications, einem Anbieter von Test-Produkten und-Services, und bei Nortel Networks tätig. |

- Bauelemente übernehmen Testfunktionen

- Lösung für manches Problem: Embedded-Instrumentierung im Chip