Powermanagement bei Funktransceivern

Leistung und Stromaufnahme im Transceiver skalieren

Fortsetzung des Artikels von Teil 3

Energieeinsparungen auf Systemebene

Wie im vorigen Abschnitt diskutiert, schalten Energiesparmodi auf Kanalebene die den Kanälen zugeordneten Komponenten, wie die im Datenpfad, HF-PLL und LDO-Regler ab. Im Fall, dass sich sowohl Sende- als auch Empfangskanal in Ruhe befinden, wie in dem Szenario in Bild 6 beschrieben, können Komponenten auf Systemebene abgeschaltet werden, um zusätzliche Energieeinsparungen zu erzielen. Solche Systemebenen-Komponenten sind Takt-PLL und die LDO-Regler der Takt- PLL, LDO-Regler für die Umsetzer und der ARM-Prozessor sowie seine Speicher. Wie bei den Energiesparmodi auf Kanalebene stehen auch auf Systemebene drei Energiesparmodi zur Verfügung. Dabei schaltet die höhere Nummer des Modus zusätzliche Systemkomponenten ab, wie in Tabelle 5 zusammengefasst.

Jobangebote+ passend zum Thema

| Abgeschaltete Kanal- und Systemkomponenten | Mode 3 | Mode 4 | Mode 5 | |

|---|---|---|---|---|

| Tx | Analoger and Digitaler Datenpfad | x | x | x |

| Interne Tx-PLLs | x | x | x | |

| PLL-LDOs und Tx-LDOs | x | x | ||

| Rx | Analoger and Digitaler Datenpfad | x | x | x |

| Interne Rx-PLLs | x | x | x | |

| PLL-LDOs und Rx-LDOs | x | x | ||

| CLK-PLL | x | x | x | |

| System | Umsetzer-LDOs und CLK-PLL-LDOs | x | x | |

| ARM-Prozessor + Speicher | x | |||

Tabelle 5. Energiesparmodi auf Systemebene. (Quelle: Analog Devices)

Wie in Tabelle 5 zu sehen, schaltet Mode 3 zusätzlich zu Mode 1 den CLK-PLL ab und schaltet Mode 4 zusätzlich zu Mode 2 den CLK-PLL, den Umsetzer-LDO-Regler sowie den CLK-PLL-LDO-Regler ab. Mode 5 schaltet über Mode 4 hinaus auch noch den ARM-Prozessor und seine Speicher ab. Allerdings führt das Abschalten zusätzlicher Komponenten zu längeren Aufwachzeiten (Tabelle 6). Im Mode 5 dauert es ungefähr 3,2 ms, um alle Komponenten wieder hochzufahren.

| Aufwachzeit bei unterschiedlichen Konfigurationen | Mode 3 | Mode 4 | Mode 5 |

|---|---|---|---|

| Ungefähre Hochfahrzeit [µs] | 250 | 650 | 3200 |

Tabelle 6. Energiesparmodi auf Systemebene und die damit verbundene Aufweckzeit. (Quelle: Analog Devices)

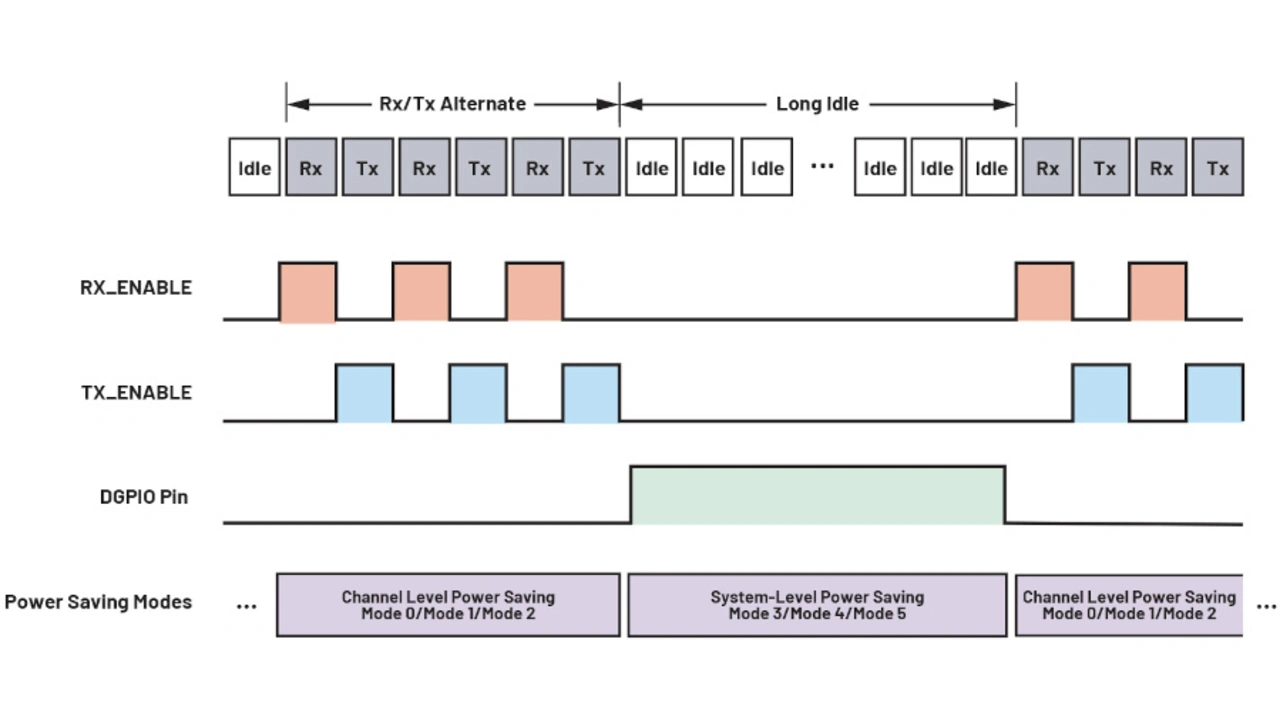

Anders als bei Energieeinsparungen auf Kanalebene, müssen die Energieeinsparungen auf Systemebene über einen DGPIO-Pin getriggert werden. Bild 8 zeigt ein Beispiel, wie Entwickler eine kombinierte Energieeinsparung auf Kanal- und Systemebene während unterschiedlicher Zeiten in einer TDD-Anwendung nutzen können, um eine höhere Energieeinsparung zu erzielen. In diesem Beispiel alternieren in dieser Zeitspanne der Sende- und der Empfangsbetrieb und der Anwender kann über die RX_ENABLE- und TX_ENABLE-Signale die bestmögliche Energieeinsparung auf Kanalebene auswählen.

Während der langen Ruheperiode, wenn kein Kanal aktiv ist, kann der Anwender einen DGPIO-Pin verwenden, der den höchstmöglichen Energiesparmodus auf Systemebene triggert, was das Abschalten weiterer Systemkomponenten erlaubt. Dies hilft eine höhere Energieeinsparung zu erzielen, als nur mit dem Einsparmodus auf Kanalebene. Wie auch bei der DGPIO-Pin-Methode bei den Energiesparmodi 1 und 2 auf Kanalebene, kann diese nur dann eingesetzt werden, wenn sowohl die TX_ENABLE- als auch die RX_ENABLE-Signale auf logisch low liegen.

Tabelle 7 präsentiert die Leistungsaufnahme für den in Bild 7 dargestellten DMR-Einsatzfall mit dem Energiesparmodus 2, wenn ein Kanal aktiv ist, und mit drei unterschiedlichen Einsparmodi, wenn beide Kanäle deaktiviert sind.

| Energiesparmodus auf Systemebene (nur für den Ruhezustand) | Leistungsaufnahme [mW] | ||

|---|---|---|---|

| PTx (nur Senden, Mode 2) | PRx (nur Empfangen, Mode 2) | PIdle (Ruhe) | |

| Mode 3 | 580 | 502 | 100 |

| Mode 4 | 580 | 502 | 65 |

| Mode 5 | 580 | 502 | 35 |

Tabelle 7. Leistungsaufnahme während unterschiedlicher Zeitspannen eines TDD-DMR-Profils mit dem Energiesparmodus 2 auf Kanalebene und den Einsparmodi 3, 4, und 5 auf Systemebene. (Quelle: Analog Devices)

Verglichen mit Tabelle 3 zeigt sich, dass man mit den Energiesparmodi auf Systemebene mehr Energie einsparen kann. Für den gleichen 5-5-90-Anwendungsfall ist die durchschnittliche Leistungsaufnahme weiter gesenkt, was sich mit 580 mW × 5 % + 502 mW × 5 % + 35 mW × 90 % = 86 mW berechnen lässt.

- Leistung und Stromaufnahme im Transceiver skalieren

- Energieeinsparungen auf Komponentenebene

- Energieeinsparungen auf Kanalebene

- Energieeinsparungen auf Systemebene

- Monitor-Modus