XDR-RAM verbessert Durchsatz im Vergleich zu DDR

Fortsetzung des Artikels von Teil 2

XDR-RAM verbessert Durchsatz im Vergleich zu DDR

An der XDR-Schnittstelle wird das DRSL-Verfahren mit einem „Flex-Phase Timing Adjustment“ kombiniert. FlexPhase kompensiert Effekte, die etwa durch kleinste Schwankungen der Leiterbahnlängen infolge von Herstellungstoleranzen verursacht werden. Das Resultat ist ein deterministisches Signal-Timing, durch das die Systeme in der Nähe ihrer idealen Timing-Parameter arbeiten können, anstatt den Worst Case zugrundezulegen. Darüber hinaus besteht bei den XDR-Modulen die Möglichkeit einer Skalierung des Durchsatzes, und zwar durch das „Dynamic Point to Point“-Verfahren (DPP), bei dem eine Multi-Point-Topologie mit der hohen Datenübertragungsrate der Punkt-zu-Punkt-Signalisierung kombiniert werden kann.

Durch diese Kombination lassen sich mit dem XDR-Interface auf Basis der Standard-Kernarchitektur DRAMs realisieren, die mit Taktfrequenzen zwischen 3,2 und 8 GHz Datenübertragungsraten von 6,4 bis 16 Gbit/s in einem einzigen XDR-DRAM-Baustein zulassen. Eine weitere Optimierung des Kerns zielt auf die Verringerung der Zugriffs-Granularität, so dass die Vorteile der höheren Datenübertragungsrate der XDR-Technologie in XDR2, der nächsten Generation der XDR-Produktfamilie, zum Tragen kommen können.

Jobangebote+ passend zum Thema

Kern-Aspekte im Blickpunkt

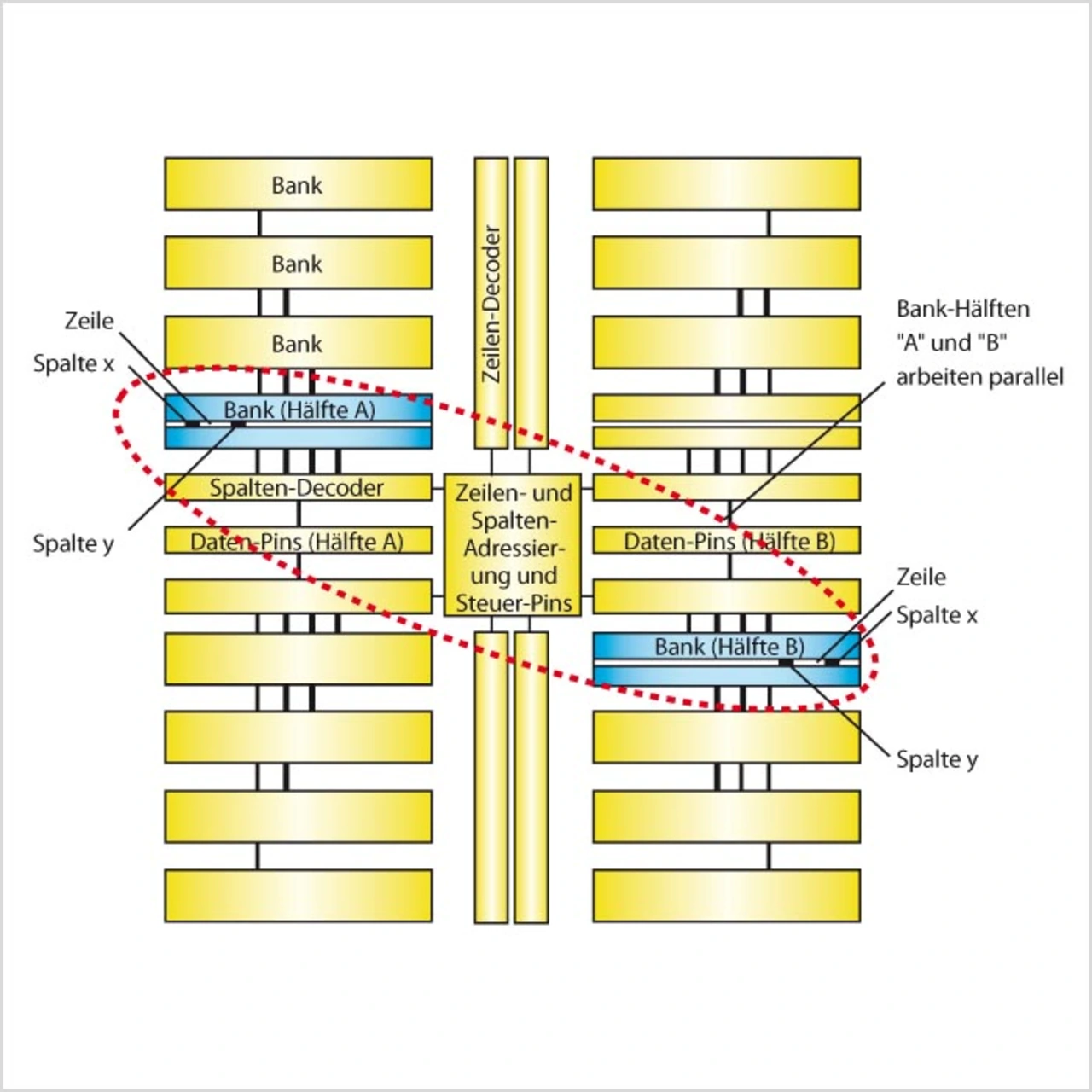

Am Beispiel eines DRAM-Kerns, der aus acht logisch versetzt angeordneten Bänken besteht, wird in Bild 1 dargestellt, wie sich die Zugriffs-Granularität verringern lässt. Zwei Gruppen von Daten-Pins untergliedern die Bänke in zwei Hälften, die auf Zeilen- und Spalten-Befehle hin parallel zueinander arbeiten. Ein Zeilen-Befehl selektiert eine einzelne Zeile in jeder Halb-Bank, während zwei Spalten-Befehle zwei Spalten-Speicherstellen in jeder Halbzeile selektieren. Vier Halb-Bänke ergeben einen Quadranten, der über eigene Spalten- und Zeilen-Decoder verfügt.

Nach dem Eingang eines Zeilen-Befehls werden die selektierte Zeile abgefragt und die Informationen zwischengespeichert. Bevor eine weitere Bank einen Zeilen-Zugriff ausführen kann, muss die Zeilen-Zugriffszeit (tRR) verstrichen sein. Die Zeilen-Schaltungen der betreffenden Bank sind während des gesamten Intervalls belegt. Nach Eingang eines Spalten-Befehls (col x) erfolgt ein Zugriff auf die selektierte Spalte. Die Spalten-Zugriffszeit tCC muss abgelaufen sein, bevor die Bank einen weiteren Spalten-Zugriff (col y) ausführen kann.

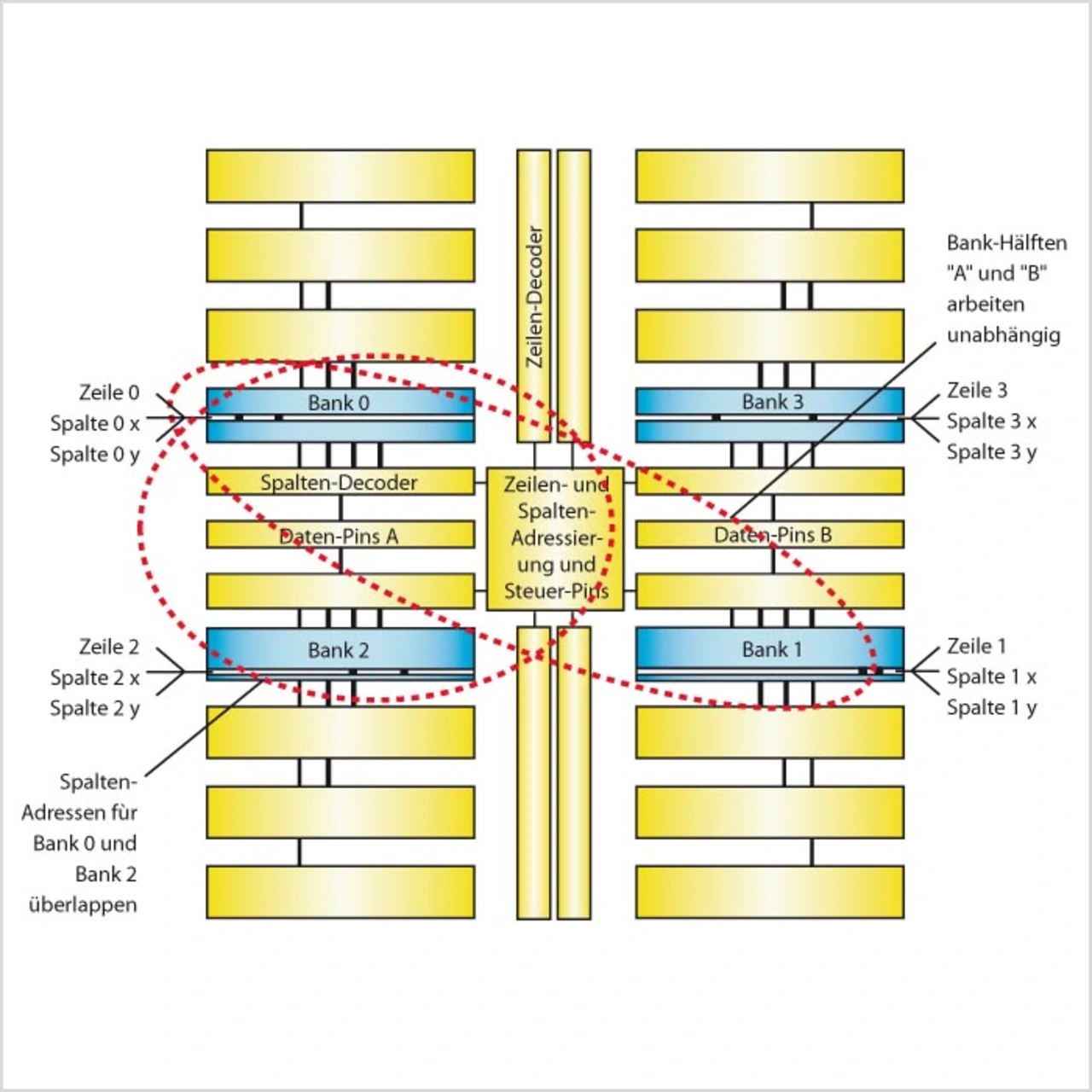

Die Signallaufzeiten setzen für das Bit-Transport-Intervall eine Grenze von 0,25 ns und legen für tCC eine Untergrenze von etwa 4 ns fest. Die maximale Spalten-Zugriffsrate beträgt deshalb 250 MHz. Auf jeder Verbindung werden während eines Spalten-Zugriffs 16 bit übertragen. Bei angenommenen 16 Daten-Verbindungen ergibt sich eine Spalten-Granularität von 32 byte. Da tRR) doppelt so groß wie tCC ist, beträgt die Zeilen-Granularität 64 byte. Wird nun der Kern in eine größere Zahl von Bänken mit jeweils unabhängigen Zeilen- und Spalten-Schaltungen unterteilt, dann lassen sich die sonst für tRR) und tCC geltenden Einschränkungen überwinden, denn die Architektur gestattet eben die Abwicklung mehrerer kleiner Zugriffe während dieser Zeitintervalle: Dieses Verfahren wird als „Micro Threading“ bezeichnet.

Bild 2 zeigt die internen Details eines Micro-Threaded-DRAM-Kerns. Die insgesamt 16 unabhängigen Bänke entsprechen dann jeweils einer Halb-Bank des konventionellen DRAM-Kerns in Bild 1. Geradzahlige Bänke sind den A-Datenpins zugeordnet, ungeradzahlige den Pins der Gruppe B. Die Bänke sind in Vierergruppen zusammengefasst und bilden sp Quadranten, die jeweils eigene Zeilen- und Spalten-Schaltungen besitzen und deshalb auch unabhängig von den anderen Quadranten auf Zeilen- und Spalten-Befehle reagieren können. Ein Spalten-Zugriff eines oberen Quadranten wird mit dem entsprechenden Spalten-Zugriff des unteren Quadranten verzahnt. Damit lassen sich die Spalten-Granularität auf 8 byte und die Zeilen-Granularität auf 16 byte reduzieren, was einem Viertel des vorigen Wertes entspricht. Diese Verminderung der Granularität resultiert in Leistungs-Verbesserungen für die Anwendungen, obwohl die Datenübertragungsrate der Schnittstelle und die Zugriffsintervalle des DRAM-Kerns gegenüber dem Standard-Baustein ohne Micro Threading unverändert geblieben sind. XDR2-Bausteine unterstützen Taktfrequenzen von 8 bis 12,8 GHz, was die mit einem einzigen ×16-XDR2-DRAMBaustein erzielbare Datenübertragungsrate auf 16 bis 25,6 Gbyte/s anhebt. A. Reddy/fr

- XDR-RAM verbessert Durchsatz im Vergleich zu DDR

- Intel prüft XDR-Speichertechnik von Rambus

- XDR-RAM verbessert Durchsatz im Vergleich zu DDR