Neuer Mikrocontroller für elektrische Motorsteuerungen

Totzeit-Kompensation verhindert Motor-Crash

Fortsetzung des Artikels von Teil 4

Totzeit-Kompensation verhindert Motor-Crash

Wie bei allen Load-Store-Architekturen betrifft auch hier eine der entscheidenden Fragen die Zahl der Universalregister, die für die allgemeine Verwendung zur Verfügung stehen. Im SH2-Core sind 16 dieser Register vorhanden, die von der CPU als Register sowie zum Ablegen von Variablen, Zeigern und Masken verwendet werden können. Weitere Register in der SH2-CPU sind der PC (Programmzähler), die bereits erwähnten Register MACH und MACL sowie zwei Zeiger. Das GBR trägt zum zügigeren Abrufen globaler Daten aus Feldern bei. Das VBR wird als Basisregister für Vektoren verwendet, um für Flexibilität hinsichtlich des Speicherortes für Interruptvektoren zu sorgen. Neben diesen Registern verfügt der SH2-Core über ein so genanntes Procedure-Register (PR), das die Interrupt-Latenz verringert und die Rücksprungzeit aus Unterprogramm-Befehlen verkürzt. Beim Einsprung in eine Interrupt-Subroutine dient das PR zum Ablegen des PC-Werts, der somit nicht auf den Stack gelegt werden muss und beim Verlassen des Unterprogramms schneller zur Verfügung steht.

Jobangebote+ passend zum Thema

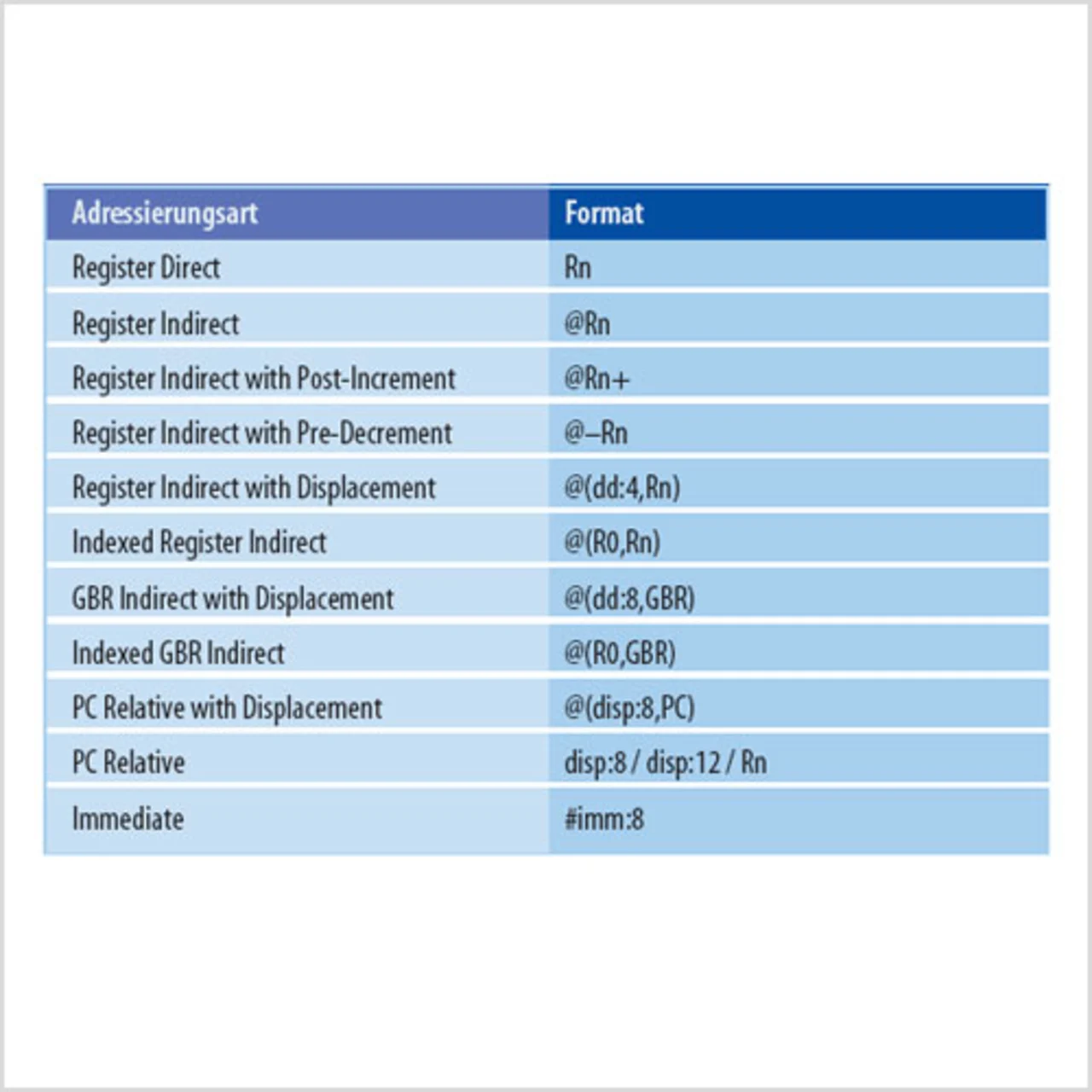

Der SH2-CPU-Core unterstützt elf Adressierungsarten, die alle speziell dafür konzipiert sind, die Effizienz des vom Compiler generierten Codes zu steigern (Tabelle 1). Besonders hervorzuheben sind die Adressierungsarten „Register Indirect with Post-Increment“ bzw. „Pre-Decrement“. Diese ermöglichen den Zugriff auf eine bestimmte Speicherstelle mit anschließender Inkrementierung bzw. Dekrementierung des Zeigers. Es erfolgt eine entscheidende Rationalisierung der Zugriffe auf den Stack oder auf Felder in Applikationen. Bei der ebenfalls unterstützten Adressierungsart „Indexed Register Indirect“ wird als effektive Adresse die Summe der Inhalte des angegebenen Registers und des Registers 0 verwendet. Diese Adressierungsart erweist sich speziell bei Zugriffen auf Inhalte von C- oder C++-Strukturen als nützlich. Natürlich sind auch alle übrigen Standard-Adressierungsarten, die ein leistungsfähiger Prozessorkern erwarten lässt, vorhanden.

Peripheriefunktionen

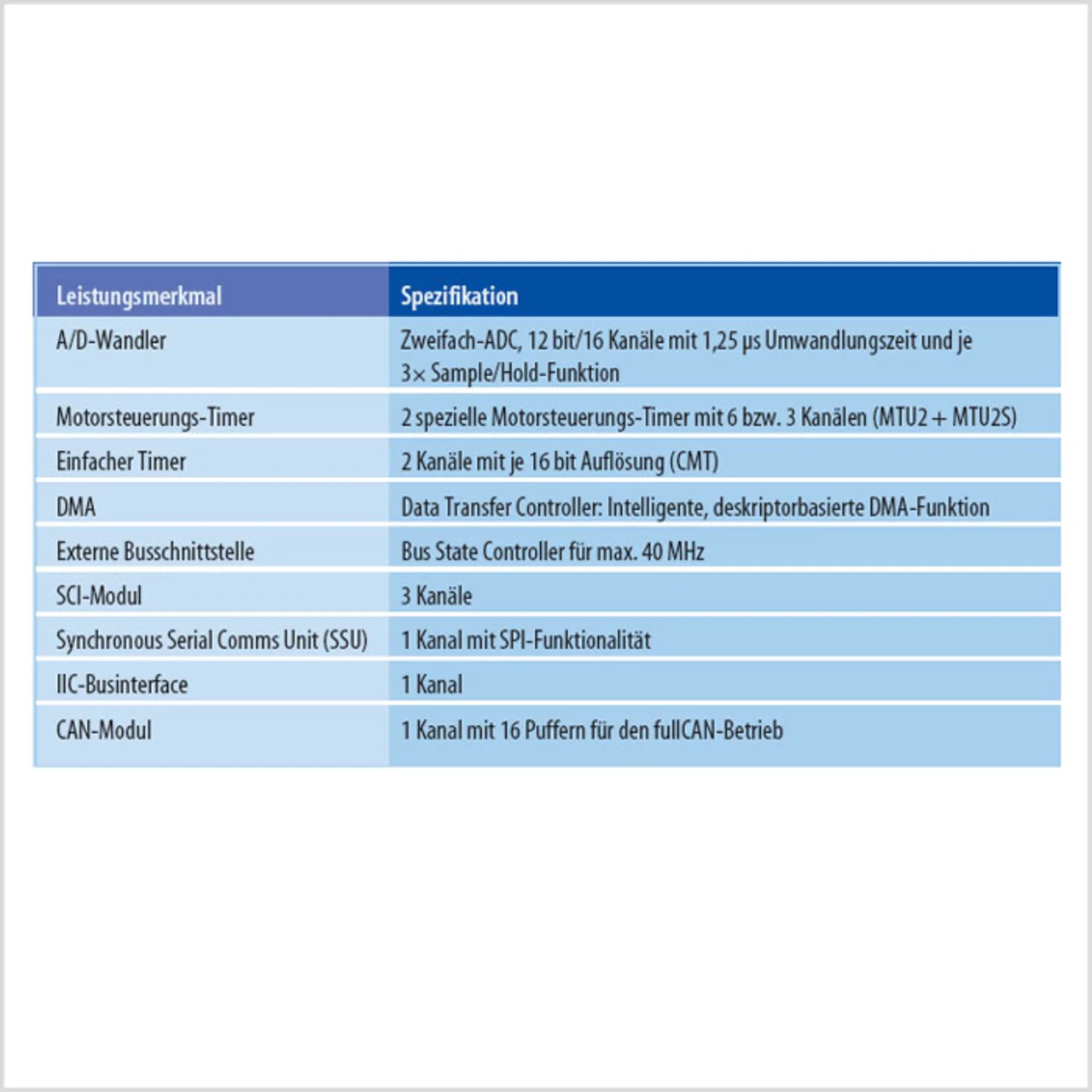

Wie im vorigen Abschnitt erläutert, enthält der Mikrocontroller SH7137F neben dem SH2-Core eine Vielzahl von Peripheriefunktionen, die ideal für Motorsteuerungs-Anwendungen, aber auch für den Einsatz bei anderen, weniger speziellen Aufgaben geeignet sind. Zum Beispiel gehören zu dem Baustein 256 K ein superschneller MONOS-Flash-Speicher, 16 Kbyte RAM und eine ganze Reihe weiterer Leistungsmerkmale, die in der Tabelle 2 aufgeführt sind. Der SH7137F hat ein QFP-Gehäuse mit 100 Pins und wird mit 3,3 V oder 5 V betrieben.

Da der SH7137F speziell für Frequenzumrichter entwickelt wurde, hat er natürlich entsprechend ausgerichtete Funktionen integriert. Zu den Leistungsmerkmalen, die ihn speziell für dieses Segment prädestinieren, zählen die Timer-Einheiten MTU2 und MTU2S. MTU2 ist eine sechskanalige 16-bit-Timer-Einheit. Jeder Kanal kann hier die gängigen Timer-Funktionen wie zum Beispiel „synchronized Timer“ wahrnehmen. Puffer-Betriebsarten erleichtern die Implementierung von Eingangs-Capture- und Ausgangs-Compare-Funktionen. Im Kaskadierungs-Modus werden zwei 16-bit-Timer-Kanäle zu einem 32-bit-Timer kombiniert, um das Timing langer Intervalle zu erleichtern. Hinzu kommen zahlreiche Optionen für das Erzeugen unterschiedlicher PWM-Signale.

- Totzeit-Kompensation verhindert Motor-Crash

- Autoren:

- A/D-Wandler und POE

- Totzeit-Kompensation verhindert Motor-Crash

- Totzeit-Kompensation verhindert Motor-Crash

- Totzeit-Kompensation verhindert Motor-Crash