Fehler durch kosmische Strahlung

Soft-Errors in Halbleiterspeichern verstehen und ihre Folgen mildern

Fortsetzung des Artikels von Teil 2

Neutronen sind eine bedeutende Quelle von Soft-Errors

Neutronen ohne kinetische Energie sind wegen der Reaktionen beim Einfangen von Neutronen eine bedeutende Quelle von Soft-Errors. Das Einfangen eines thermischen Neutrons durch einen Kern eines Bor-Isotop (10B), die in großen Mengen in dem als Glasdielektrikum eingesetzten Borphosphorsilikat vorkommen, führt zu Emission eines Alphateilchens, eines Lithiumkerns und von Gammastrahlung. Sowohl das Alphateilchen als auch der Lithiumkern können einen Soft-Error verursachen.

Thermische Neutronen sind ein besonders wichtiger Faktor in der Medizinelektronik, die in der Bestrahlungstherapie eingesetzt wird. Im Zusammenspiel mit dem bei der Behandlung eingesetzten Photonenstrahl führen die Neutronen zu einem Neutronenfluss, der eine sehr hohe Rate von Soft-Errors verursacht. Dennoch sind thermische Neutronen heute keine Hauptursache von Soft-Errors mehr, da die Hersteller mit dem 150-nm-Prozess-Node keine borierten Dielektrika mehr einsetzen.

Soft-Errors können durch eine verbesserte Prozesstechnologie und Anordnung der Speicherzellen, Änderungen auf Systemebene und Änderungen beim Chip-Design und der Architektur vermieden werden. Die Zuverlässigkeit eines Speicherbausteins kann dadurch erhöht werden, dass die in der Speicherzelle enthaltene kritische Ladung vergrößert wird. Die Widerstandsfähigkeit eines Bauteils gegenüber Soft-Errors lässt sich auch durch eine Prozesstechnologie mit geringerer Diffusionsschichtdicke verbessern. Dadurch verkürzt sich die Zeitdauer, die ein geladenes Teilchen in einer Speicherzelle verbringt. Eine Dreifachwannenarchitektur kann dazu eingesetzt werden, Ladungen aus der aktiven Region abzuleiten. Dieser Prozess erzeugt ein gegenüber der NMOS-Verarmungszone entgegengerichtetes elektrisches Feld und zwingt die Ladungen in das Substrat. Er wirkt nur, wenn im NMOS-Bereich ein Soft-Error auftritt.

Auf der Systemebene können die Entwickler die Auswirkungen von Soft-Errors mit Hilfe einer Logik vermeiden, die mit einem externen Fehlerkorrekturcode (ECC) arbeitet. Bei dieser Technik setzt der Anwender zusätzliche Speicherchips mit Paritätsbits zur Fehlererkennung und -korrektur ein. Wie zu erwarten war, ist die Bekämpfung auf Systemebene teuer. Außerdem erhöht sie die Komplexität des Systems und seiner Software.

Dies ist der beste Weg, Soft-Errors zu bekämpfen. Chip-Entwickler können die Auswirkungen von Soft-Errors mit Hilfe eines Fehlerkorrekturcodes (ECC) verringern. Während eines Schreibvorgangs fügt der ECC-Encoder-Algorithmus zu jedem in den Speicher übernommenen adressierbaren Datenwort Paritätsbits hinzu. Beim Lesen nutzt der ECC-Erkennungs-Algorithmus die Paritätsbits, um zu bestimmen, ob Datenbits verändert worden sind. Falls nur ein einzelnes Bit betroffen ist, bestimmt der ECC-Korrektur-Algorithmus die Position dieses Bits. Zur Fehlerkorrektur wird anschließend das Datenbit wieder in seinen ursprünglichen Wert verändert.

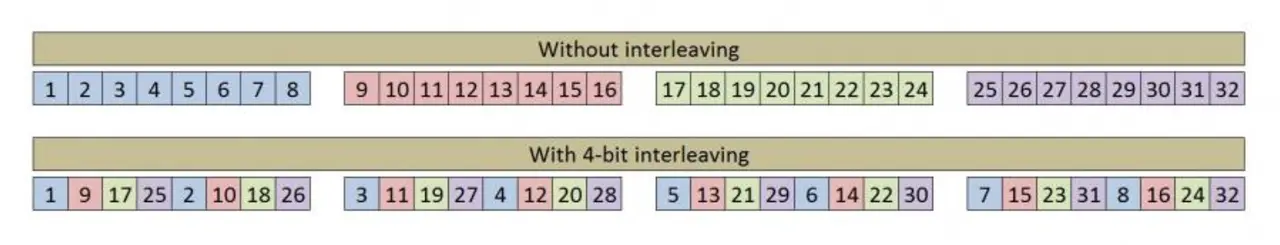

ECC allein löst jedoch noch nicht das Problem einer Störung mehrerer Bits (MBU). Hierfür müssen die Entwickler das sog. Bit-Interleaving einsetzen. Diese Technik ordnet die Bitfolgen so an, dass physikalisch benachbarte Bits in verschiedene Wort-Register geschrieben werden. Der Abstand beim Bit-Interleave verhindert, dass zwei aufeinanderfolgende Bits in dasselbe Wort-Register geschrieben werden. Wenn der Abstand beim Bit-Interleave größer ist, als der von einem über mehrere Bits reichenden Soft-Error betroffenen Bereich, führt dies zur Störung einzelner Bits (SBU) in mehreren Wörtern statt mehrerer Bits (MBU) in einem Wort. Der typische Abstand beim Bit-Interleave hängt von der Prozesstechnologie ab. Es wird ein Neutronentest mit einer anschließenden physikalischen MBU-Analyse durchgeführt, um für jede einzelne Prozesstechnologie den sicheren Abstand beim Interleaving zu ermitteln. Bei einem Speicher mit Bit-Interleave kann der Fehlerkorrektur-Algorithmus für einzelne Bits zur Erkennung und Korrektur aller Fehler eingesetzt werden. Der ECC-Algorithmus wirkt sich nur auf die Kopie des betroffenen Datenworts aus. Die Daten im Speicher enthalten immer noch das umgekehrte Bit. Falls dieses verfälschte Bit im Speicher nicht korrigiert wird, kann das Umkehren eines weiteren Bits im selben Wort zu einem MBU führen. Daher ist es wichtig, dass die ECC-Logik das Auftreten und die Korrektur der Störungen einzelner Bits meldet. Das System kann anhand dieser Information das Ereignis erkennen und die korrigierten Daten zurückschreiben. Diese Technik ist als Memory-Scrubbing bekannt.

Jobangebote+ passend zum Thema

In dem Maß, wie die Strukturen in Halbleiterchips immer kleiner werden, steigt die Gefahr von Soft-Errors. Daher erwarten zahlreiche Fachleute, dass die Soft-Errors zum beschränkenden Faktor bei der weiteren Größenreduzierung werden, wenn keine neue Technologie entwickelt wird, die das Problem der Soft-Errors löst. Außerdem steigen dadurch, dass Technologie in immer mehr Bereichen des menschlichen Lebens eingesetzt wird, die Anforderungen an die Zuverlässigkeit. Dieser Trend erhöht die Notwendigkeit des Einsatzes von Fehlerkorrekturcode (ECC) bei Speichermodulen. Alle bedeutenden Speicherhersteller haben begonnen, Chips mit On-Chip-ECC vorzustellen, um die Nachfrage nach hochzuverlässigem Speicher zu erfüllen. Angesichts der anspruchsvollen Anwendungen, in denen SRAM eingesetzt wird, ist die Möglichkeit zur Fehlerkorrektur bei SRAM unverzichtbar geworden. Cypress, das weltweit führende Unternehmen im Bereich SRAM, produziert eine Familie von höchstzuverlässigem asynchronem SRAM mit On-Chip-ECC und Bit-Interleaving.

- Soft-Errors in Halbleiterspeichern verstehen und ihre Folgen mildern

- Ein Soft-Error ist ein Zustandswechsel

- Neutronen sind eine bedeutende Quelle von Soft-Errors