Alte Schaltkreise neu entwickeln

Redesign abgekündigter ASICs #####

Fortsetzung des Artikels von Teil 2

Ein ASIC in einer maskenprogrammierbaren Technologie nachentwickeln

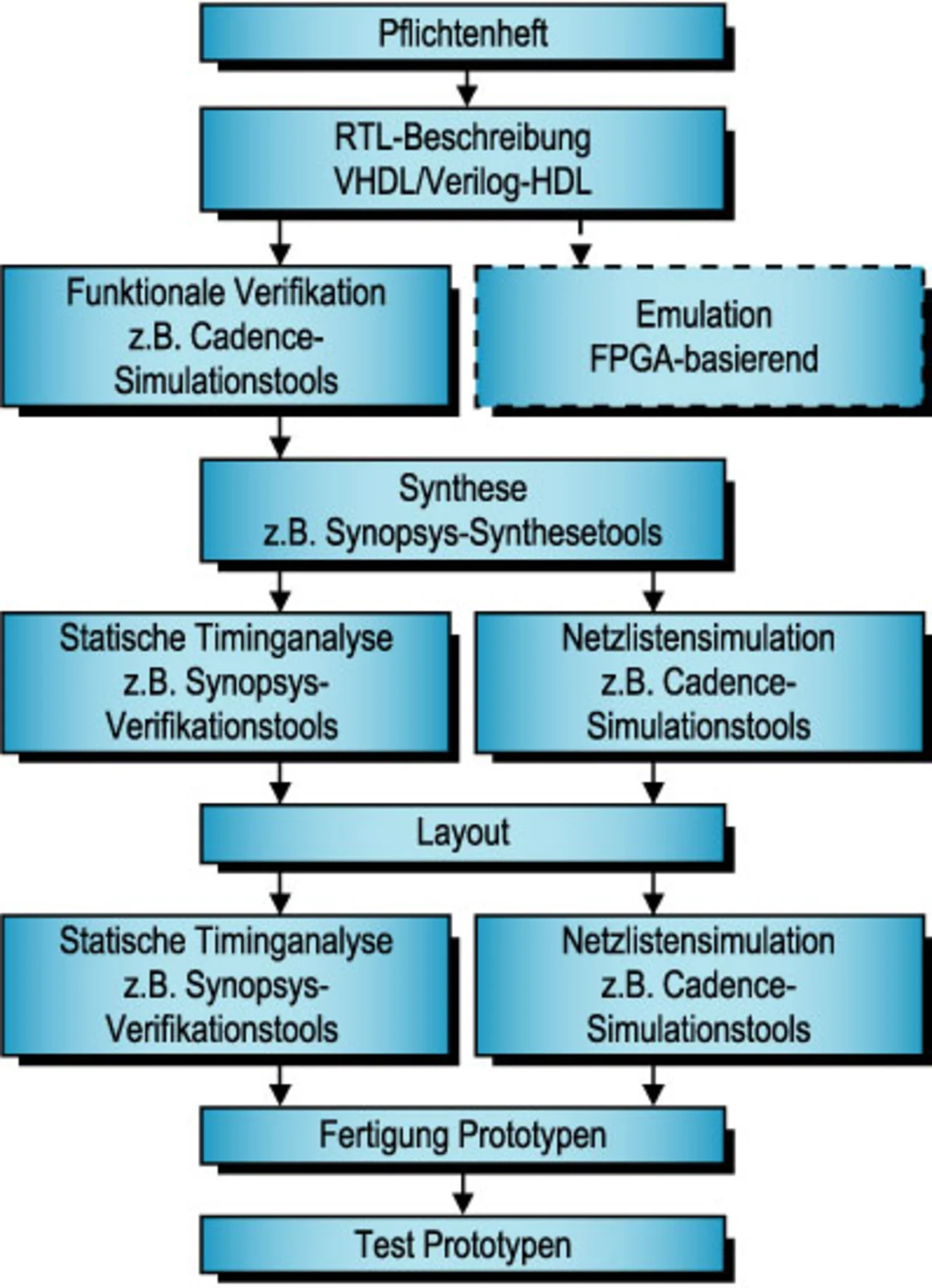

In Bild 2 ist der Design-Ablauf für ein maskenprogrammierbares ASIC dargestellt. Zu Beginn der Entwicklung wird ein Pflichtenheft erarbeitet, auf dessen Grundlage die RTL-Beschreibung (Register Transfer Level) des ASICs erfolgt. Die anschließende funktionale Verifikation des RTL-Modells geschieht unter Benutzung der eventuell vorliegenden Test-Bitmuster oder der Testum-gebung. Die FPGA-Emulation beschleunigt die Verifikation. Es werden mehr Testfälle ausgeführt und damit wird eine höhere Testabdeckung erreicht. Das verifizierte RTL-Modell bildet die Basis für die Synthese in die Zieltechnologie. Die Verifikation der erhaltenen Netzliste erfolgt mittels Simulation und statischer Timinganalyse. Ist dieser Verifikationsschritt erfolgreich, kann die Freigabe zum Layout erfolgen, und die Vektoren für den Serientest werden erzeugt. Das Layout wird in der Regel durch den Halbleiterhersteller selbst erstellt. Aus dem Layout wird die Postlayout-Netzliste erzeugt und verifiziert. Bei positivem Ergebnis können anschließend die Prototypen gefertigt werden. Der Prototypentest in der Applikation bringt die abschließende Gewissheit, ob das Redesign den gewünschten Erfolg hatte. Dabei sind funktionelle wie elektrische Eigenschaften gleichbedeutend Gegenstand der Untersuchung. Anschließend steht der Serienfertigung nichts mehr im Weg.

Jobangebote+ passend zum Thema

Das Beispiel eines ASIC-Redesigns für die Siemens AG zeigt die Vorgehensweise für das Redesign eines ASICs auf einer maskenprogrammierbaren Technologie. Das betreffende ASIC ist ein Schnittstellenschaltkreis, der aus einem seriellen Eingangsdatenstrom pulsbreitenmodulierte Ausgangssignale erzeugt. Das Original-ASIC entstand vor mehr als zehn Jahren in einer 1,0-µm-Standard-Zell-Technologie. Als Entwicklungswerkzeuge wurden ehemals der LOG/iC- GatesPro-Compiler und die SOLO1400-ASIC-Entwicklungsumgebung genutzt. Eine De-Archivierung der Datenbasis war aus technischen Gründen nicht möglich.

Was waren die weiteren Randbedingungen für das Redesign? Das ASIC wird in vier verschiedenen Baugruppen bei Siemens eingesetzt. Für die nächsten fünf Jahre ist zu erwarten, dass in Summe eine Anzahl von ca. 5000 ASICs benötigt wird. Das neue ASIC muss pinkompatibel im SOIC20-Gehäuse geliefert werden und mit einer Betriebsspannung von 5 V arbeiten. Eine der mit diesem ASIC bestückten Anwendungen ist auf einen minimierten Stromverbrauch ausgelegt.

Auf Grund der Stückzahl und der Anforderungen an Betriebsspannung, Stromaufnahme und Gehäuse wurde als Zieltechnologie ein Gate-Array mit 0,6 µm Strukturbreite gewählt. Das Gate-Array ermöglicht problemlos eine Umsetzung im SOIC20-Gehäuse und bildet wirtschaftlich im Vergleich zu anderen Möglichkeiten das Optimum. Die Initialisierungskosten (Layout, Maskenerstellung) für die Gate-Array-Technologie sind günstiger als für andere maskenprogrammierbare Entwicklungen. Die avisierte Stückzahl der Serie kann so preisgünstig hergestellt werden.

Eine weitere wichtige Voraussetzung für das Redesign war eine ausführliche Spezifikation mit einer abgedruckten Netzliste. Leider konnte im Vorfeld der Entwicklung keine Gewissheit erlangt werden, wie genau die vorliegende Netzliste der Realisierung im Orginal-ASIC entspricht. Das Redesign begann unter der Annahme, dass die Unterschiede nur relativ gering sind. Für die Umsetzung des Redesigns wurde dann der folgende Weg gewählt:

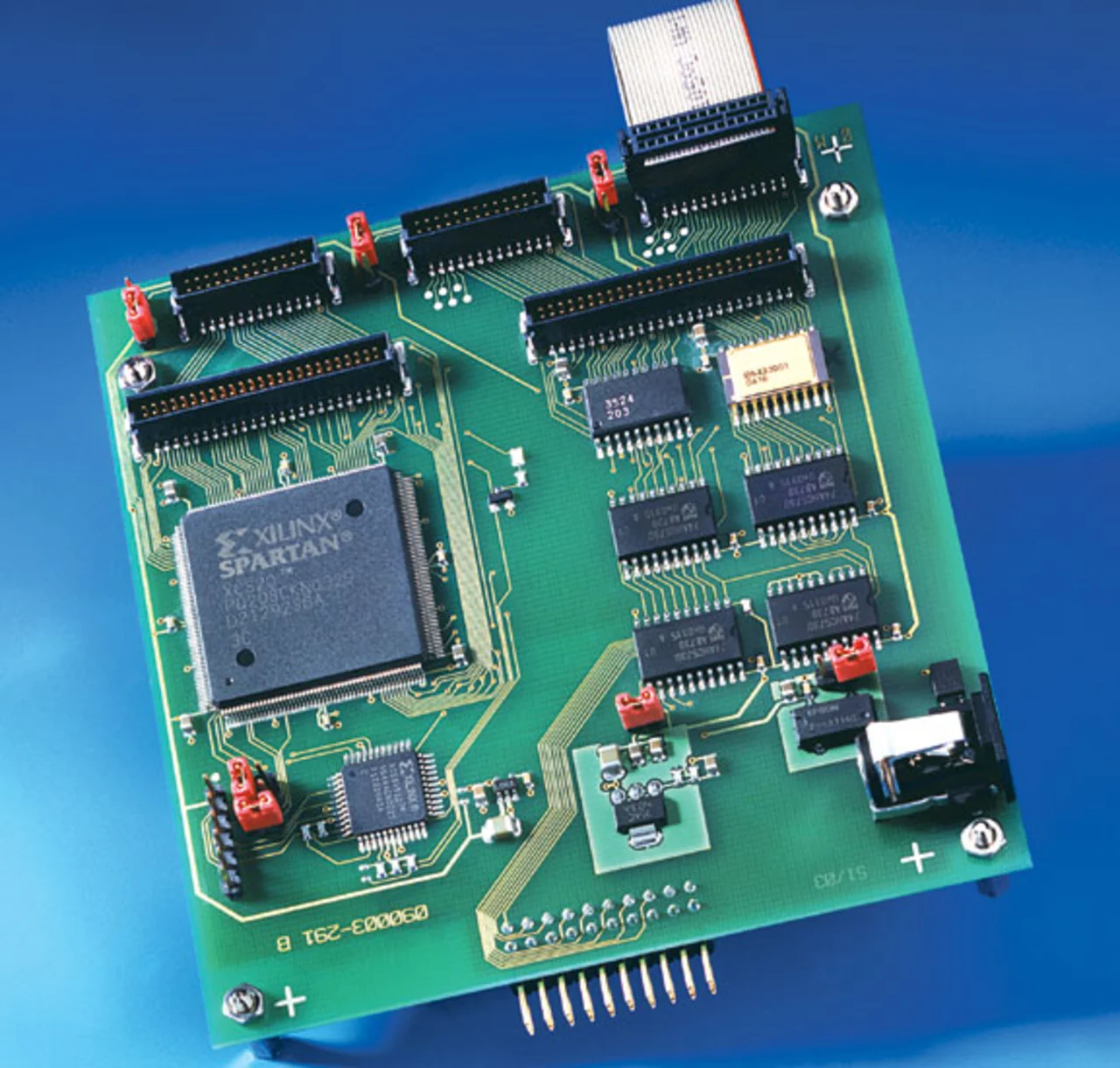

- Erstellung einer Test-Leiterplatte (mit Emulations-FPGA konfiguriert per E2PROM, Original-ASIC und ASIC-Kopie).

- Implementierung der Netzliste im FPGA und Verifizierung des Designs gegenüber dem Original-ASIC und in den vier Applikationen.

- Synthese und Layout in der Gate-Array-Technologie.

- Test der Prototypen auf der Test-Leiterplatte und in den vier Applikationen.

Auf der Test-Leiterplatte (Bild 3) können die drei „ASICs“ parallel betrieben werden. Für die Verifikation der drei Schaltkreise gibt es die Möglichkeit, die Eingangssignale mit einem Bitmuster-Generator zu stimulieren und alle Ein- und Ausgangssignale mit einem Logikanalysator aufzuzeichnen. Um die Schaltkreise in den vier Applikationen zu integrieren, wird die Test-Leiterplatte mittels Bandkabel und Stecker mit der Applikationsschaltung verbunden. Dabei wird ein Ende des Bandkabels direkt in die Schaltung an Stelle des SOIC20-Gehäuses eingelötet und das andere Ende über einen angepressten Stecker mit der Test-Leiterplatte verbunden. Dadurch ist es möglich, zwischen den drei realisierten Möglichkeiten umzustecken und Unterschiede im Verhalten sofort nachmessen zu können.

Die Umsetzung des Designs erfolgte in VHDL. Die vorhandene Netzliste war eine Gate-Level-Beschreibung in LOG/iC-Syntax. Eine Testumgebung war leider nicht vorhanden; sie musste neu erstellt werden. Aus der verbalen Beschreibung des ASICs wurden die entsprechenden Funktionen als Verhaltensmodell realisiert. Bei der Simulation werden die Eingangssignale des Designs als Stimuli für den Bitmuster-Generator sowie alle Ein- und Ausgangssignale des Designs als Vergleichs-Bitmuster aufgezeichnet.

Die Umsetzung in die FPGA-Technologie war problemlos möglich. In der Netzliste wurden keine „unüblichen“ Zellen wie z.B. RS- oder JK-Flipflops benutzt. Die einzige Besonderheit waren einige D-Flipflops, die mit der negativen Flanke getaktet werden. Aber auch ihre Realisierung stellte im Emulations-FPGA kein Problem dar. Anhand der Stimulierung des Original-ASICs und des Emulations-FPGAs mit den Test-Bitmustern und dem Vergleich der Ausgangsdaten wurde nachgewiesen, dass die Netzliste mit der Realisierung im Original-ASIC übereinstimmt. Der Test des Emulations-FPGAs in den vier Applikationsschaltungen verlief ebenfalls erfolgreich. Es konnte kein unterschiedliches Verhalten zwischen der umgesetzten Netzliste im Emulations-FPGA und dem Verhalten des Original-ASICs festgestellt werden. Die aufgezeichneten Bitmuster des Original-ASICs dienten in allen Verifikationsschritten als Referenzdaten der Entwicklung.

Der nächste Schritt war die Synthese des Designs in die Gate-Array-Technologie. Die Umsetzung der Netzliste stellte ebenfalls kein Problem dar, da in der verwendeten Technologie negativ getaktete Flipflops zur Verfügung stehen. Schwieriger war die Realisierung der Timing-Anforderungen der Ausgangssignale. Diese werden vorwiegend über kombinatorische Verknüpfungen gebildet. Bei der Synthese musste hier ein besonderes Augenmerk auf die realisierte Struktur gelegt werden. In der Prelayout-Simulation und bei der statischen Timinganalyse wurde nachgewiesen, dass das Verhalten der entstandenen Netzliste mit dem Verhalten des Orginal-ASICs in allen Testfällen identisch ist. Das Timing wird unter allen Umgebungsbedingungen (best/typical/worst) und bei der Produktion im schlechtesten Prozess eingehalten. Das vom Halbleiterhersteller erzeugte Layout erfüllt ebenfalls alle Anforderungen.

Die elektrischen Anforderungen an einige Anschlüsse des ASICs sind höher als es die Spezifikation der Gate-Array-Technologie definiert. Es war u.a. notwendig, dass ein Schmitt-Trigger-Eingang bei anderen Spannungsschwellen schaltet und ein Ausgang eine größere Last treiben soll. Diese Anforderungen können mit der Gate-Array-Technologie auch erfüllt werden, u.U. sinkt allerdings bei ungünstigen Prozessbedingungen die Ausbeute. Um mit allen Serienbauelementen die erhöhten Anforderungen zu erreichen, wurden die Parameter im Testprogramm des Halblei-terherstellers angepasst.

Auf Grund des engen zeitlichen Rahmens wurden die Prototypen und die Serienbauelemente parallel in einer Risiko-Produktion gefertigt. Beim Test der Prototypen konnte ohne Einschränkungen eine 100%ige Kompatibilität zum Original-ASIC festgestellt werden. Der leicht erhöhte Stromverbrauch der Prototypen stellte sich als unkritisch heraus. Die Ursache für den leichten Anstieg der Stromaufnahme liegt in den nicht genutzten Zellen des Gate-Array-Masters. Die Verifikation der Prototypen hat „keinerlei Hinweise ergeben, dass sich der Baustein vom Original-ASIC unterscheidet“. Das neue ASIC wird als vollwertiges Ersatz-Bauelement für das Original-ASIC in der Fertigung verarbeitet.

- Redesign abgekündigter ASICs #####

- Ein ASIC mit programmierbarer Logik ersetzen

- Ein ASIC in einer maskenprogrammierbaren Technologie nachentwickeln