Alte Schaltkreise neu entwickeln

Redesign abgekündigter ASICs #####

Fortsetzung des Artikels von Teil 1

Ein ASIC mit programmierbarer Logik ersetzen

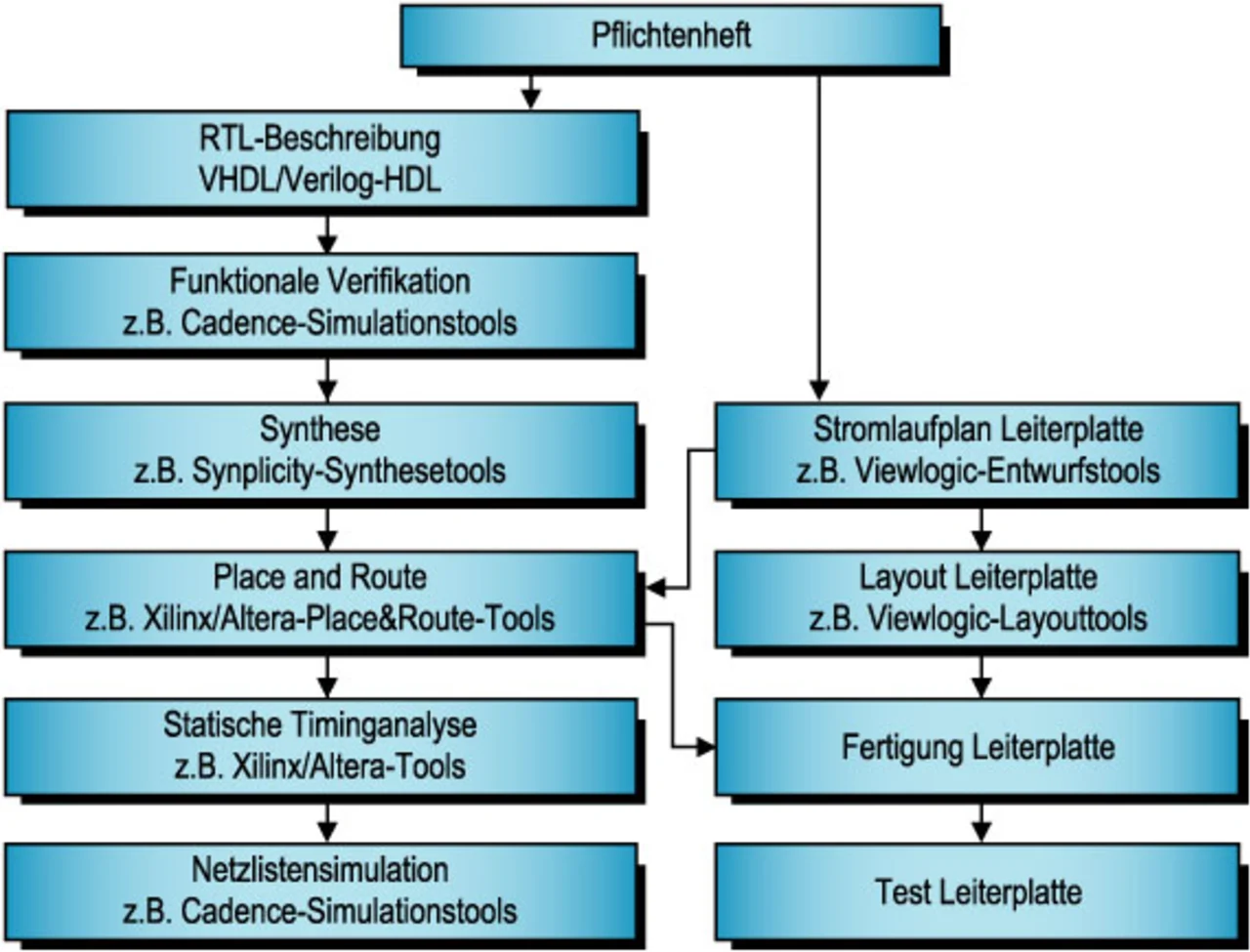

Bild 4 zeigt den Design-Ablauf für programmierbare Logik. Die Erstellung des Pflichtenheftes, die RTL-Beschreibung und die funktionale Verifikation des nachzuentwickelnden ASICs erfolgen analog zum Design-Ablauf für maskenprogrammierbare ASICs. Für die Synthese der programmierbaren Logik werden in der Regel aber andere Werkzeuge genutzt. Nach der Synthese erfolgen das Place&Route sowie die statische Timinganalyse mit herstellerspezifischen Programmen. Zur Verifikation des Designs wird die Netzliste simuliert.

Jobangebote+ passend zum Thema

Weiterhin muss für die programmierbare Logik ein Leiterplattenträger entworfen und gefertigt werden. Die Verdrahtung der Leiterplatte fließt in die Anschlussbelegung der programmierbaren Logik ein. Hier ist eine enge Zusammenarbeit der Entwickler notwendig. Auf dem Leiterplattenträger ist die programmierbare Logik meist über eine JTAG-Schnittstelle (Joint Test Action Group) konfigurierbar. Diese wird in der Entwicklungsphase für die Konfiguration genutzt. In der Produktion werden vorkonfigurierte Bauelemente eingesetzt. Die Verifikation der Funktion des entstandenen Moduls erfolgt in den Applikationen oder mit Hilfe des Serientests des Original-ASICs.

Das Beispiel des Redesigns eines Adressvergabe-ASICs, ebenfalls für die Siemens AG, verdeutlicht diesen Design-Ablauf. Das Redesign erfolgte mit Hilfe eines programmierbaren Schaltkreises auf einem Leiterplattenträger. Das Original-ASIC entstand in einer 2,0-µm-Standard-Zell-Technologie. Die Entwicklungsumgebung ist nicht mehr bekannt.

Das Orginal-ASIC wird in zwei Baugruppen eingesetzt und es werden vorerst 1000 Bauelemente benötigt. Es liegt in einem PLCC68-Gehäuse vor, die Betriebsspannung beträgt 5 V. Durch das relativ große Gehäuse des Original-ASICs ist die Entwicklung eines Leiterplattenträgers mit CPLD als ASIC-Ersatz möglich. Auf Grund der geringen benötigten Stückzahl ist dies die kostengünstigste Variante.

Auch für das Adressvergabe-ASIC war eine ausführliche Spezifikation vorhanden. Leider fehlte zu Beginn des Projekts eine technische Beschreibung der Funktion des Original-ASICs. Als Referenzen standen nur die Test-Bitmuster des Serientests und die verbale Beschreibung der Funktionen des Original-ASICs zur Verfügung. Für das Redesign wurde der folgende Weg gewählt:

- Entwurf eines Leiterplattenträgers im PLCC68-Format.

- Redesign des ASICs anhand der Spezifikation und der Test-Bitmuster.

- Umsetzung auf die CPLD-Technologie.

- Test des ASIC-Ersatzes mit dem Serientestprogramm und in den Applikationen.

Das CPLD für den ASIC-Ersatz hat ein TQFP100-Gehäuse. Dieses Gehäu-se ist mit 14,4 mm Kantenlänge rund 10 mm kleiner als das PLCC68-Gehäuse. Dadurch ist es möglich, die Leiterbahnen auf einer Lage des Leiterplattenträgers zu führen und zugleich die fünf Stützkondensatoren neben dem CPLD zu platzieren (Bild 5). Um eine Reprogrammierung des CPLDs in der Entwicklung vornehmen zu können, sind die vier JTAG-Signale als Testpunkte auf dem Leiterplattenträger verfügbar.

Das Redesign des Original-ASICs gestaltete sich schwierig, da die verfügbaren Informationen (verbale Beschreibung, Test-Bitmuster) für ein Redesign gering waren. Anhand der Beschreibung und der Test-Bitmuster wurde ein HDL-Modell entwickelt. In der Entwurfsphase sind die Test-Bitmuster des Original-ASICs mit den Test-Bitmustern der Simulation des neuen HDL-Modells immer wieder verglichen worden. Die Entwicklung wurde, bis auf wenige Unterschiede zwischen den Test-Bitmustern, vorangetrieben. Je weniger Unterschiede beim Vergleich der Test-Bitmuster vorlagen, um so schwieriger stellte sich die Ummodellierung des HDL-Modells dar.

Glücklicherweise konnte – wenn auch verspätet – die verwendete Schaltung des Original-ASICs als Schaltplan beigestellt werden. Das bisherige Redesign wurde verworfen. Auf Basis der Schaltpläne entstand ein neues HDL-Modell, dass einer 1:1-Kopie des Original-ASICs entspricht. Die erzeugten Test-Bitmuster der HDL-Simulation sind identisch mit den vorhandenen Test-Bitmustern des Serientests.

Bei der Synthese und dem anschließenden Place&Route in der CPLD-Technologie hat sich ein weiteres Problem gezeigt. Nicht alle verwendeten Strukturelemente der Standard-Zell-Bibliothek, wie z.B. RS-Flipflops oder Scan-Flipflops (Flipflop mit vorgeschaltetem Multiplexer für das gezielte Adressieren zu Testzwecken), sind in der CPLD-Technologie verfügbar. Für diese Zellen mussten Ersatzschaltungen entworfen werden, da die automatische Umsetzung der HDL-Beschreibung dieser Funktionen nicht möglich war.

Die Verifikation des ASIC-Ersatzes erfolgte mit Hilfe des Serientestprogramms vom Original-ASIC und in den Applikationen. Für die Verifikation auf dem Tester wurde ein spezieller Adapter für den Leiterplattenträger geschaffen. Das Serientestprogramm prüft nur die logischen Funktionen des Schaltkreises. Das Freigabekriterium für die Entwicklung war der fehlerfreie Test des ASIC-Ersatzes mit den Test-Bitmustern des Original-ASICs. Dieses Ziel wurde mit der Umsetzung der Schaltpläne erreicht.

Die Applikationsschaltungen sind mit dem Leiterplattenträger neben den funktionalen Tests auch EMV- und Stresstests z.B. in einer Klimakammer unterzogen worden. Die Verifikation des ASIC-Ersatzes verlief erfolgreich. Nach der Fertigung der 1000 neuen „ASICs“ ist die Bestückung der Baugruppen mit den Modulen in der Fertigung problemlos möglich.

| Dipl.-Ing. (FH) Dirk Bernerist in Schmölln geboren. Er studierte Elektrotechnik in der Fachrichtung Informationstechnik an der FH in Jena. Seit seiner Diplomarbeit im Jahr 1999 ist er bei der MAZeT GmbH angestellt. Als Projektleiter im Bereich Chipdesign & Opto-elektronik umfasst sein Aufgabengebiet den Entwurf digitaler Systeme für FPGA-, Gate-Array- und Standard-Zell-Technologien. E-Mail: berner@mazet.de |

Verwandte Artikel:

- Redesign abgekündigter ASICs #####

- Ein ASIC mit programmierbarer Logik ersetzen

- Ein ASIC in einer maskenprogrammierbaren Technologie nachentwickeln