PC-Prozessor statt DSP?

Fortsetzung des Artikels von Teil 4

PC-Prozessor statt DSP?

Die Verwendung von Vektoroperationen hat des Weiteren gravierende Auswirkungen auf das Design der Algorithmen-Implementierungen.

Jobangebote+ passend zum Thema

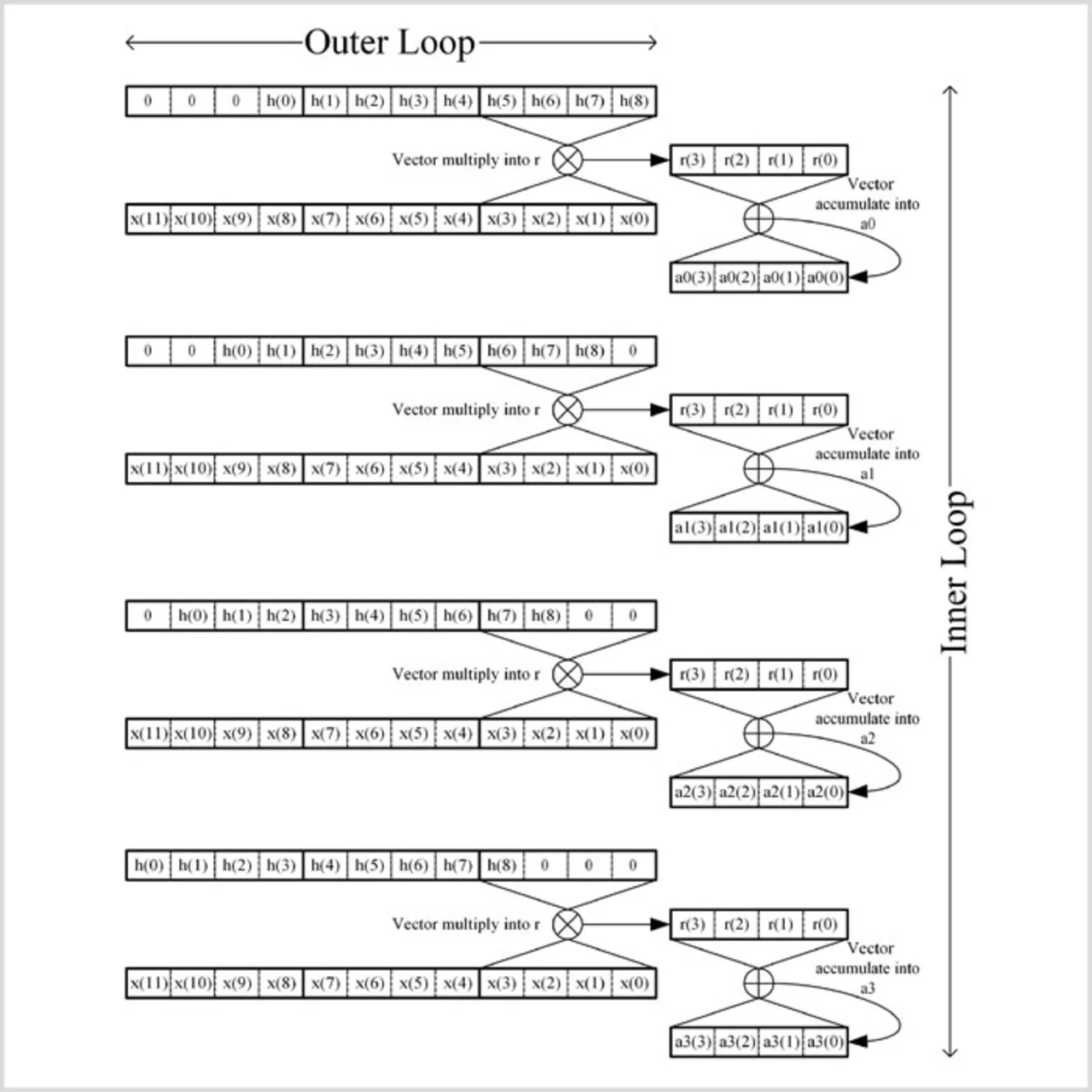

Die Anpassung einer Implementierung an eine SIMDArchitektur nennt sich Vektorisierung. Bild 1 zeigt eine vektorisierte Implementierung eines FIR-Filters (Finite Impulse Response), in der ein Vektor vier Werte enthält. Zu Beginn einer jeden Iteration der äußeren Schleife wird ein Vektor mit Signalproben aus dem Speicher geholt. In der inneren Schleife multipliziert der Prozessor vier Koeffizienten-Vektoren mit dem Signalproben-Vektor, die Ergebnisse summiert er in vier Akkumulatoren auf. Nach der letzten Schleife befinden sich in diesen Akkumulatoren Teilsummen, die zum Produzieren von vier Ergebniswerten kombiniert werden müssen. Hierbei ist hervorzuheben, dass dieser Prozess in verschiedenen Bereichen ineffizient ist. Zum Beispiel muss eine Reihe von Multiplikationen mit Null explizit ausgeführt werden, und außerdem sind vier Tabellen mit Filterkoeffizienten zu erstellen (eine Tabelle für jeden Offset der Koeffizienten innerhalb der Vektorstruktur). Alternative Strukturen können für Filter mit wenigen Koeffizienten besser geeignet sein, und sogar eine skalare Implementierung kann sich als beste Variante herausstellen.

Die Sache mit dem Cache

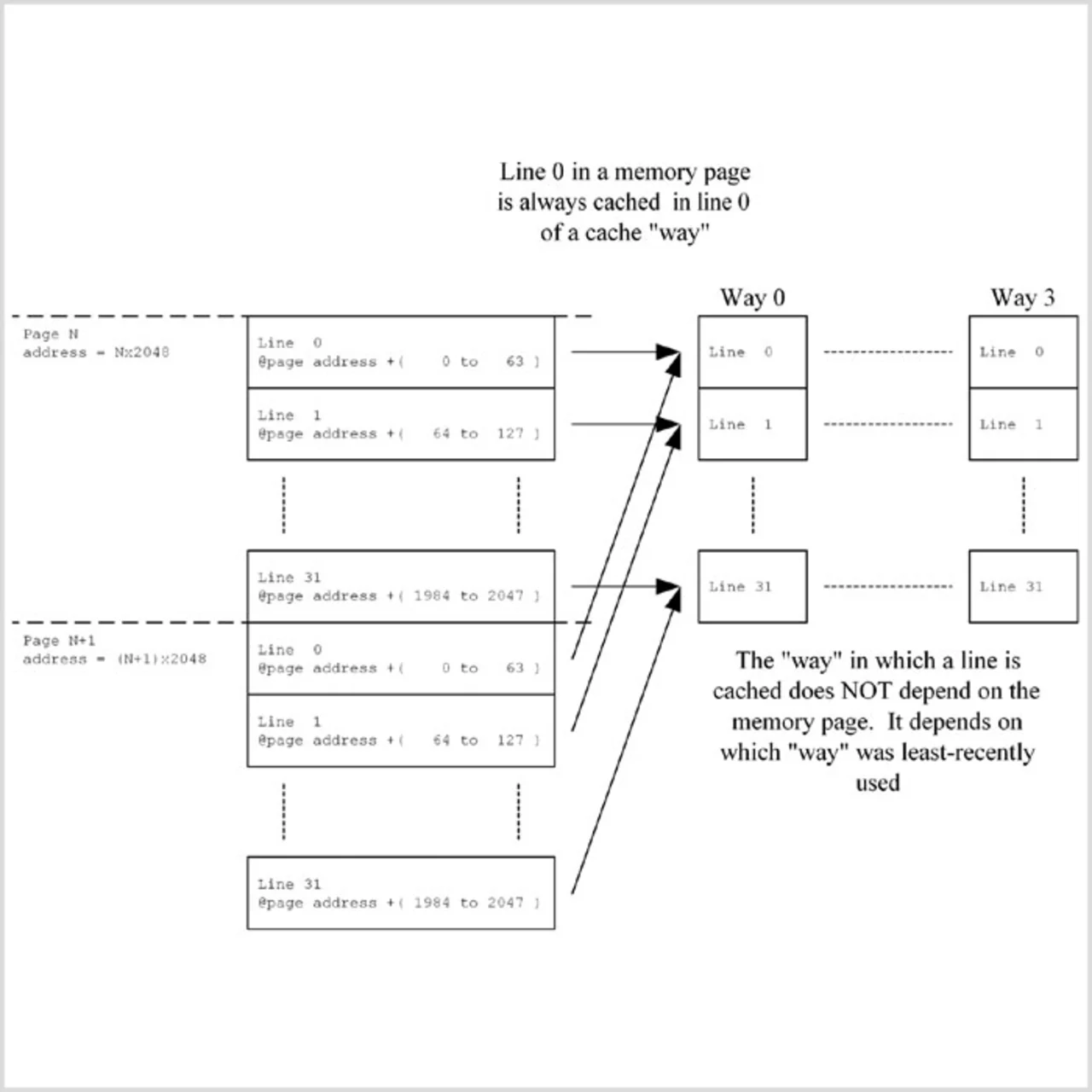

Das Speichermanagement ist meist derjenige Faktor, der die weitreichendsten Auswirkungen auf die Performance einer PC-CPU hat, da der eigentliche Hauptspeicher (gegenüber dem Speicher eines DSP-Systems) stets langsam ist. Dieser Speicherengpass betrifft übrigens nicht nur DSP-Algorithmen, sondern die gesamte auf einem PC laufende Software. Aus diesen Gründen haben die Prozessorhersteller viel Erfindergeist in das Design von Cache-Speichern investiert, um die Langsamkeit des Speichers wirksam zu kompensieren. Die Cache-Systeme der verschiedenen PC-CPUs unterscheiden sich erheblich. Als Beispiel soll hier der Level-1-Daten-Cache des »Pentium 4« dienen (Bild 2). Dabei handelt es sich um einen »4-Way Set Associative «-Cache mit jeweils 64 Byte langen Zeilen und einer Kapazität von 8 KByte. Speicherinhalte werden stets in Blöcken zu je 64 Byte im Cache abgelegt. Welche Zeile im Cache verwendet wird, hängt von der Adresse des ersten Bytes in dieser Zeile ab, die logischerweise immer ein Vielfaches von 64 ist. Fünf Bits der Adresse dienen zur Identifikation einer von 32 Zeilen, die sich zum Cachen eines bestimmten Datenblocks nutzen lassen. Jede Zeile wird somit zum Ablegen einer ganzen Reihe verschiedener Adressregionen (Pages oder Seiten) verwendet. Um zu verhindern, dass eine Cache-Zeile durch den ersten Zugriff von/aus einer ebenfalls dieser Zeile zugeordneten Adresse überschrieben wird, gibt es für jede Zeile vier »Ways«. Überschrieben wird stets derjenige Weg, dessen Nutzung am längsten zurückliegt.

Aus dieser Architektur ergeben sich verschiedene Konsequenzen:

- Wird ein Cache-Zugriff nicht fündig (Cache Miss), sind 64 Bytes aus dem Speicher (bzw. bei vielen CPUs aus dem Level-2-Cache) zu laden, auch wenn nur ein einziges Byte benötigt wird. Cache-Misses kosten deshalb viel Verarbeitungszeit.

- Wird ein Datenblock, den ein Algorithmus braucht, auf den Beginn einer Zeile ausgerichtet, kommt es für das erste Byte zu einem Cache-Miss, doch die nächsten 63 Bytes werden im Cache gefunden, falls sie benötigt werden.

- Werden die Daten nicht sequenziell benötigt, ist Sorgfalt bei der Anordnung der Daten im Speicher erforderlich. Im ungünstigsten Fall kann es bei jedem vierten Zugriff zu einem Cache-Miss kommen, wenn die Daten von Adressen mit Abständen von jeweils 2048 gelesen werden (diese Daten werden von verschiedenen Seiten denselben Cache-Zeilen zugewiesen). Ein Beispiel wäre ein Algorithmus, der nacheinander Bytes mit jeweils demselben Offset aus mehreren 2048 Byte fassenden Puffern lesen muss. Bei jedem vierten Lesezugriff kommt es hier zu einem Cache-Miss. Würde man die Puffergröße hier auf 2112 Bytes (2048 + 64) anheben, richteten sich die Lesezugriffe an verschiedene Cache-Zeilen und es käme deutlich seltener zu Cache-Misses.

- PC-Prozessor statt DSP?

- Schnelle Evaluierung

- Cache-Misses vermeiden

- PC-Prozessor statt DSP?

- PC-Prozessor statt DSP?

- Sind PC-Prozessoren wie der »Pentium« die besseren DSPs? Tatsächlich sind solche CPUs oft mit deutlich höherer Frequenz getaktet als DSPs. Und da sie oft im Gaming-Bereich eingesetzt werden, unterstützen viele von ihnen beispielsweise auch komplexe Vektoroperationen. Doch welche Vor- und Nachteile hat es, PC-Prozessoren als DSPs einzusetzen?