CMOS-Bildsensoren mit integrierten Bildverarbeitungsstufen

Optimierung von SoC-Bildsensoren

Fortsetzung des Artikels von Teil 2

Optimierung von SoC-Bildsensoren

Bei den SoC-Bildsensoren sind daher lediglich ein Oszillator und eine entsprechende Spannungsversorgung extern vorzusehen. Aus diesem Grund erfreuen sich SoC-Bildsensoren einer steigenden Nachfrage, gerade in kostensensitiven Anwendungsgebieten.

Es ist offensichtlich, dass die oben genannten Funktionsblöcke über eine Vielzahl von Parametern verfügen und jede Änderung dieser Parameter eine andere sichtbare Auswirkung im Bild hat. Die Anzahl der möglichen Parameter ist sensor- und herstellerspezifisch. So hat beispielsweise die SoCLinie von Aptina (früher Micron) – erkennbar an der Teilenummer MT9_1__ – folgende Mindestanzahl von Parametern: LC > 50, CCM > 20, AE > 20, AWB > 40, Gamma > 10, FBAS-Encoder > 10 und weitere > 10 Parameter zur generellen Ansteuerung und zum Verhalten bei dunklen Szenen (Low Light Performance). Ausgeliefert werden SoC-Bildsensoren in der Regel mit einem Standardsatz von Parametern, die für eine bestimmte Optik-Filter-Kombination und durchschnittliche Szenenanforderungen – Regelgeschwindigkeiten und Verhalten der AE und AWB – optimiert sind. Dadurch ist die oben genannte minimale Konfiguration möglich.

Jobangebote+ passend zum Thema

Aus technischen und wirtschaftlichen Gründen wird es auch weiterhin Non-SoC-Bildsensoren geben – bei Aptina z.B. erkennbar an der Teilenummer: MT9_0__. Dabei handelt es sich um Bildsensoren, die letztlich nur aus einem Sensor-Array nebst dazugehöriger Ansteuerung und einem ADU bestehen. Gerade Bildsensoren mit einer Auflösung von > 3 MPixel und insbesondere HDR-Sensoren (High Dynamic Range, wie z.B. die MT9V022/023/032/033-Serie von Aptina) werden noch auf die Integration einer vollständigen Color Pipeline verzichten müssen. Die Color Pipeline wird dann in der Regel in einem externen DSP oder FPGA realisiert, oft in Kombination mit weiteren Kamerafunktionen und der eigentlichen Applikations-Software.

Der jeweilige DSP- bzw. FPGA-Programmierer muss in diesem Fall neben seiner eigentlichen Applikation auch die vollständige Color Pipeline aufbauen und parametrieren können. Zusätzlich müssen die spezifischen Eigenschaften des Sensors berücksichtigt werden. Soll z.B. ein 5-MPixel-Bild mit 12 Hz ausgelesen und verarbeitet werden, so entspricht dies 60 MPixel pro Sekunde. Eine Color Pipeline benötigt pro Pixel mindestens 40 Rechenoperationen, so dass etwa 2,4 Giga-Rechenoperationen pro Sekunde nur für die Pipeline benötigt werden. Offensichtlich kann dies nur mit leistungsfähigen DSPs oder FPGAs realisiert werden.

Die ersten CMOS-Bildsensoren waren lediglich mit einer Pixelmatrix und der dazugehörigen analogen Ausleseelektronik ausgestattet und benötigten daher zusätzliche externe Bauelemente wie ADUs (Analog/Digital-Umsetzer), FPGAs (Field Programmable Gate-Arrays), DSPs (Digitale Signalprozessoren) oder/und Signal-Encoder.

Mittlerweile sind ein digitaler Datenausgang und eine digitale Parametrierung bei CMOS-Bildsensoren standardmäßig vorhanden. Sensoren mit dieser minimalen Ausstattung werden auch als Non-SoC-Sensoren bezeichnet.

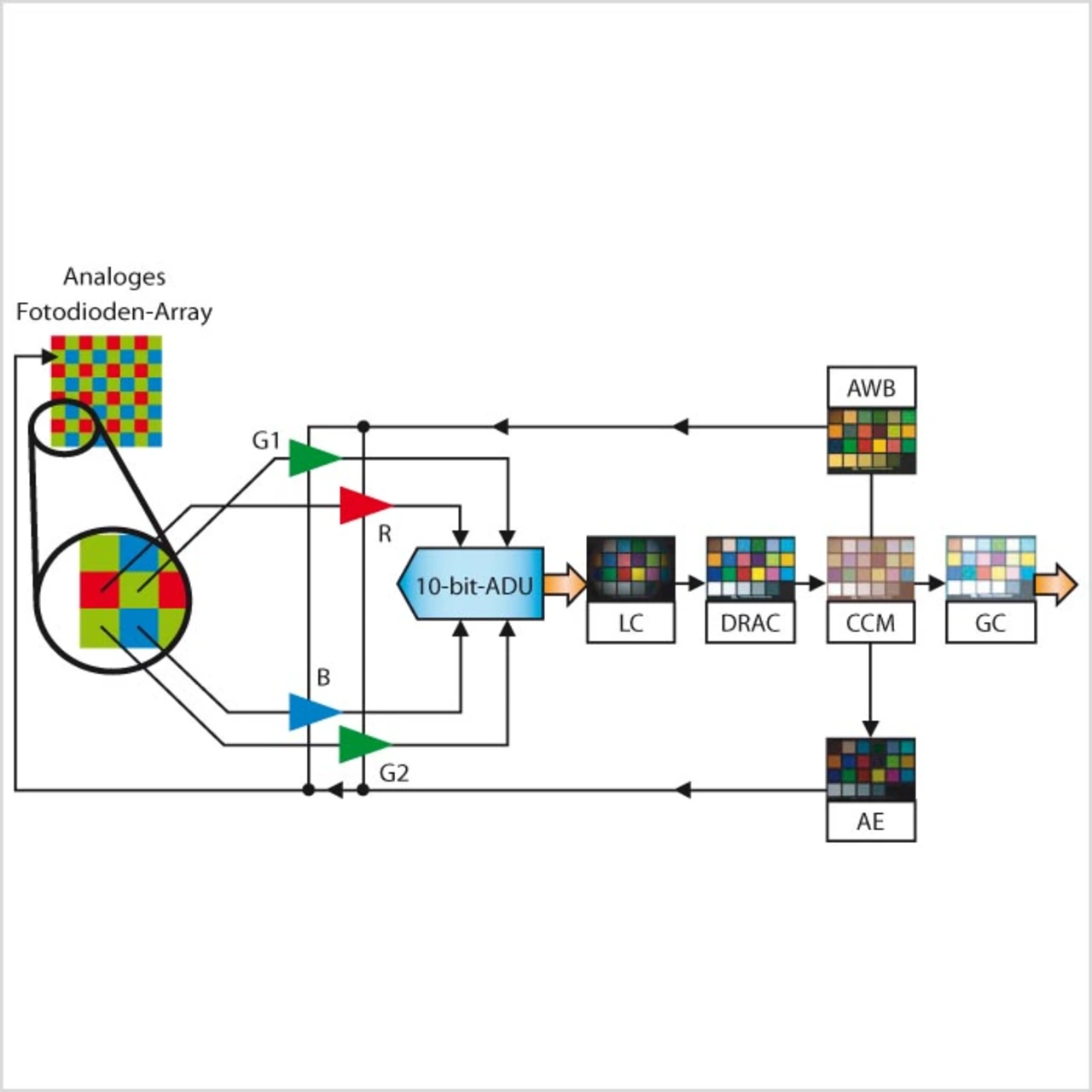

Enthält der Sensor zusätzlich noch Bildvorverarbeitungsblöcke, wie z.B. Farb-Demosaikfunktionen – z.B. nach dem Bayer-RGB-Muster –, Farbraumumwandlungen oder auch JPEG-Codecs, so spricht man von Systemon-Chip-Sensoren. Ein SoC-Sensor enthält in der Regel alle Funktionsblöcke, die notwendig sind, um aus den Rohdaten des Sensors ein RGB-Bild – auch als Color Pipeline bezeichnet – zu generieren (Bild 1).

Durch direkte Integration von digitalen, analogen und Mixed-Signal-Funktionseinheiten zusammmen mit dem Bildsensor auf einem Chip sind auf kleinstem Raum kostengünstige Implementierungen von komplexen Bildverarbeitungsprozessen realisierbar.

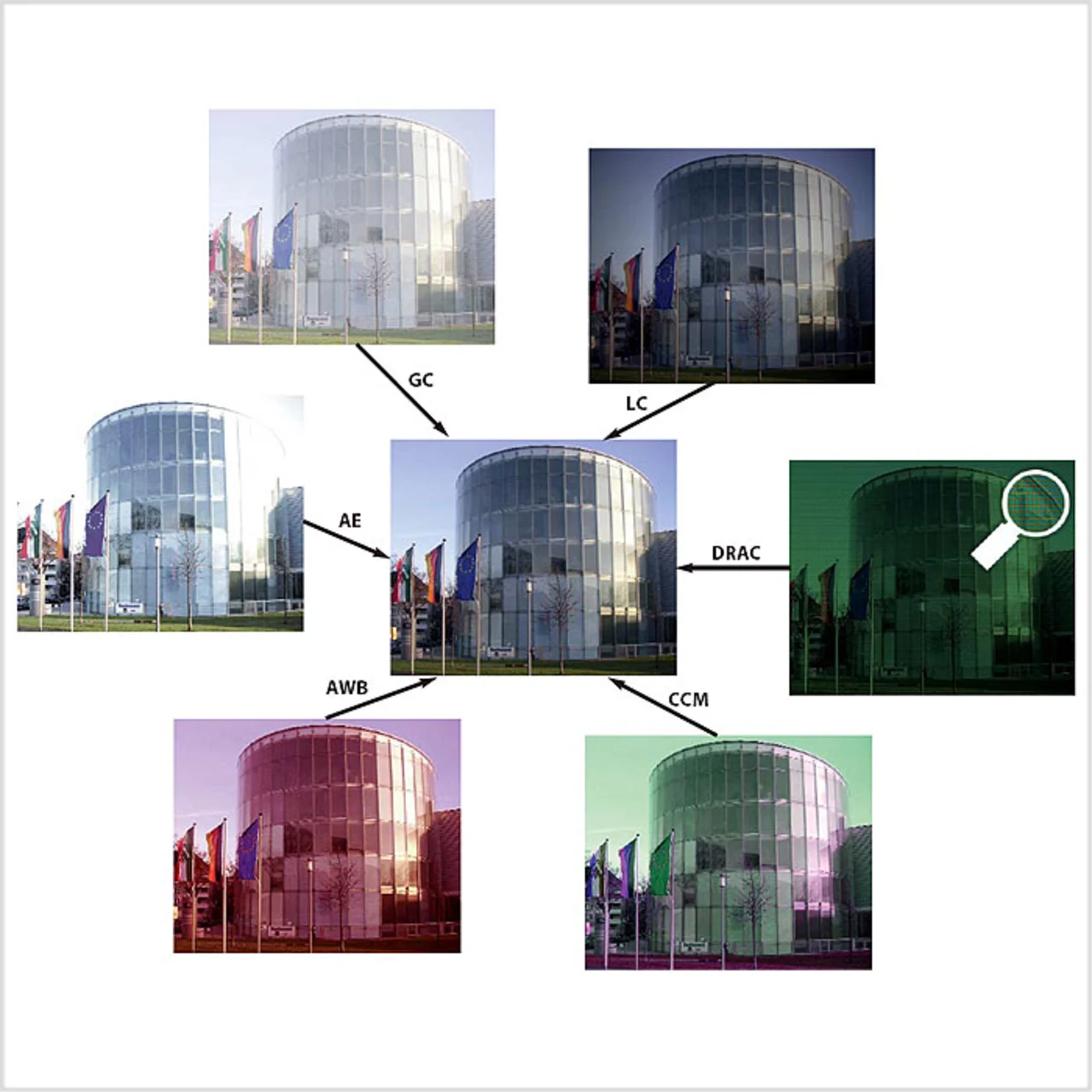

Die Funktionsblöcke eines SoC-Bildsensors im Überblick (Bild 2):

- LC (Lens Shading Correction): Bei Weitwinkelobjektiven und bei Sensoren mit Mikrolinsen kommt es zu Vignettierungseffekten. Diese zeichnen sich durch eine abnehmende Farb-/ Bildhelligkeit zum Sensorrand hin aus. Die Folge ist im Fall der Bildhelligkeit eine Art Tunnelblick und im Fall der Farbhelligkeit ein farbfleckiges Bild. Die Vignettierungseffekte können für jeden Farbkanal und für jede Richtung unterschiedlich ausfallen und müssen daher einzeln und richtungsabhängig korrigiert werden.

- DRAC (Demosaic, Resize and Aperture Correction): Die meisten CMOSBildsensoren verfügen als Farbsensoren über ein so genanntes Bayer-RGB-Filter. Dieses Farbfilter ist ein Grund dafür, dass jede Fotodiode des Bildsensors nur über eine Farbinformation verfügt. Beim Bayer-Filter ist eine Zeile mit Grün-Rot-Grün-Rot-Pixeln und die folgende Zeile mit Blau-Grün-Blau-Grün-Pixeln bestückt. Diese verteilten Farbinformationen werden so interpoliert (Demosaic), dass für jedes Pixel anschließend alle drei Farbkomponenten (RGB) vorliegen. Notwendige Bildskalierungs- (Resize) und Nachschärfeoperationen (Aperture Correction) werden in diesem Funktionsblock ebenfalls durchgeführt.

- Optimierung von SoC-Bildsensoren

- Autor:

- Optimierung von SoC-Bildsensoren

- Optimierung von SoC-Bildsensoren