Low-Power-Mikrocontroller

Mehr Performance ohne mehr Strom

Mehr Leistung bedeutet in modernen Embedded Systemen nicht immer mehr Rechenleistung, denn immer mehr Anwendungen - nicht nur batteriebetriebene - fordern einen möglichst geringen Stromverbrauch. Dorthin führt der Weg nur über moderne Halbleiterprozesse und innovative Stromspartechniken, die im Mikrocontroller implementiert sind.

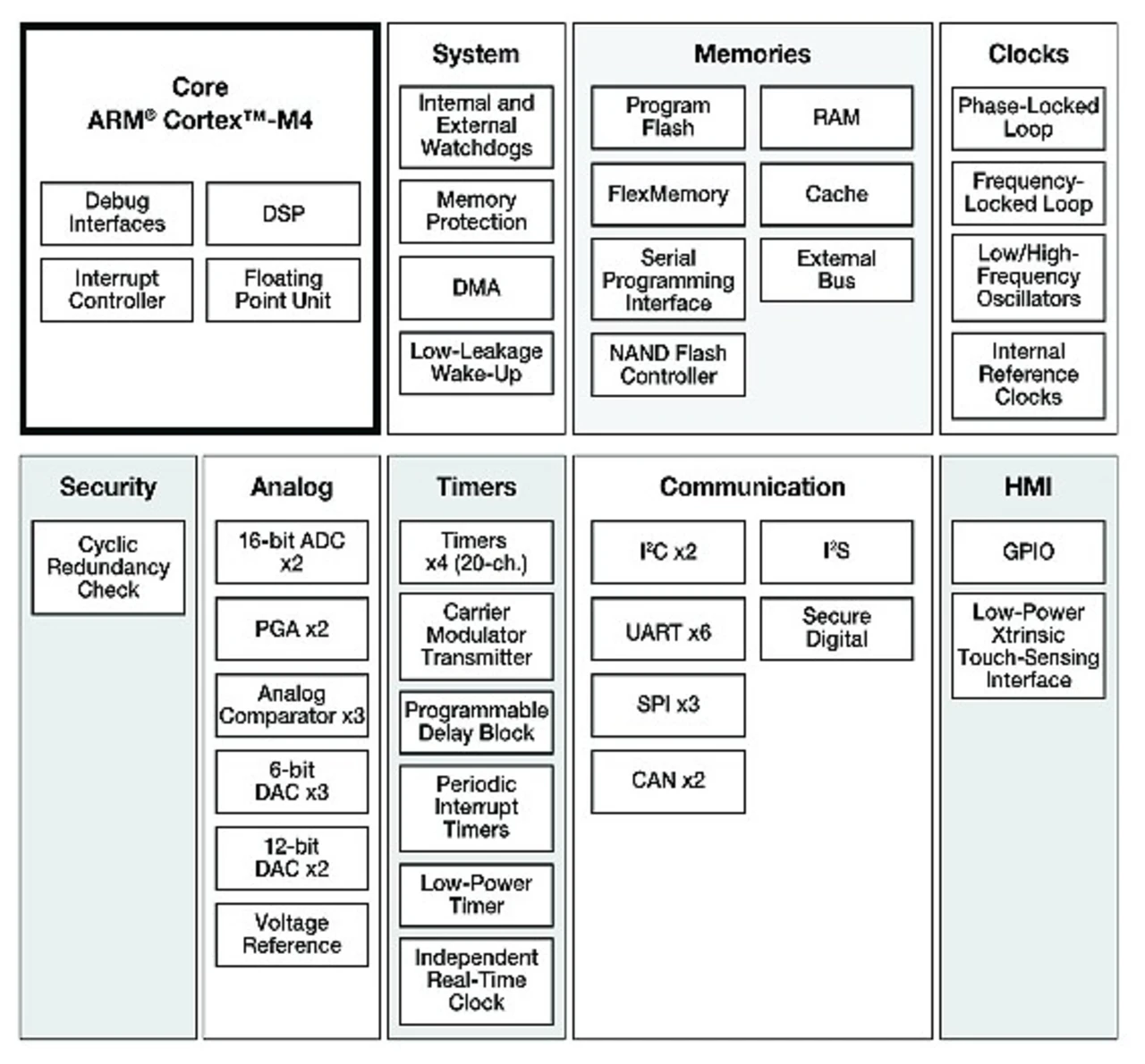

Um diesen Bedürfnissen gerecht zu werden, hat Freescale die neue Mikrocontrollerfamilie »Kinetis« entwickelt, die auf dem Rechenkern »ARM Cortex-M4« basiert (Bild 1).

Das Produktspektrum reicht von äußerst kompakten Bausteinen im QFN-Gehäuse mit 50 MHz und 32 KByte Flashspeicher bis zu solchen mit 150 MHz Taktfrequenz, 1 MByte Flashspeicher und umfangreichen, für den industriellen Einsatz konzipierten Peripheriemodulen.

Bei der Entwicklung der Kinetis-MCUs spielte der Stromverbrauch eine zentrale Rolle.

Die Prozesstechnologie ist der Startpunkt eines jeden Halbleiterprodukts und ein Schlüsselfaktor für die Definition des Stromverbrauchs eines Mikrocontrollers.

Jobangebote+ passend zum Thema

Die Kinetis-MCUs sind die ersten Produkte, die von der »SG-TFS«-Flash-Technologie (Split Gate Thin Film Storage) des Herstellers profitieren, die zudem extrem kurze Zugriffszeiten und hohe Immunität gegen Ladungsverluste bieten soll. Für die Realisierung der SG-TFS-Bitzelle hat Freescale schnelle Niederspannungstransistoren im Lesepfad integriert, die mit niedrigeren Betriebsspannungen von 1,71 V bis 3,6 V auskommen.

In Anwendungen, die aus zwei 1,5-V-Batterien versorgt werden, ist meist bei einer Spannung von 0,9 V pro Batterie Schluss.

Die mit 1,71 V niedrigere Spannungsschwelle bietet gegenüber herkömmlichen, üblicherweise auf Spannungen von 2 V oder darüber angewiesenen MCUs eine deutlich längere Batterieaufzeit.

Dieser erweiterte Spannungsbereich bezieht sich nicht nur auf die auf dem Chip integrierten Speicherbereiche - Flash, SRAM und das neue Freescale-eigene »FlexMemory« (ein konfigurierbares, robustes EEPROM) -, sondern auch auf die analogen Peripheriemodule. Damit soll selbst am unteren Ende des Spannungsbereichs eine kontinuierliche Messung und Aufbereitung von Signalen gewährleistet sein.

Die Spannungscharakteristika, die der Halbleiterprozess ermöglicht, reduzieren darüber hinaus auch den Betriebsstrom, denn nun lassen sich auch schnelle Signale bei geringen Spannungen (typisch 1,2 V) verarbeiten. Weil der Betriebsstrom proportional zu C · U2 · f ist, wirkt sich das Absenken der Spannung äußerst positiv auf den Stromverbrauch des Flashspeichers im aktiven Betrieb aus.

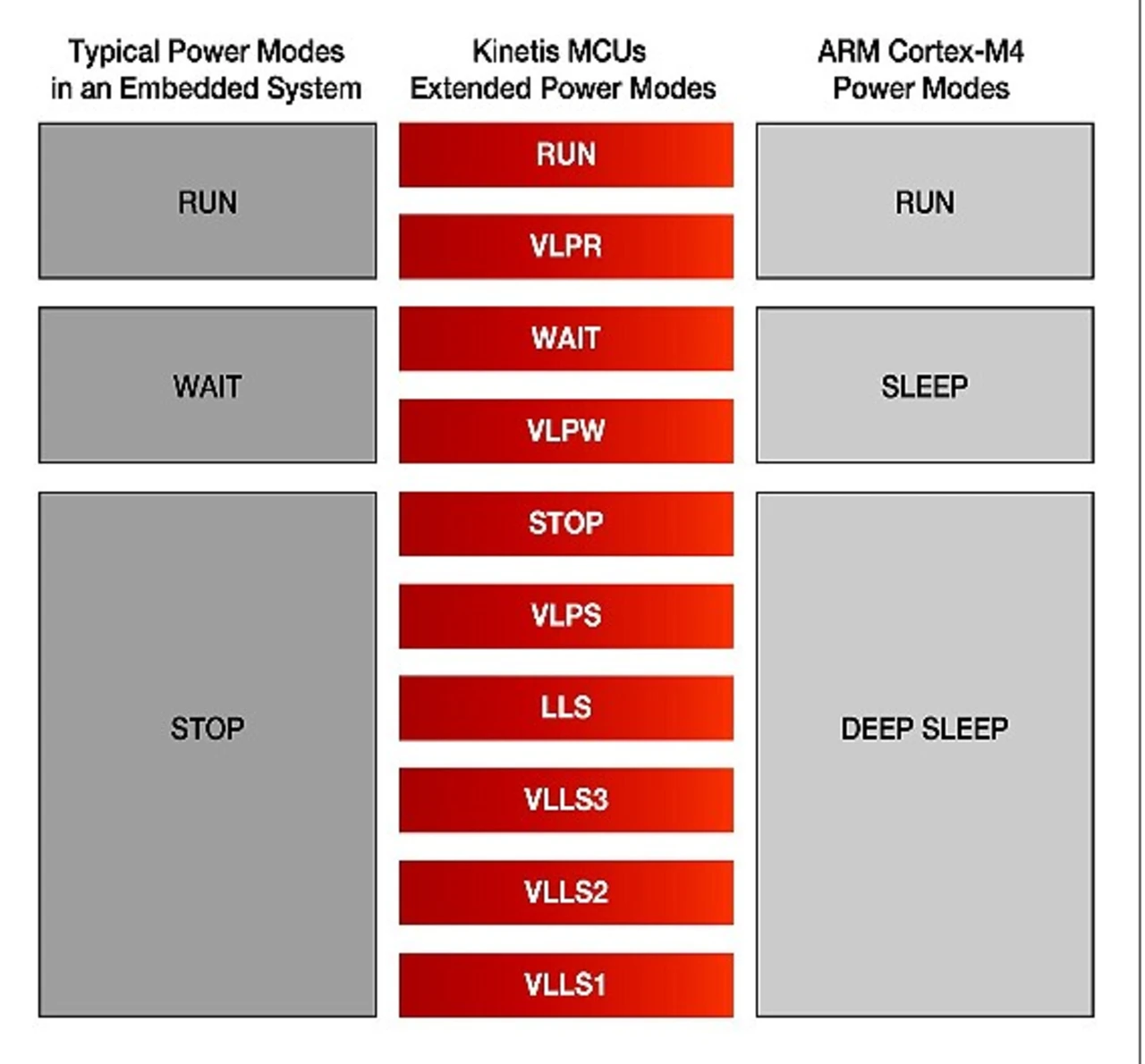

Zehn verschiedene Betriebsmodi

In der Mehrzahl batteriebetriebener Geräte arbeitet die CPU die meiste Zeit im Stromspar- oder Schlafmodus. Ein Mikrocontroller muss daher eine attraktive Kombination aus Betriebsarten, Weckquellen und Reaktionszeiten bieten, damit Entwickler die Aktivität der Peripherie und die Reaktionszeiten auf die Anforderungen der jeweiligen Applikation optimieren und so die verfügbare Batterieleistung optimal nutzen können.

Freescale hat seine Kinetis-MCUs daher mit zehn Betriebsmodi wie »Low-Power Run«, »Wait« und »Stop« sowie mehreren Weckquellen ausgestattet (siehe Bild 2 und Tabelle 1).

Jeder Run-Modus verfügt über einen entsprechenden Wait- und Stop-Modus.

Darüber hinaus hat Freescale mehrere leckstromarme Modi sowie einen neuen Wake-up-Controller mit besonders geringen Leckströmen konzipiert, um auch sehr aggressiven Energievorgaben gerecht zu werden

Im Run-Modus verarbeitet die CPU den Softwarecode mit voller Geschwindigkeit, wobei sie mit einer Stromaufnahme von 200 µA/MHz auskommen kann.

Wird der maximale Bustakt nicht benötigt, so bietet sich der VLPR-Modus (Very Low Power Run) an. Der CPU-Takt wird auf 2 MHz gedrosselt, und der integrierte Spannungsregler wird in den Standby-Modus gefahren, während die Funktion der Peripherie und die Erkennung von Unterspannung (Low Voltage Detect, LVD) voll gewährleistet ist.

| Power-Modus | Kurzbeschreibung |

|---|---|

| Run |

MCU kann auf voller Geschwindigkeit laufen. |

| Wait |

Erlaubt den Peripherieblöcken zu arbeiten, während sich die CPU schlafen legt. |

| VLP Run |

Die maximale Taktfrequenz für CPU und Peripherie ist auf 2 MHz begrenzt. Der Zugriff auf das Flash liegt bei maximal 1 MHz. LVD (Low Voltage Detect) ist ausgeschaltet. |

| VLP Wait |

Ähnlich wie VLP Run, allerdings ist die CPU im Schlaf-Modus. |

| Stop |

MCU befindet sich in einem statischen Zustand. Dies ist die stromsparendste Betriebsart, bei der alle Register erhalten werden, während der LVD aktiv ist. |

| VLP Stop |

MCU befindet sich in einem statischen Zustand, während LVD ausgeschaltet ist. Dies ist der stromsparendste Power-Modus, bei dem ADC, LPT, RTC, LCD, HSCMP, DAC und Interrupt-Pins aktiv sind. |

| LL Stop |

MCU wird in einen Low-Leakage-Erhaltungsmodus versetzt. Die LLWU (Low-Leakage Wake-up Unit) überwacht die Weckquellen einschließlich LPT, RTC, LCD, HSCMP, DAC und ausgewählte Interrupt-Pins. |

| VLL Stop3 |

MCU ist in einem Low-Leakage-Mouds, bei dem fast die ganze interne Logik heruntergefahren wird. Der System-RAM-Inhalt wird erhalten wie auch die I/O-Stati. Die LLWU überwacht die gleichen Weckquellen wie im LL-Stop-Modus. |

| VLL Stop2 |

Ähnlich wie VLL Stop3, wobei nur ein Teil des System-RAM-Inhalts erhalten wird. Der Inhalt des FlexRAM kann optional erhalten werden. |

| VLL Stop1 |

Ähnlich wie VLL Stop3, wobei nur die 32 Byte große Registerdatei erhalten wird. |

Tabelle 1: Alle Power-Modi der Kinetis-MCUs und ihre Bedeutung

Je nach Rechenleistung, Speicherausbau und Peripheriekonfiguration bewegt sich die Stromaufnahme im VLPR-Modus zwischen 600 µA und 1 mA. Der Wait-Modus und der »Very Low Power Wait«-Modus (VLPW) verhalten sich äquivalent zu den entsprechenden Run-Modi, nur dass die CPU angehalten wird und die Programmierung des FlexMemory nicht möglich ist.

Sind die Interrupts der Peripheriefunktionen aktiviert, so kann damit die MCU aus dem Wait-Modus geholt werden, die vorgesehene Aufgabe ausführen und sich dann gleich wieder in einen Stromsparmodus begeben. So lässt sich die durchschnittliche Stromaufnahme von Applikationen minimieren, die häufig zwischen Aktiv- und Stromsparmodus umschalten müssen.

Je nach Busfrequenz reduziert sich der Betriebsstrom gegenüber dem Run-Modus um 30 bis 60 Prozent. Bei den diversen Stop-Modi bleiben die im Betrieb herrschenden Zustände und die teilweise oder volle Deaktivierung bestimmter Logikgruppen beziehungsweise des Speichers erhalten.

Der »Low-Leakage Stop«-Modus (LLS) ist am stromsparendsten, was man sich aber mit einer Reaktionszeit von 4 µs erkauft. Durch Absenken der Spannung für die interne Logik und die Minimierung der Leckströme von nicht benutzten internen Schaltkreisen lässt sich eine typische Stromaufnahme (LDD) von 1,2 µA bis 7 µA erreichen. Die »Very Low-Leakage Stop«-Modi (VLLS) gehen noch einen Schritt weiter: Sie deaktivieren auch die interne Logik und optional auch das RAM und eliminieren so die Leckströme aus den nicht benötigten Schaltkreisen.

Die einzelnen VLLS-Modi unterscheiden sich im Wesentlichen in Bezug auf die Erhaltung des RAM-Speichers. Im VLLS3-Modus bleibt das RAM voll erhalten, VLLS2 gewährleistet die Erhaltung von Teilbereichen, und im VLLS1-Modus wird das RAM nicht erhalten. Jedoch steht für kritische Applikationsdaten noch ein 32 Byte großes Register zur Verfügung.

Eine Schlüsselkomponente der Kinetis-MCU ist die so genannte »Low-Leakage Wake-Up Unit« (LLWU), welche die Koordination der Weckvorgänge aus allen Low-Leakage-Stop-Modi übernimmt. Die LLWU unterstützt bis zu sechzehn externe Eingangspins (diese können wahlweise auf fallende beziehungsweise steigende Flanken oder auf alle Übergänge reagieren) sowie bis zu acht interne Peripheriemodule, die der Anwender als Weckquelle konfigurieren kann.

Im Modus mit der geringsten Stromaufnahme stehen gleich mehrere Weckquellen zur Verfügung: ein Low-Power-Timer, die Echtzeituhr (Real-Time Clock), ein Analogkomparator, das Touchsensing-Interface (TSI) sowie mehrere Pin-Interrupts. Die Weckeingänge werden - falls so konfiguriert - aktiviert, sobald die MCU in den LLS-Modus oder in einen der VLLS-Modi fährt. Da die Taktversorgung mit bis zu 40 Prozent zur Stromaufnahme im aktiven Betrieb beiträgt, hat man für die Kinetis-MCUs ein programmierbares Clock-Gating für alle Module vorgesehen.

Im Run- und Wait-Modus werden so nicht genutzte Takte abgeschaltet, ohne jedoch Rechenleistung oder Funktion in irgendeiner Weise zu beeinträchtigen. Dies kann sich angesichts der Zahl von Kommunikationsmodulen und Timern, welche die Bausteine mitbringen, als besonders wichtig erweisen. Darüber hinaus werden Schaltungsteile wie inaktive Speicherbereiche und Logik über das so genannte »Power Gating« komplett abgeschaltet, wodurch die Leckströme noch weiter sinken.

Die Mikrocontroller verfügen über einen »Low Power Timer«, durch den das System durchgängig im Stromsparmodus arbeiten kann. Er kann entweder als normaler Timer genutzt werden oder die Ausgangsimpulse der auf dem Chip integrierten Komparatoren zählen. Und schließlich unterstützt eine so genannte »Low-Voltage Detection Unit« (LVD) die Voreinstellung von zwei Triggerpunkten mit vier möglichen Warnschwellen pro Triggerpunkt. Sie lässt sich so konfigurieren, dass sie bei Schwankungen der Versorgungsspannung einen Reset beziehungsweise einen Interrupt auslöst und auf diese Weise die Speicherinhalte und die Systemzustände der MCU schützt.

- Mehr Performance ohne mehr Strom

- Mehr Performance ohne mehr Strom