Low-Cost-FPGAs in 65 nm

Fortsetzung des Artikels von Teil 2

Low-Cost-FPGAs in 65 nm

Pdynamisch=[0,5 x CU2 + QKurzschluss x U] x f x Aktivität Kurzschluss - Ladevorgang während des Schaltens |

Energieoptimierte 65-nm-FPGAs

Jobangebote+ passend zum Thema

Will ein Halbleiterhersteller die Herausforderungen bezüglich der Leistungsaufnahme bei 65 nm meistern, so sollte er auf einen „Low-Power“-Prozess zurückgreifen sowie Prozessoptimierungen, Power-Analyse und Optimierungstechniken ausschöpfen.

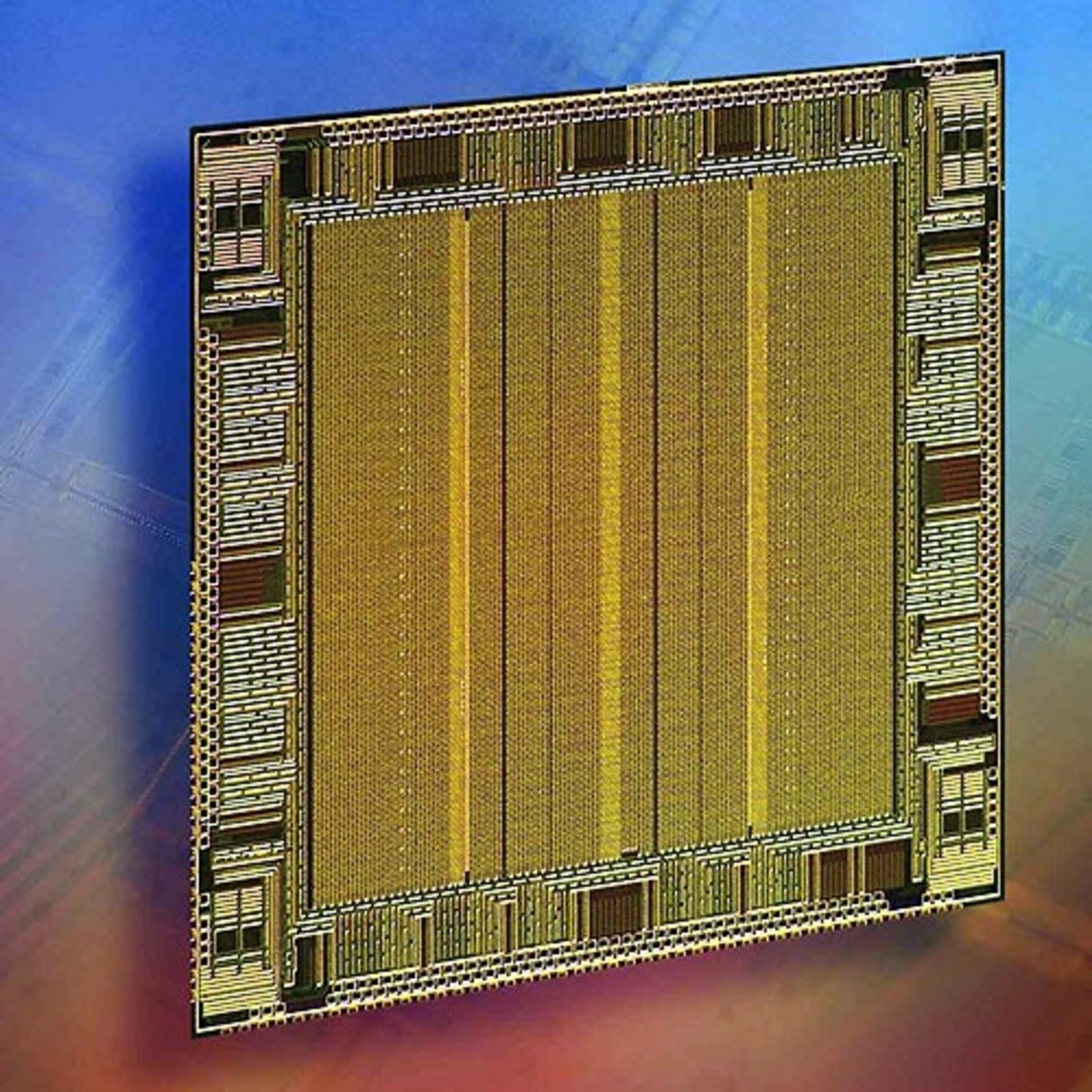

Die meisten Halbleiter- Foundries bieten spezielle Prozesse an, die für Low- Power-Anwendungen optimiert sind (z.B. die 65-nm-Low-Power- Technologie von TSMC, mit der die Cyclone-III-FPGAs gefertigt werden; Bilder 3 und 4). Diese Prozesse kommen vorwiegend bei der Fertigung von Chips für portable und Consumer- Anwendungen wie DVRs, DVD-Spieler und portable Media-Player zum Einsatz. Solch ein Low-Power-Prozess ist im Hinblick auf die Geschwindigkeit und die Leckströme fein abgestimmt und nutzt mehrere Schwellenspannungen, Transistoren für mehrere I/O-Spannungen und Transistoren mit unterschiedlichen Kanal-Längen. Low-Power-Bausteine verfügen über ein dickeres Gate-Oxid als Mehrzweck- Bausteine. Damit geht zwar ein wenig Geschwindigkeit verloren, aber der Leckstrom im Stand-by-Modus lässt sich exponentiell verringern. Außerdem kommt in diesem Fall eine Methodik mit Low-Power-Bibliotheken, IP und Design-Referenz-Flow zum Einsatz, bei der Prozess- und Design- Technologie eng gekoppelt sind.

Ein geringerer Betriebsstrom bedeutet weniger Komponenten und geringere Bausteintemperaturen. Das wiederum wirkt sich positiv auf die Systemzuverlässigkeit aus. Wenn die Betriebstemperatur eines Bausteins nur um 10 K reduziert wird, verdoppelt sich die Lebensdauer des Bausteins. FPGAs mit einer geringeren Leistungsaufnahme führen somit zu mehr Leistung, geringeren Kosten und höherer Zuverlässigkeit des Gesamtsystems.

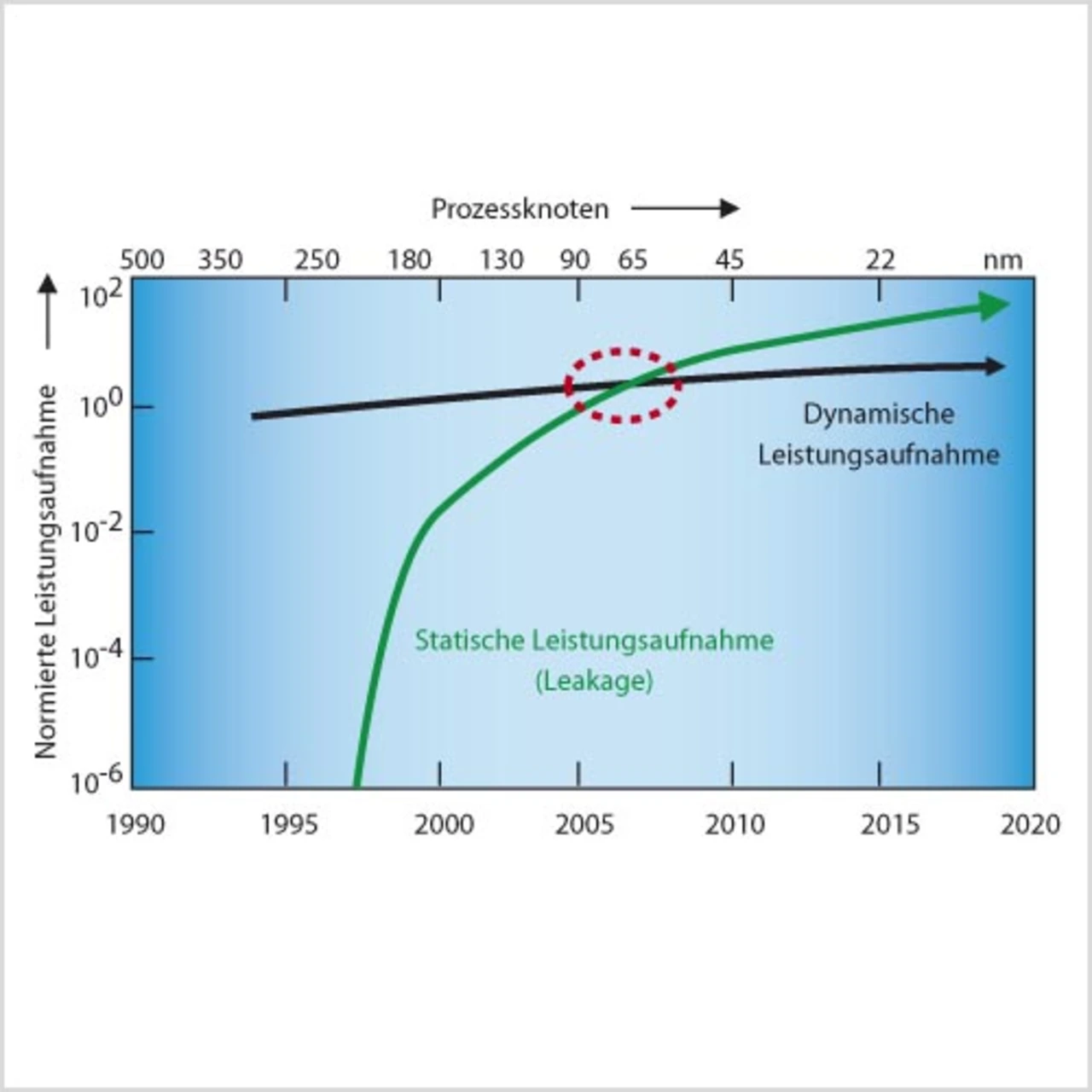

Die Leistungsaufnahme setzt sich zusammen aus der statischen und der dynamischen Leistungsaufnahme. Mit dem Schritt zu kleineren Geometrien und höherer Systemgeschwindigkeit steigt die dynamische Leistungsaufnahme. Aber mit kleineren Prozessstrukturen sinken auch die Kern-Spannungen, so dass die steigende dynamische Leistungsaufnahme wieder handhabbar wird. Das – kombiniert mit der Tatsache, dass kleinere Prozessgeometrien auch kleinere parasitäre Kapazitäten (verbunden mit kleineren Transistoren) und kürzere, weniger parasitäre Verbindungen zwischen der Logik ermöglichen, führt dazu, dass die dynamische Leistungsaufnahme nur minimal ansteigt. Auf der anderen Seite steigt die statische Leistungsaufnahme aufgrund von steigenden Transistorleckströmen exponentiell an. Bild 1 zeigt, dass bereits bei 65-nm-Strukturen die statische Leistungsaufnahme die dynamische übersteigt.

Eine bewährte Regel in der Halbleiterphysik sagt: Verringert sich die Transistorlänge, dann steigt der Leckstrom. Kleinere physikalische Abstände machen den Strom anfälliger dafür, als Verluststrom abzufließen. Sowohl der Leckstrom zwischen Source und Drain als auch der Gate-Leckstrom sind umgekehrt proportional zur Kanallänge und zur Dicke des Gate-Oxids und steigen dadurch mit kleineren Prozessstrukturen dramatisch an.

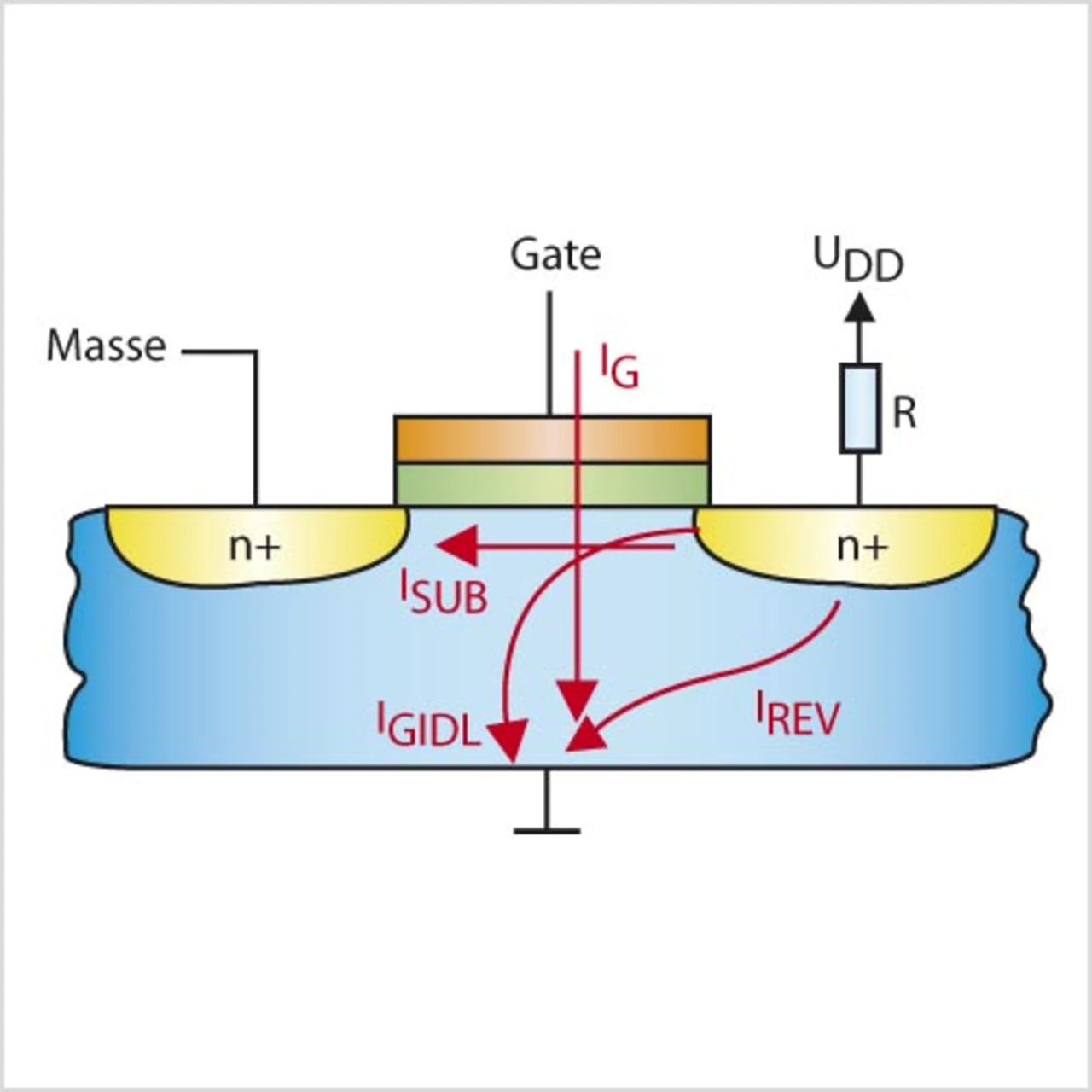

Leckströme zwischen Source und Drain: Der Leckstrom zwischen Source und Drain, auch bekannt als Subthreshold-Strom (ISUB), stellt den größeren Teil der Leckströme dar (Bild 2). In diesem Fall fließt der Leckstrom von der Quelle (Source) des Transistors zur Senke (Drain), auch wenn der Transistor abgeschaltet ist. Je kleiner der Transistor, desto schwieriger ist es, diesen Stromfluss zu unterbinden. Deshalb weisen 65-nm-Transistoren einen Source- Drain-Leckstrom auf, der um Größenordnungen über dem von größeren Transistoren liegt, während alle anderen Parameter gleich bleiben. Hinzu kommt noch, dass der Source-Drain-Leckstrom exponentiell mit der Temperatur wächst (z.B. vergrößert er sich um den Faktor 5, wenn die Sperrschichttemperatur Tj von 25 auf 85 °C steigt).

Eine weitere Herausforderung bei der Fertigung stellt die Dicke des Gate-Oxids dar. Dünnere Oxidschichten ermöglichen, dass der Transistor schneller geschaltet werden kann. Aber gleichzeitig steigt mit der dünneren Oxidschicht auch der Leckstrom. Die Größe des Leckstroms ist außerdem von der Schwellenspannung des Transistors abhängig. Die Schwellenspannung UT sagt aus, ab welcher Spannung im Kanal Strom zwischen der Quelle (Source) und der Senke (Drain) fließt. Kleine hochschnelle Transistoren benötigen eine kleinere Schwellenspannung, die durch die Oxiddicke und die Dotierung beeinflusst wird. Wenn man die Geschwindigkeit, mit der der Transistor durch die Gate- Elektrode an- und abgeschaltet wird, aufrechterhalten will, steigt der Leckstrom, weil der Transistorkanal nicht mehr vollständig abgeschaltet werden kann.

Der Gate-Leckstrom stellt eine weitere Herausforderung dar, auch wenn er nicht so hoch ist wie der Subthreshold- Leckstrom. Während der Gate- Leckstrom bei 65-nm-Strukturen steigt, nimmt die Dicke des Gate-Oxids ab. Anders als der Leckstrom zwischen Source und Drain nimmt der Gate- Leckstrom mit steigender Temperatur nur unwesentlich zu.

- Low-Cost-FPGAs in 65 nm

- Low-Cost-FPGAs in 65 nm

- Low-Cost-FPGAs in 65 nm