Neue Technologien bei Hochleistungs-IGBTs

Fortsetzung des Artikels von Teil 1

Neue Technologien bei Hochleistungs-IGBTs

Neben der ausgezeichneten Leistung wird eine sehr hohe Immunität gegenüber Kurzschlüssen (Latch up) erwartet, da die p-leitende Säule als Löcher-Strompfad funktioniert und einen geringeren Löcherstrom unter der n+-Emitterregion erlaubt, wodurch der Kurzschluss-Strompegel erhöht wird. Der Scheitelwert der Elektronenstromdichte ist beim SJFS-IGBT niedriger und zeigt einen gleichmäßiger verteilten Löcherstrom. Diese Charakteristik ist sehr hilfreich zur Reduzierung der Temperaturerhöhung bei einem Betrieb mit hohen Strömen wie z.B. im Kurzschlussbetrieb.

Bild 9 zeigt den Verlauf des Kurzschlussstroms für die beiden IGBTs wenn der maximale Kurzschlussstrom fließt. Ein Teil der Kurzschlussströme fließt beim SJFS-IGBT auch entlang der p-leitenden Säule, wodurch eine regelmäßigere Temperaturverteilung mit niedrigerem Scheitelwert erreicht wird (Bild 10). Dieser Unterschied im Betrieb des SJFS-IGBT führt im Vergleich zu einem typischen FS-IGBT zu einer höheren Haltbarkeit. fr

Jobangebote+ passend zum Thema

Nach der Dickenreduzierung erfolgen nacheinander die Anoden-Implantierung, die Aktivierung und die Metallisierung. An diesem Punkt wird der Prozess der Anodenaktivierung zu einer erneuten Herausforderung, da die zulässigen Temperaturen beim Tempern aufgrund der bestehenden vorderen Metallschichten begrenzt sind. Aus diesem Grund sind rasches thermisches Tempern oder ein Tempern mit gepulsten Laserstrahlen wünschenswert.

Tempern mit gepulsten Laserstrahlen

Die Anodenstruktur von NPT- und FS-IGBTs wird auf der Rückseite des dickenreduzierten Wafers gebildet, nachdem die oberen Strukturen hergestellt wurden. Deswegen sind die Prozesse für die Rückseite bei dünnen Wafern wie die Anoden-Implantierung, Aktivierung und Metallisierungsprozesse auf der Rückseite besonders schwierig. Der Aktivierungsprozess nach der Anoden-Implantierung sollte daher bei einer niedrigeren Temperatur ausgeführt werden, die für die obere Oberflächenmetallschicht kein Problem darstellt und 500 °C nicht überschreitet.

Der konventionelle Aktivierungsprozess führt zu niedrigeren Aktivierungsraten, so dass die Steuerung der Durchlass- und Sperrcharakteristik des IGBT eingeschränkt wird. In dieser Hinsicht kann das Tempern mit gepulsten Laserstrahlen effektiver sein, da es eine rasche lokale Erwärmung des Wafers in geringer Tiefe erlaubt, ohne dass sich die Temperatur auf den ganzen Wafer auswirkt. Es steht fest, dass das Tempern mit gepulsten Laserstrahlen erfolgreich zur Anoden-Aktivierung von IGBTs eingesetzt werden kann und dabei eine Aktivierungsrate von mehr als 80 % erreicht wird [2]. Bei Anodenstrukturen mit hoher Aktivierung lassen sich IGBTs mit ultra-niedrigem Leitungsverlust realisieren.

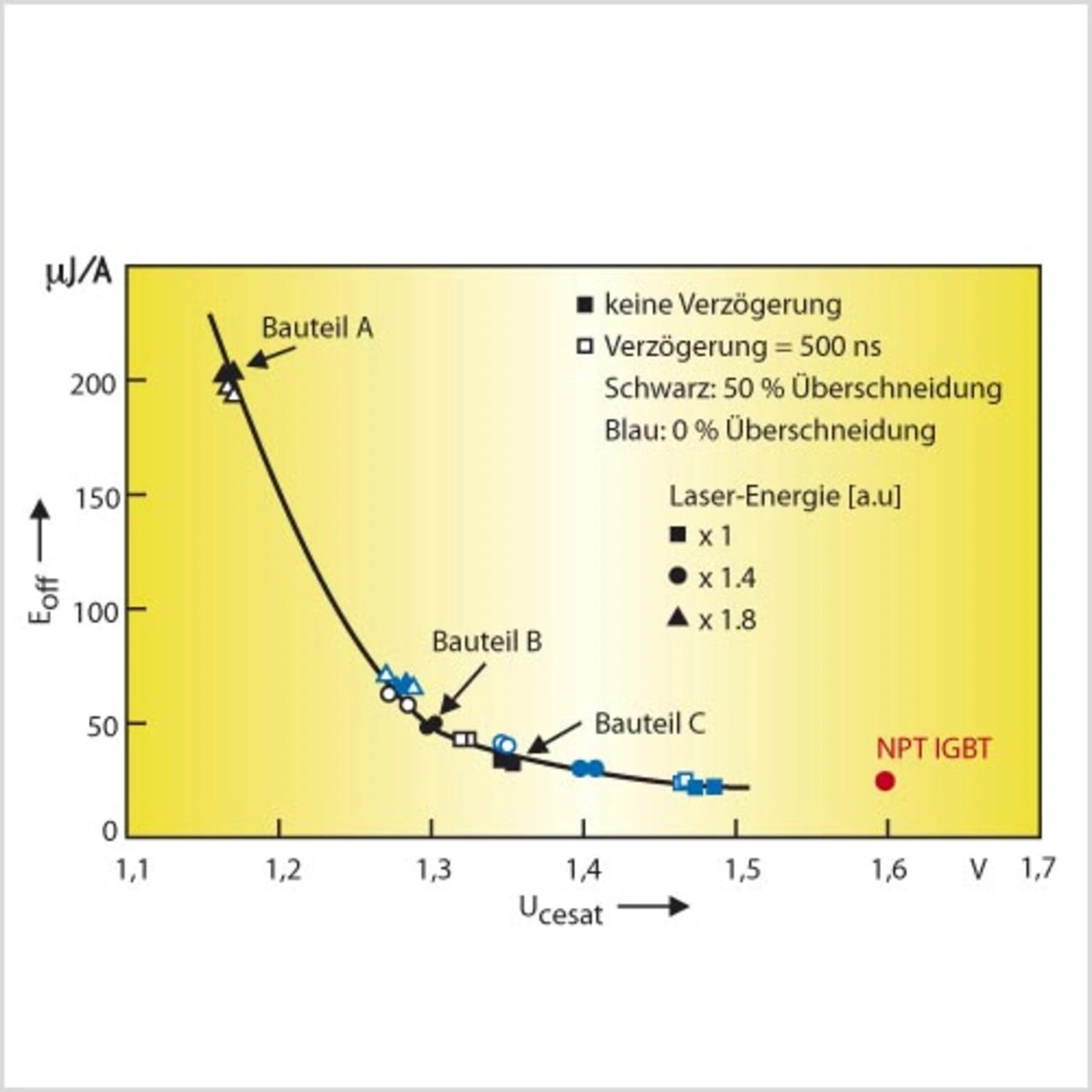

Bild 6 zeigt den Leistungskompromiss zwischen Ucesat und der Abschaltenergie Eoff eines 600-V-NPT-IGBT, hier dargestellt für ein Bauteil bei Tempern mit gepulsten Laserstrahlen im Vergleich mit thermischem Tempern bei niedriger Temperatur im Diffusionsofen. Die mittels Tempern mit gepulsten Laserstrahlen hergestellen IGBTs zeigen mit zunehmender Energiedichte des Lasers eine größere Leistungsbandbreite.

Wenn das Tempern des Bauteils im konventionellen Diffusionsofen erfolgt, zeigt der IGBT eine Spannung Ucesat von 1,6 V und eine Abschaltenergie Eoff von 25 μJ/A. Der mittels Laser-Tempern hergestellte NPT-IGBT zeigt im Einschalt-Zustand einen Spannungsabfall von 1,17 V bis 1,49 V bei einer Kollektorstromdichte von 165 A/cm², während Eoff von 23 μJ/A bis 200 μJ/A reicht, womit sich ein weiter Bereich für Kompromisse ergibt.

Von den Versuchsergebnissen lässt sich theoretisch ableiten, dass eine Feinabstimmung des Bauteilverhaltens durch eine genaue Steuerung der Laserstrahlung möglich ist.

Super-Junction-FS-IGBT

Obwohl das FS-Konzept (Feld-Stop) die Vorteile der Thin-Wafer-Technologie, aber auch das Prinzip der PT-Struktur nutzen kann, sind ein hoher spezifischer Widerstand des Substrats und eine endliche Dicke der Drift-Schicht unbedingt erforderlich. Dies begrenzt damit den Spielraum für eine weitere Verbesserung der Bauteilleistung.

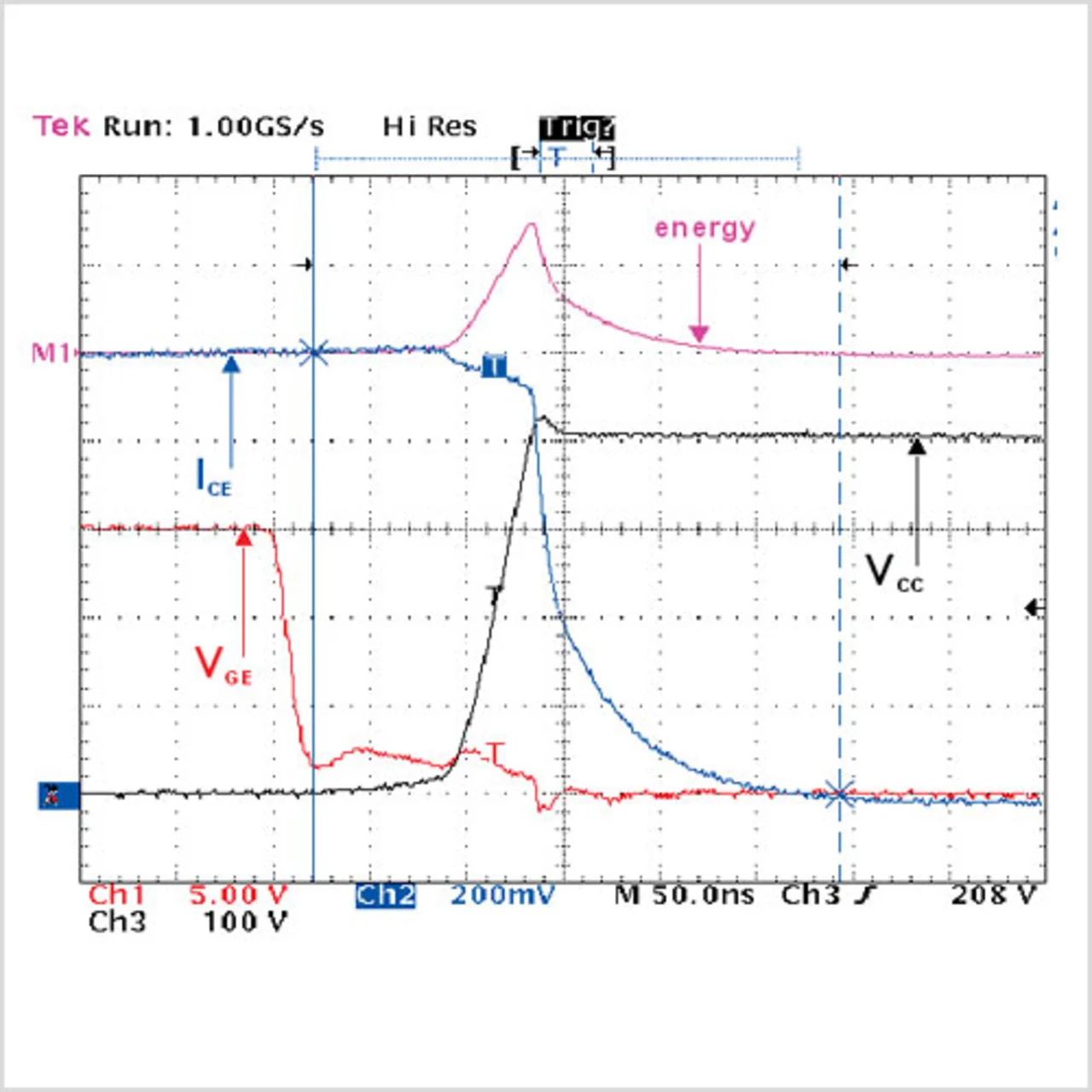

Im transienten Betrieb, wenn die Gate-Emitter-Spannung unter die Schwellenspannung sinkt, beginnt die Kollektor-Emitter-Spannung linear zu steigen (Bild 2). Nachdem die Kollektorspannung Ucc (im Bild Vcc) erreicht, nimmt der IGBTStrom ab, wobei ein geringer Reststrom aufgrund der gespeicherten Minoritätsladungsträger im n-Driftgebiet erhalten bleibt. Die meisten Schaltverluste entstehen während dieses Zeitraums wegen des Reststroms, der das Schaltverhalten der IGBTs beschränkt. Da bei IGBTs ein Kompromiss zwischen Leitungsverlust und Schaltverlust gefunden werden muss, wurden umfassende Forschungen für neuartige Design- und Prozesskonzepte durchgeführt. In dieser Hinsicht können die Thin-Wafer-Technologie, Tempern mit gepulsten Laserstrahlen (Pulsed Laser Annealing) und Super-Junction-IGBTs als neuartige Technologien für fortschrittliche IGBTs betrachtet werden.

Da Thin-Wafer-basierende IGBTs, wie NPT- oder FS-IGBTs, keine Lebensdauereinstellungen der Minoritätsträger benötigen, führt eine höhere Ladungsträger-Lebensdauer zu einem geringeren Spannungsabfall im Einschalt-Zustand. Auch kann durch die Optimierung des Injektionswirkungsgrads der Anode eine schnelle Schaltleistung erreicht werden. Überdies sind aufgrund der reduzierten Dicke die thermische Stabilität sowie die Haltbarkeit besser als bei einem typischen PT-IGBT.

In dieser Hinsicht benötigen mittels der Thin-Wafer-Technologie hergestellte IGBTs sehr dünne Wafer von weniger als 100 μm Dicke. Im Allgemeinen erfordern 600-V-NPTIGBTs Wafer mit 90 bis 110 μm und 1200-V-IGBTs Wafer mit 160 bis 200 μm. Noch dünnere Wafer werden für FS-IGBTs benötigt. Deshalb ist ein Prozess für ultra-dünne Wafer für IGBT-Bauteile entscheidend. Ein derartiger 6-Zoll-Wafer mit 100 μm für NPTIGBTs ist in Bild 3 zu sehen.

Wie in Bild 3 ersichtlich ist, müssen auch Verformung und Durchbiegung beachtet werden. Die Fertigung von Hochleistungs-IGBTs mit solchen unebenen Wafern ist sehr komplex, da die aufeinander folgenden Prozessschritte nicht einfach weiter fortgesetzt werden können und ein hohes Risiko für den Bruch des Wafers besteht. Dadurch gehören der Prozess zur Dickenreduzierung des Wafers und die dazugehörigen Prozessschritte zu den größten Herausforderungen in der Herstellung fortschrittlicher IGBTs.

Die wichtigsten Prozessschritte der Thin-Wafer-Technologie sind in Bild 4 dargestellt. Nach der Fertigung der oberen Strukturen erfolgt die Dickenreduzierung des Wafers. Da die Grundoberfläche sehr rauh ist, sollte das Polieren des Wafers nach der Reduzierung der Dicke erfolgen, um einen Bruch des Wafers zu vermeiden. Bild 5 zeigt die rauhen Oberflächenschichten nach dem Schleifen der Rückseite und die saubere Oberfläche nach der anschließenden Ätzung zur Glättung der beschädigten rauhen Schichten.

- Neue Technologien bei Hochleistungs-IGBTs

- Neue Technologien bei Hochleistungs-IGBTs