Dynamische Blindleistungskompensation

Fortsetzung des Artikels von Teil 1

Anforderungen an eine neue FPGA-Architektur

Eine Analyse der beschriebenen Probleme zeigt, dass vor allem zwei Faktoren begrenzend wirken – die „zweidimensionale“ Formgebung der verwendeten Funktionsblöcke und die Anordnung der I/O-Blöcke entlang der Kanten des Die. Beim Übergang auf modernste Fertigungsprozesse wird daher eine neue FPGA-Architektur erforderlich, wenn man die Skalierbarkeit, die Verarbeitungsleistung und die Stromversorgungsqualität der Bausteine verbessern will.

Eine andere Verteilung der I/O-Blöcke ist der Schlüssel zu kürzeren Verbindungen. Zudem eröffnet dies mehr Freiheitsgrade für die Anordnung der Funktionsblöcke im Baustein. Mit dem Flip-Chip-Verfahren lassen sich diese Anforderungen erfüllen. Diese Technik erlaubt eine Anordnung der Verbindungen vom Chip mit der Außenwelt (Leiterplatte) über den ganzen Die verstreut und ermöglicht so kürzere Verdrahtungsstrukturen mit den damit verbundenen Vorteilen.

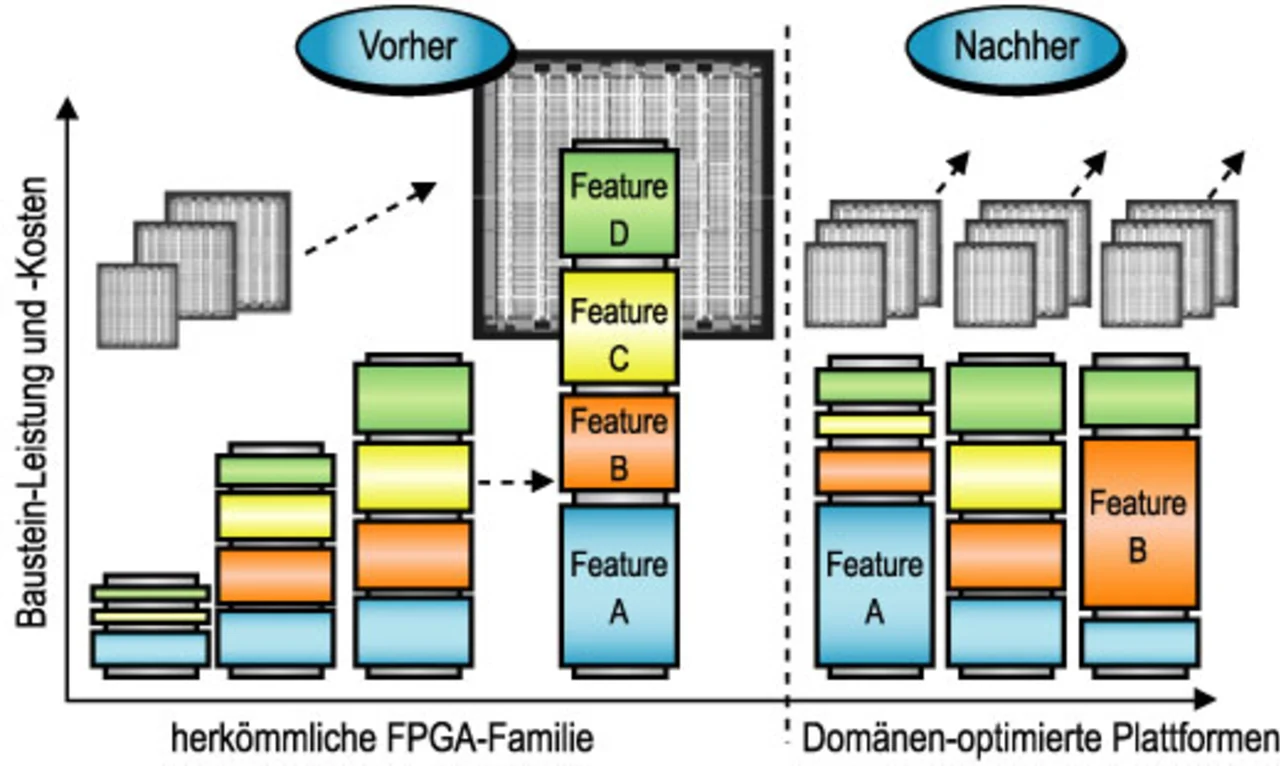

Einfache Anpassbarkeit des Bausteins an unterschiedliche Anwendungen ist eine der Stärken des FPGA-Konzepts. Im Zeitalter des Systems-on-Chip (SoC) bieten moderne FPGAs eine Palette unterschiedlicher Funktionsblöcke wie z.B. Gatter, Register, Controller, digitale Signalprozessoren, I/O-Kanäle und Speicherfunktionen. Weil aber die verschiedenen Anwendungen auch einen unterschiedlichen Mix dieser Funktionsblöcke erfordern, wären FPGAs mit einer festen Zusammensetzung dieser Funktionsblöcke nicht wirtschaftlich: Benötigt man von einer bestimmten Funktion mehr Elemente als gerade vorhanden, so müsste man sehr schnell ein größeres Bauteil verwenden, obwohl zahlreiche andere Funktionsblöcke ungenutzt blieben. Dies lässt sich durch einen Domänen-optimierten FPGA-Aufbau vermeiden. Solche Bausteine sind für unterschiedliche Anwendungsbereiche optimiert (Bild 4). Domänen-optimierte FPGAs benötigen weniger Fläche, sind daher kostengünstiger und verbrauchen weniger Strom als traditionelle, nicht-spezifische FPGAs.

Jobangebote+ passend zum Thema

Die „ASMBL“-Architektur

Die „Advanced Silicon Modular Block“-Architektur nutzt Flip-Chip-Gehäusetechnik und bringt die Anschlusspunkte zur Außenwelt in das Die-Innere. Die verschiedenen Funktionsblöcke in dieser FPGA-Architektur sind aber nicht mehr kachelförmig, sondern in Form von Säulen angeordnet (Bild 1, rechts) – einschließlich der I/O-Kanäle. Bei einer solchen Anordnung steht die verfügbare Die-Fläche nicht mehr in einer starren Beziehung zur Anzahl der I/O-Kanäle, wodurch sich das auf den Baustein abgebildete Design wesentlich leichter skalieren lässt.

Die Anordnung dieser Blöcke ist für den Anwender vollständig transparent – und sie erfordert auf der Benutzerseite keine Veränderungen im Designprozess, weil sich die Blöcke von ihrer Funktion her genauso ansprechen lassen wie in der vorherigen FPGA-Generation.

Auch das elektrische Verhalten dieser neuen Bausteingeneration profitiert von der Säulen-Organisation: Die Anschlüsse für Masse und Versorgungsspannung lassen sich gleichmäßig über den Die verteilen und in unmittelbarer Nachbarschaft zu den Verbrauchern anordnen (Bild 2, rechts). Dadurch verkürzen sich die Verbindungs-Längen, was besonders beim Übergang auf 90-nm-Fertigungsprozesse Vorteile bringt. Dank geringerer Spannungsabfälle über die Versorgungsleitungen sinkt die Verlustleistung und damit die Stromaufnahme des Bausteins. Bei Signalleitungen lassen sich höhere Schwellwerte für die Logikpegel definieren, was eine bessere Störungsunempfindlichkeit ermöglicht. Ein weiteres Element, das für eine niedrige Verlustleistung sorgt und trotzdem Taktfrequenzen bis 500 MHz zulässt, ist die Triple-Oxid-Technik, die Xilinx zusammen mit seiner Foundry UMC entwickelt hat. Drei unterschiedlich dicke Schichten bilden dabei die Gate-Isolation und senken so den beim Übergang von 0,13 µm auf 90 nm üblichen Anstieg der Leckströme, so dass statische und dynamische Leistungsaufnahme um bis zu 50 % gesenkt werden.

Die säulenförmige Anordnung der Funktionsblöcke eröffnet dem FPGA-Hersteller die Möglichkeit, neue Plattformen modular zusammenzustellen. Weil alle Funktionsblöcke für die Säulenform ausgelegt sind, lassen sie sich praktisch beliebig nebeneinander anordnen bzw. durch andere Blöcke ersetzen (Bild 3, rechts). So kann man neue oder zusätzliche Hard-IPs auf dem Baustein unterbringen, ohne dass dazu sofort ein größerer Die erforderlich wird. Die bessere Skalierbarkeit ermöglicht so häufig den Einsatz kleinerer Bausteine, was für den Anwender niedrigere Kosten bedeutet.

Domänen-optimierte Plattform-FPGAs

Dank der Möglichkeit, ein FPGA in dieser Säulenstruktur modular aufzubauen, lassen sich nun unterschiedlich zusammengesetzte Plattform-FPGAs für verschiedene Anwendungsklassen aus unterschiedlichen, vorgefertigten säulenförmigen Funktionsblöcken zusammenstellen. So kann man dem Anwender eine Familie von Plattform-FPGAs zur Verfügung stellen, die jeweils die passende Mischung generischer Funktionen für das Funktionsspektrum der jeweiligen Anwendung bereitstellen.

Die verschiedenen generischen Funktionen sind Logik (einschließlich aller Komponenten zur Implementation von Soft-IP), Speicher, digitale Signalverarbeitung (DSP), Prozessoren (z.B. PowerPC) und High-Speed-I/Os für alle gängigen seriellen und parallelen Schnittstellen. Mit unterschiedlich zusammengestellten Kombinationen dieser Funktionen lassen sich Plattform-FPGAs aufbauen, deren Funktionsspektrum auf unterschiedliche Anwendungsbereiche ausgerichtet ist.

Diese Anwendungsbereiche beschreiben nicht bestimmte, dedizierte Anwendungen, sondern eine Klasse von Anwendungen, denen ein bestimmtes Funktionsspektrum gemeinsam ist (Bild 5). Einer dieser Anwendungsbereiche konzentriert sich schwerpunktmäßig auf programmierbare Logik (LX-Baureihe), ein anderer überwiegend auf digitale Signalverarbeitung (SX-Baureihe) und ein dritter auf die Funktionsauswahl kompletter Systeme (FX-Baureihe). Die für diese Bereiche optimierten Plattform-FPGAs sind daher keine anwendungsspezifischen Bausteine, weil sie sich nach wie vor für unterschiedliche Anwendungen konfigurieren lassen und nicht an spezielle, vertikale Märkte gebunden sind. So kommen z.B. „High-Performance“-DSP-Funktionen in vielen unterschiedlichen Anwendungen, Produkten und Marktsegmenten zum Einsatz, z.B. in Wireless-, Broadcasting- oder Konsumelektronik-Systemen. Als erste Virtex-4-Baureihe wird die LX-Serie im Sommer 2004 bemustert. Die SX- und FX-Plattformen folgen zu einem späteren Zeitpunkt.

Dieses Konzept und die zugehörigen Entwicklungswerkzeuge haben aber auch noch einen weiteren Effekt: Der Designer kann jederzeit im Entwicklungsprozess die Systemarchitektur überprüfen, verändern oder verbessern und damit schnell auf veränderte Einsatz- oder Marktanforderungen reagieren. Diese Flexibilität gewinnt eine besondere Bedeutung, wenn Produkte für neu entstehende oder miteinander konkurrierende Standards entwickelt werden müssen.

| John Heighton studierte Electronics Engineering im schottischen Glasgow und erwarb den akademischen Grad eines BEng (Honours). Seine berufliche Karriere begann er 1986 als Hardware-Ingenieur bei IBM. Nach mehreren Jahren Tätigkeit in der Applikation, im Vertrieb und im Marketing wechselte er Anfang 2000 zu Xilinx. Derzeit ist er europäischer Marketing Manager für programmierbare Logik. E-Mail: john.heighton@xilinx.com |

- Dynamische Blindleistungskompensation

- Anforderungen an eine neue FPGA-Architektur