Cynergy3 bei AMS Technologies

Fortsetzung des Artikels von Teil 1

Dreifach-DES in Virtex-II Pro FPGAs

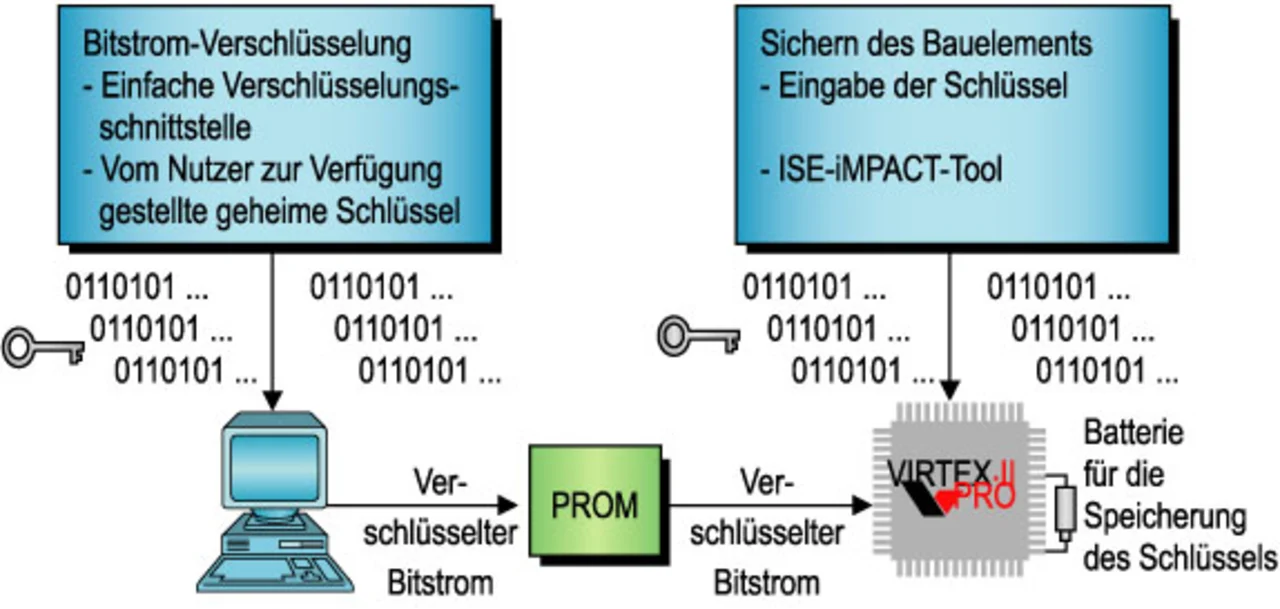

Die Virtex-II-Pro-Bausteine besitzen eine integrierte Entschlüsselungs-Engine, die sich zur Sicherung des Konfigurations-Bitstroms und damit auch des FPGA aktivieren lässt. Den Bitstrom verschlüsselt man in der Xilinx-Software mit Hilfe eines Schlüsselsatzes, und das Virtex-II-Pro-Bauteil entschlüsselt den einlaufenden Bitstrom intern anhand des gleichen Schlüsselsatzes (Bild 2).

Jobangebote+ passend zum Thema

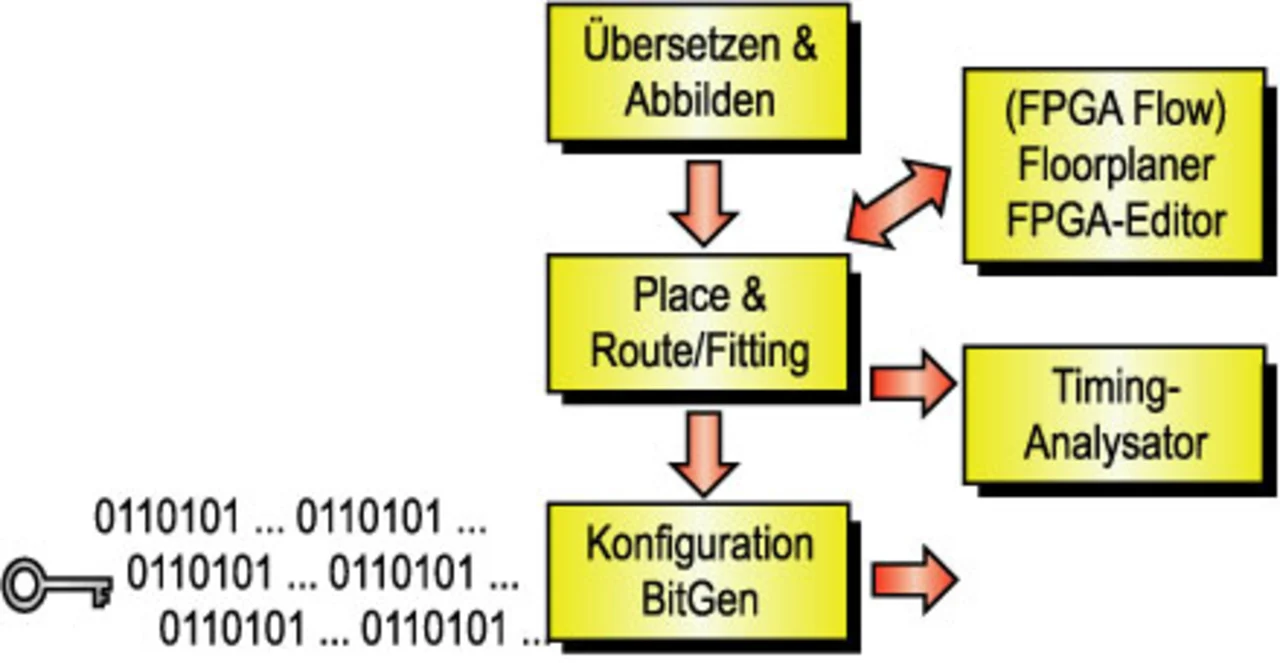

Sobald das Design in den ISE-Tools einen Platzierungs- und Routinglauf hinter sich hat, wird der verschlüsselte Konfigurations-Bitstrom anhand des ISE-BitGen-Programms mit benutzerdefinierten Schlüsseln (Bild 3) generiert. Die gleichen Schlüssel werden über den JTAG-Port mit Hilfe der ISE-iMPACT-Tools in das FPGA geladen.

Um die Schlüssel in den Baustein zu programmieren, muss dieser in den Key Access Modus versetzt werden, der das FPGA automatisch löscht – einschließlich aller alten Schlüssel und des aktuellen Bitstroms. Auch diese Maßnahme bietet Schutz gegenüber Angriffen.

Nachdem der Baustein mit den Schlüsseln programmiert ist, kann man ihn mit dem verschlüsselten Bitstrom konfigurieren. Sobald der verschlüsselte Bitstrom in das FPGA programmiert ist, lässt sich dieses weder durch unbeabsichtigte noch durch beabsichtigte Eingriffe oder Einbrüche rekonfigurieren, partiell konfigurieren oder auslesen. Jeder Versuch, ein Design zu stehlen, führt automatisch zur Löschung des gesamten FPGA (für Test- und Debugging-Zwecke lassen sich allerdings nicht-verschlüsselte Bitströme in ein FPGA programmieren, in das zuvor Schlüssel geladen wurden).

Die Schlüssel sind in einem speziellen Dreifach-DES-Block an einer Ecke des Bauteils angeordnet. Eine externe Batterie dient zur Speicherung der Schlüssel, wenn die Leiterplatte nicht unter Spannung steht. Jede normale Batterie mit einer Spannung zwischen 1 und 4 V lässt sich verwenden; das ermöglicht eine Lebensdauer von 15 Jahren.

Obwohl nicht-flüchtige PLD-Sicherheitsbits Lese-/Schreibzugriffe auf das Bauteil sperren, bietet die Dreifach-DES-Funktion von Virtex-II Pro mit Verschlüsselung echte Sicherheit. Und selbst wenn die Anordnung des Dreifach-DES-Blocks in den Virtex-II-Pro-FPGAs bekannt ist, lassen sich die Schlüssel ohne eine Löschung des Chip nicht abfangen.

Neun Metall-Schichten sind eine weitere Schutzbarriere gegen potenzielle Diebe. Weil bei der Speicherung der Sicherheitsbits keinerlei feste Verdrahtung beteiligt ist, sind sämtliche Versuche zum Scheitern verurteilt, die in den Virtex-II-Pro-FPGAs verborgenen Sicherheitsbits per Wärmebildtechnik zu finden.

Jeder Virtex-II-Pro-Baustein verfügt über sechs separate Schlüssel und erlaubt damit den Einsatz von zwei Dreifach-DES-Schlüsselsätzen. Man kann die Bausteine von vornherein mit beiden Schlüsselsätzen programmieren. Dies bietet sogar einen Schutz gegen Angriffe der Klasse III. Sollte zum Beispiel der erste Schlüsselsatz geknackt worden sein, so kann man die Bausteine im Feld ferngesteuert mit einem Bitstrom reprogrammieren, der den zweiten Schlüsselsatz verwendet. Mit ihrer hohen Sicherheit eignen sich die Bausteine besonders für den Einsatz im Automotive-Bereich, zum Beispiel in automatischen Distanzkontrollen oder dem Motor-Management.

Was ist Dreifach-DES? Dreifach-DES ist der dominante Verschlüsselungsstandard, der im Bankwesen täglich für Millionen von Transaktionen verwendet wird, bei denen es um Billionen von Dol-lar geht. In Xilinx-FPGAs arbeitet die gleiche Technologie zum Schutz ihrer Designs. Es gibt zwar Berichte, dass der ältere DES-Standard schon geknackt worden ist, doch noch niemand konnte Dreifach-DES erfolgreich angreifen. Dreifach-DES ist eine offizielle NIST- (National Institute of Standards and Technology) und ANSI-X9.52-Norm (American National Standards Institute). AES (Advanced Encryption Standard) ist die Verschlüsselung der nächsten Generation, die eingesetzt werden wird, falls Dreifach-DES geknackt werden sollte. Im Rahmen ihrer laufenden Bemühungen, Hacker zu behindern, arbeiten Verschlüsselungsexperten bereits an der Entwicklung zukünftiger AES-Versionen. Obwohl Billionen Dollar und Millionen von finanziellen Transaktionen auf dem Spiel stehen und vielleicht einige Tausend Hacker an den unterschiedlichsten Angriffen arbeiten, hat sich Dreifach-DES bis heute gut geschlagen. Aus diesem Grund hat sich Xilinx für Dreifach-DES und damit für die beste Verschlüsselungsfunktion zum Einsatz in seiner Premium-Produktlinie Virtex-II Pro entschieden. Dreifach-DES ist ein symmetrischer Verschlüsselungsalgorithmus. Für Ver- und Entschlüsselung benutzt man also die gleichen Schlüssel. Die Sicherheit der Daten hängt vom Schlüssel ab – im Gegensatz zu Systemen mit öffentlichem Schlüssel wie RSA oder PGP verwendet Dreifach-DES drei Schlüssel, und der Verschlüsselungsalgorithmus wird mit jedem Schlüssel wiederholt, was ein Plus an Sicherheit bringt. Jeder Schlüssel ist 56 bit lang und verschlüsselt Datenblöcke mit 64 bit Länge in einem Schritt. Weitere Informationen zum Dreifach-DES Standards gibt es unter www.itl.nist.gov. |

- Cynergy3 bei AMS Technologies

- Dreifach-DES in Virtex-II Pro FPGAs