Bis 260 °C löten mit anschließender erhöhter Temperaturzyklenfestigkeit

Automotive-MOSFET-Gehäuse für bleifreie Reflow-Lötprozesse

Fortsetzung des Artikels von Teil 1

Temperaturzyklentests mit dem Robust-Package

Das Robust-Package ist gemäß AEC Q101 qualifiziert. Für den durch Temperaturzyklen bedingten thermomechanischen Stress auf das Gehäuse gibt es innerhalb der AEC Q101 zwei Tests:

Temperature-Cycling (TC), bestehend aus Zyklen von –55 °C bis +150 °C mit externer Wärmeeinbringung, und- Intermittent-Operating-Lifetime (IOL), bestehend aus Zyklen von typisch 35 °C bis 135 °C mit MOSFET-interner Wärmeerzeugung.

Jobangebote+ passend zum Thema

Beide Tests werden nach der Lagerung und 3-facher Reflow-Lötung-Simulation bis 260 °C (MSL 1 260 °C Preconditioning) durchgeführt. Um die Auswirkungen dieser Gehäuseänderungen in der Praxis zu beurteilen, wurden Vergleichstests zwischen dem Infineon-Robust-Package und marktgängigen Bauteilen durchgeführt. Als Gehäuse wurde ein D2PAK (P-TO263-3) verwendet. Beim Preconditioning der Mitbewerberprodukte wurde die 3-fache Lötsimulation nur bis 245 °C gefahren, weil diese Gehäuse nur bis 245 °C freigegeben sind. Dies bedeutet für diese Bauteile auch einen geringeren Lötstress. Solche Testergebnisse werden immer sowohl elektrisch als auch visuell ausgewertet. Dabei wurde auf beide erwähnten Hauptfehlermechanismen im Gehäuse fokussiert: Lotermüdung und Delamination der Pressmasse.

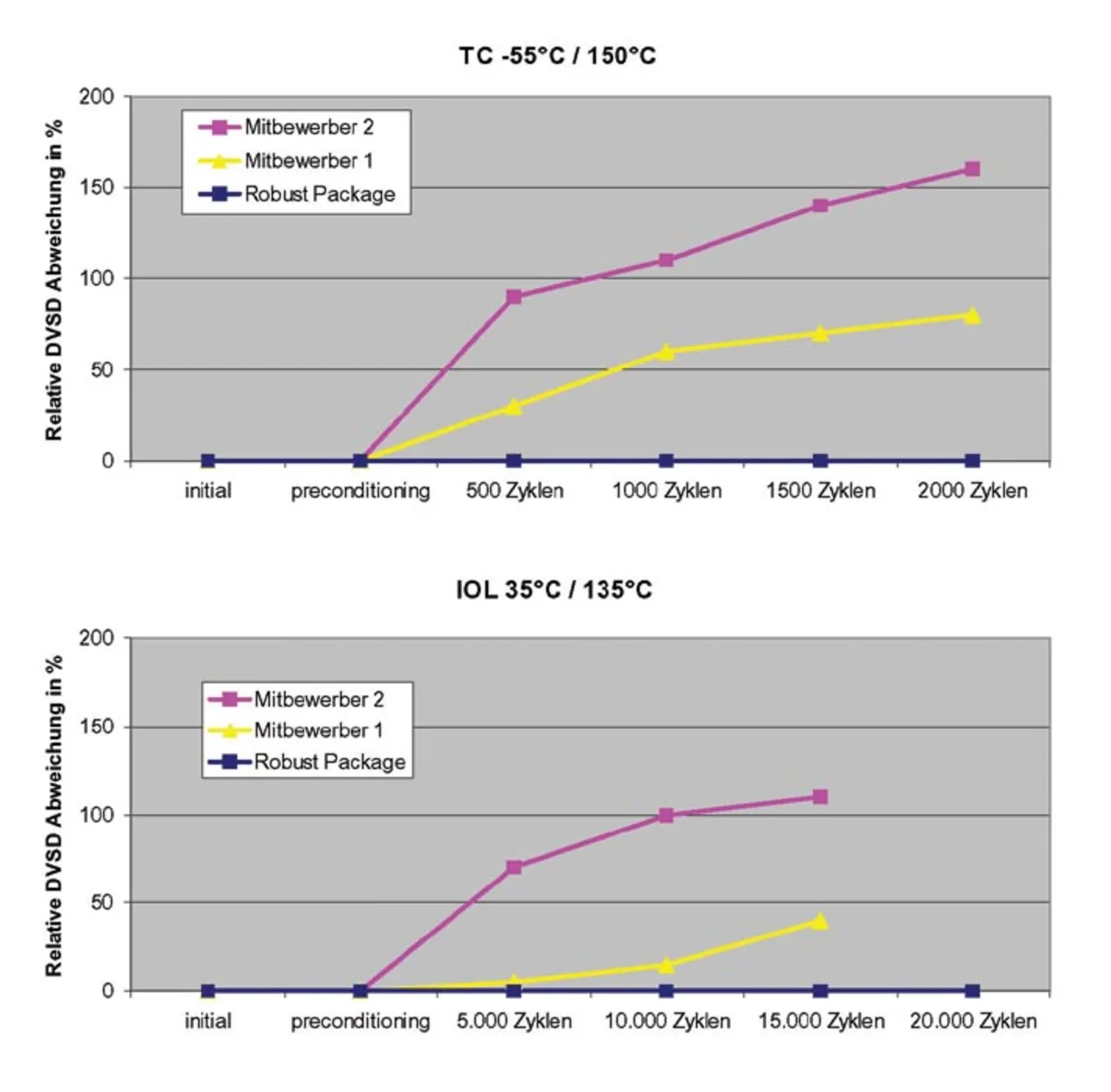

Betrachtet werden die statischen elektrischen Parameter (z.B. Rds(on), Ugs(th), Ubrd(ss), ...) und auf eventuelle Ausfälle oder Abweichungen der Parameter geprüft. Besonders wird die Chip-Lotqualität über einen so genannten Delta-Usd-Test (DVSD) bewertet. Die thermische Leitfähigkeit des Chip-Lots wird überprüft, indem ein Leistungspuls im MOSFET eingeprägt und die Änderung eines temperatursensitiven Parameters vor und nach dem Puls beobachtet wird. Dabei wird die Vorwärtsspannung der Body-Diode benutzt. Wenn das Lot in Ordnung ist, befindet sich die Temperaturänderung im normalen Bereich und die Differenz der Vorwärtsspannung vor und nach dem Puls hat einen bestimmten DVSD-Wert. Verschlechtert sich das Lot, erhöht sich dieser DVSD-Wert während des Tests, weil die Wärme nicht oder schlechter abgeführt werden kann. Bild 4 zeigt die relative Änderung dieses DVSD-Wertes. Anders als bei marktgängigen Gehäusen, gibt es beim Robust-Pack°age keine Abweichung während der verschiedenen Zyklen. Dies bedeutet, dass der thermische Widerstand Junction-to-Case beim Robust-Package stabil bleibt.

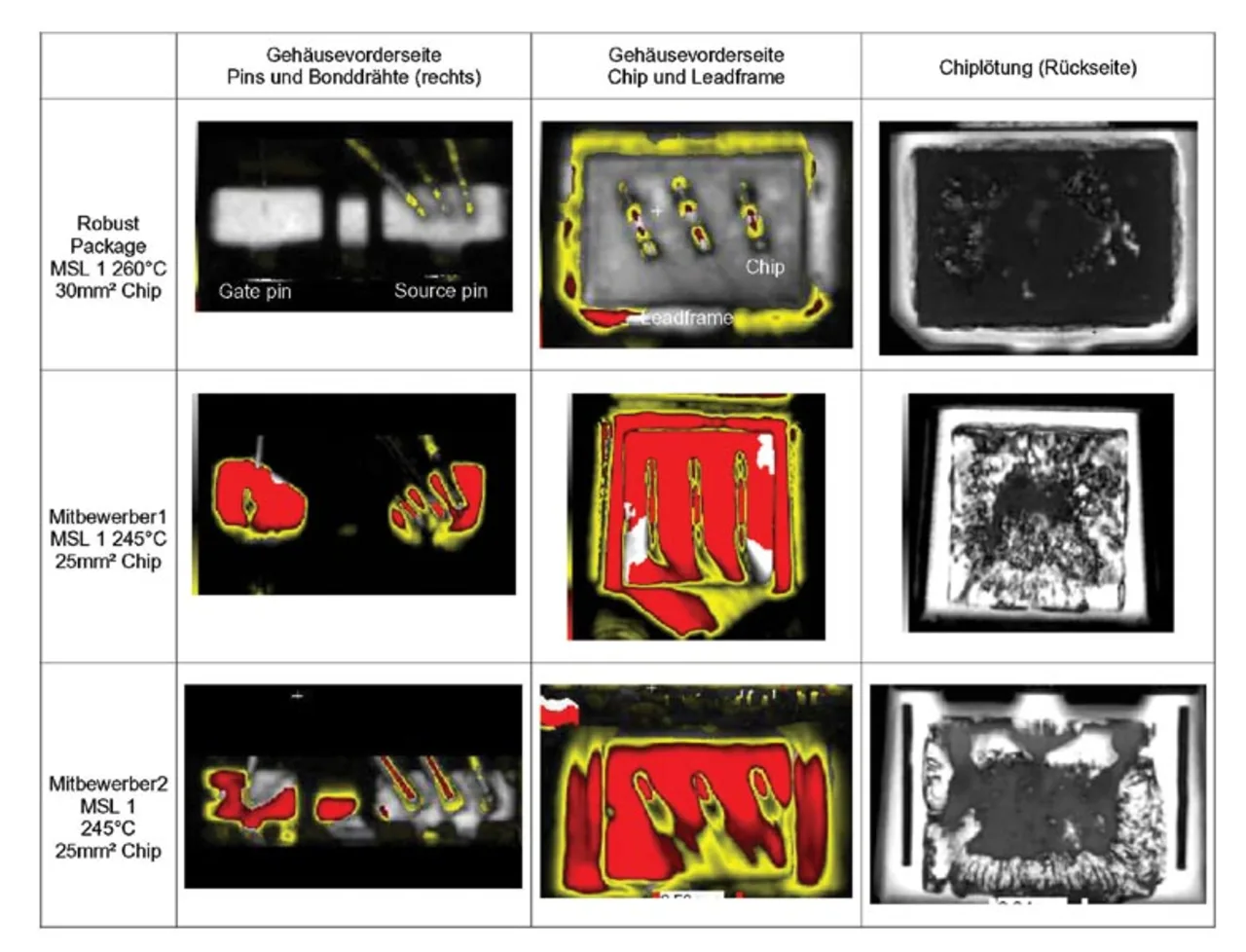

Bei der visuellen Inspektion wird das Vorhandensein möglicher Fehler wie z.B. Delamination der Pressmasse überprüft. Man sieht in Bild 5 ultraschallmikroskopische Bilder von der Gehäusevorderseite (Leadframe und Pins) und dem Chip-Lot nach 2000 Temperaturzyklen (TC). Die Ergebnisse des IOL-Tests ähneln denen des TC-Tests. Auf der linken Seite werden die Pins untersucht. Beim Robust-Package sieht man keine Farbfläche. Dies bedeutet perfekte Haftung der Pressmasse mit den Pins und den Source- und Gatebond-Drähten. Bei den Mitbewerbern ist besonders der Gatepin delaminiert (rote Farbfläche). Dies kann unter Umständen zur Gate-Drahtabhebung und zum Ausfall des Bauteils führen. In der mittleren Spalte sieht man beim Robust-Package eine leichte Delamination der Pressmasse auf dem Leadframe und keine Delamination auf dem Chip. Dies bedeutet geringeren thermomechanischen Stress auf dem Chip und dem Lot. Die Lotqualität bleibt erhalten und somit auch der Rth(JC). Bei den Standardgehäusen gibt es eine totale Delamination auf dem Leadframe und auf dem Chip. In der dritten Spalte sind Bilder der Chip-Lötung dargestellt. Nur in den dunklen Bereichen ist die Lötung noch intakt. Die Graubereiche visualisieren eine starke Lotermüdung.

Diese Bilder sind konsistent mit den DVSD-Werten (siehe Bild 4). Mit dem Robust-Package gibt es keine Delamination der Pressmasse und somit keine Degradation des Chip-Lots wie bei den Standardgehäusen. Das heißt, keine Verschlechterung des thermischen Widerstandes Rth(JC) während der Temperaturzyklen und letztendlich eine höhere Zuverlässigkeit in der Applikation. Diese erhöhte Temperaturzyklenfestigkeit ist von großem Vorteil für Applikationen, die den MOSFET thermisch besonders beanspruchen, wie beispielsweise eine lineare Lüftersteuerung oder eine elektronische Lenkunterstützung (EPS).

Robust-Package als Basisgehäuse für die Zukunft

Die „robuste“ Gehäusetechnologie ist an dem D2PAK-(P-TO263-) Gehäuse entwickelt worden. Sie kann aber auch für beliebige weitere Gehäuse, wie zum Beispiel DPAK (P-TO252), SOT223 oder P-DSO 150/300/430mil, angewandt werden.

Das Robust-Package ist kompatibel mit den bleifreien Platinenverarbeitungsprozessen und hat eine grüne Pressmasse. Die Anschlussverzinnung beinhaltet derzeit noch Blei. Der letzte Schritt zu einem „grünen“ Gehäuse (Green and Robust-Package) ist eine bleifreie Anschlussverzinnung aus 100 Prozent Zinn. Diese Änderung war einfacher durchzuführen, da die Verzinnung ein bekannter Prozess ist, ohne Einfluss auf die Zuverlässigkeit. Die Herausforderung beim Robust-Package lag in dem neuen Hochtemperatur-Chip-Lot, die „grüne“, umweltfreundliche Pressmasse und im Besonderen in der Entwicklung und Prozessstabilisierung des Pressmassenhaftvermittlers. Ein solches „Green and Robust-Package“ ist ebenfalls schon verfügbar.

Die guten thermomechanischen Eigenschaften sowie die Kompatibilität mit den bleifreien Lötprozessen machen aus dem „Green and Robust-Package“ eine exzellente Basis für einen zukünftigen MOSFET mit einer maximalen Sperrschichttemperatur von 200 °C. Die Herausforderung liegt bei der Pressmasse, die im heutigen Zustand an ihre Temperaturgrenze stößt. Für weitere Informationen zu Hochtemperaturgehäusen siehe [1]. Der Weg zu einem Hochtemperatur-MOSFET ist aber noch lang, denn es gibt noch viele offene Fragen. Die Definition selbst eines 200-°C-MOSFETs ist nicht klar. Wie lange dürfen die 200 °C anliegen? Wie wird der MOSFET dann gelötet? Wenn die Junction-Temperatur 200 °C beträgt, ist die Pin-Temperatur auch schon bei Temperaturen weit über den üblichen 125 °C max. für Standardplatinen. Wie wird so ein Bauteil qualifiziert? Wie wird dann eine Testbeschleunigung erzielt, ohne neue und applikationsfremde Fehlermechanismen zu erzeugen? Die aktuelle AEC Q101 ist nicht ausreichend, um den Anforderungen eines 200-°C-Produktes gerecht zu werden. Dies betrifft insbesondere die Definition der passiven und aktiven Temperaturzyklenfestigkeit.

In diesem Artikel ist dargelegt, dass durch die Änderung des Chip-Lots, der Pressmasse und den Zusatz eines Pressmassenhaftvermittlers, die Komponenten im neuen Robust-Package von Infineon für bleifreie Lötprozesse bis 260 °C Peak-Temperatur gemäß JEDEC-Norm J-STD-020C geeignet sind. Die Vermeidung der Delamination der Pressmassen sowie der Lotermüdung gibt den Komponenten eine hervorragende Temperaturzyklenfestigkeit – und das auch nach einer dreifachen Lötsimulation bis 260 °C (Moisture Sensitivity Level 1 bis 260 °C). Dies erhöht die Zuverlässigkeit der Komponenten in der Applikation. Wenn die bleihaltige Anschlussverzinnung des Robust-Packages durch ein 100-prozentiges Zinn-Plating ersetzt wird, erhält man das so genannte „Green and Robust-Package“, das die neuen „grünen“ Richtlinien erfüllt.

| Dipl.-Ing. Jean-Philippe Boeschlin kam nach seinem Elektrotechnikstudium an der ENSEA in Paris zu Tyco Electronics (ehemals Siemens AG Bereich Elektromechanische Kompo-nente) als Applikationsingenieur für Automobil-Relais. Er arbeitet heute als Applikationsingenieur für Leistungsschalter im Bereich Automobil bei der Infineon Technologies AG. E-Mail: jean-philippe.boeschlin@infineon.com |

- Automotive-MOSFET-Gehäuse für bleifreie Reflow-Lötprozesse

- Temperaturzyklentests mit dem Robust-Package