Single-Chip-CMOS-Transceiver ist weltweit einsetzbar

In allen UMTS-Bändern zu Hause

Fortsetzung des Artikels von Teil 7

In allen UMTS-Bändern zu Hause

Der Sendezug beinhaltet ein aktives Analog-Basisbandfilter dritter Ordnung mit Butterworth-Charakteristik, drei Direkt-Aufwärtswandler, VGA-Stufen mit einem steuerbaren Verstärkungsbereich von über 85 dB für jeden Pfad und Hochleistungs-Ausgangstreiberstufen. Adaptives Biasing in den VGA-Stufen sorgt für eine minimale Stromaufnahme über den gesamten Ausgangsleistungsbereich. Jeder Direct-Conversion-Sendepfad besteht aus einem vollständig differenziellen, programmierbaren Eingangspuffer, um die verschiedenen Basisband-Eingangssignale verarbeiten zu können. Das integrierte Basisbandfilter eliminiert unerwünschte Störsignale wie beispielsweise das Weitabrauschen des Basisband-D/A-Wandlers, ohne das gewünschte Signal zu verzerren, so dass sich eine optimale und dem Standard entsprechende Spektralverteilung des Ausgangssignals ergibt.

Sowohl der Empfangs- als auch der Sendepfad nutzen einen voll integrierten Fractional-N-Synthesizer mit On-chip-Schleifenfiltern und -Referenzwiderständen. Damit kann die Anzahl der erforderlichen externen Komponenten deutlich reduziert werden. Um alle Betriebsbänder abzudecken und zusätzliche Frequenzspielräume zum Ausgleich von Prozessvariationen zu schaffen, kommen differenzielle VCOs (spannungsgesteuerte Oszillatoren) mit einem großen Nutzfrequenzbereich zum Einsatz. Für den Betrieb in den UMTS-Bändern V und VI wird ein zusätzlicher Teiler (:2) an den VCO-HF-Ausgängen aktiviert. Ein interner Abgleichalgorithmus, der jedes Mal getriggert wird, wenn die PLL startet oder eine neue Frequenz anliegt, wählt das passende VCO-Band aus. Gleichzeitig sorgen weitere Kalibrieralgorithmen dafür, dass alle Abweichungen in der PLL, wie beispielsweise die Eckfrequenzschwankungen des Schleifenfilters, minimiert werden.

Jobangebote+ passend zum Thema

Strom und Platz sparen

Ein stromsparendes Design ist ein wichtiges Kriterium für Mobiltelefon-Applikationen, was unter anderem in dem neuen Baustein durch einen speziellen HF-CMOS-Prozess realisiert wird. Ansonsten arbeitet der Transceiver mit einer Spannungsversorgung zwischen 2,7 und 3 V bei einer Umgebungstemperatur zwischen –30 und +85 oC. Um optimale Kompatibilität zu gewährleisten, lässt sich der Chip für verschiedene Quarzoszillator-Referenzfrequenzen sowie unterschiedliche Basisband-Schnittstellenparameter konfigurieren (zum Beispiel I/Q-Gleichtaktspannung). Diverse Power-Down-Betriebsarten sichern eine minimale Stromaufnahme bei allen Betriebsbedingungen. Wenn weder die Empfangs- noch die Sendefunktion genutzt wird, kann z.B. ein spezieller „Sleep Mode“ aktiviert werden. Damit lässt sich die typische Stromaufnahme auf nur noch wenige ?A reduzieren, wenn das Handy keine Funkanwendung benötigt. Alle Register-Einstellungen werden in einem speziellen RAM abgelegt, damit der Chip bei der nächsten Aktivierung sofort wieder alle Einstellungen herstellen kann.

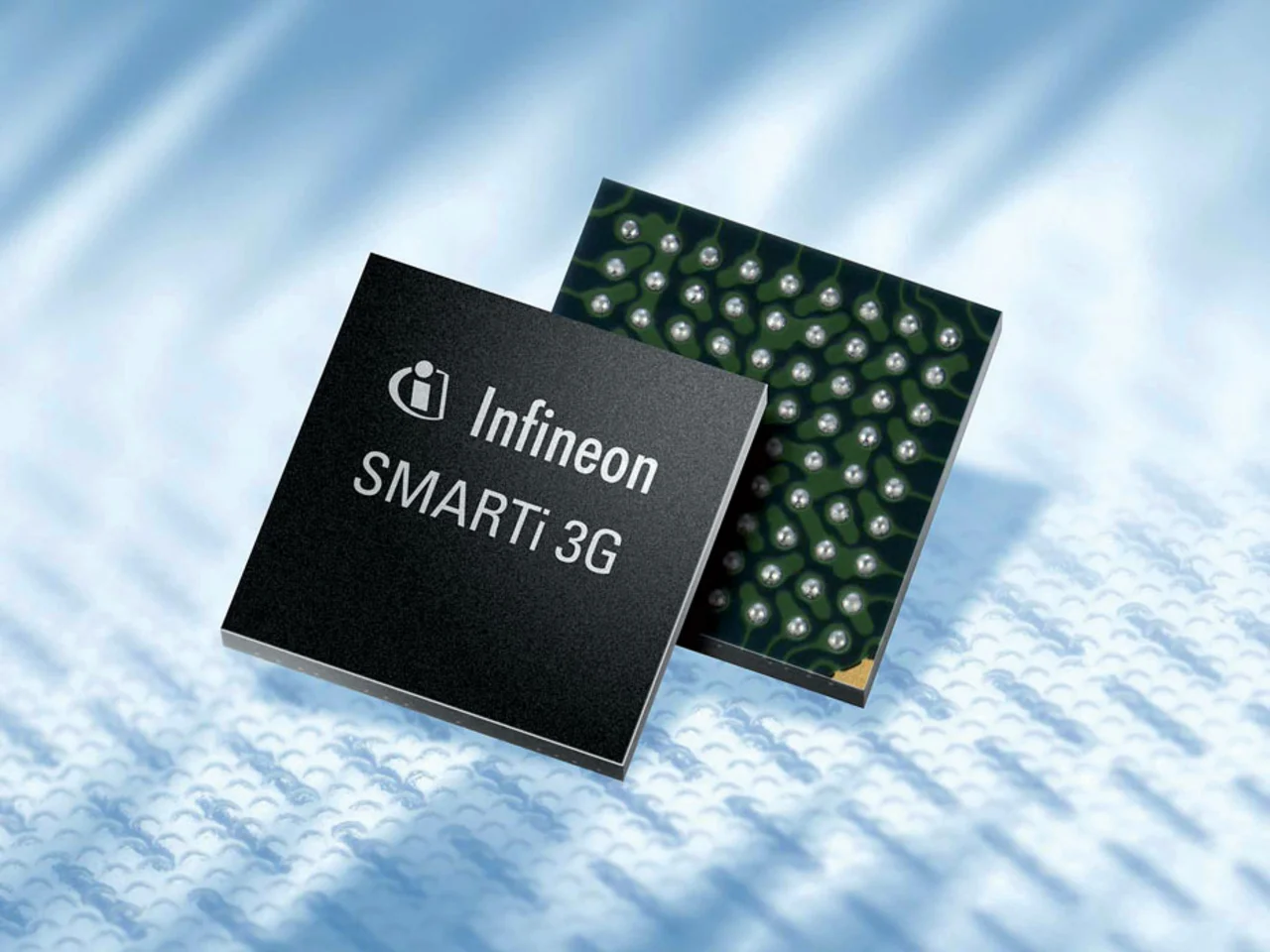

Untergebracht ist der Baustein in einem WFSGA-Gehäuse (Very Very Flat Semi Ball Grid Array) bei einer Gesamtfläche von nur 5 mm x 5 mm und einer Höhe von 0,8 mm (Bild 2).

- In allen UMTS-Bändern zu Hause

- Die Basis: Das initiale Board Support Package

- Produktentwicklung führt zu individuellem BSP

- In allen UMTS-Bändern zu Hause

- Mit individuellem Board Support Package Mehrwert erzielen

- Mehr Funktionen, bessere Qualität in kürzerer Zeit

- In allen UMTS-Bändern zu Hause

- In allen UMTS-Bändern zu Hause