Die EC/ECP-FPGA-Familie von Lattice Semiconductor ist für den kostensensitiven Massenmarkt konzipiert

Die Schotten-FPGAs

Fortsetzung des Artikels von Teil 2

Interne Speicherstruktur

Wie oben erwähnt, ist die interne Logik in der Lage, Speicherfunktionen bereitzustellen. Dies genügt aber in den meisten Fällen nicht, um die gesamten Speicherfunktionen eines Designs zu implementieren. Deshalb stellen die EC/ECP-FPGAs auch dedizierte Speicherblöcke zur Verfügung.

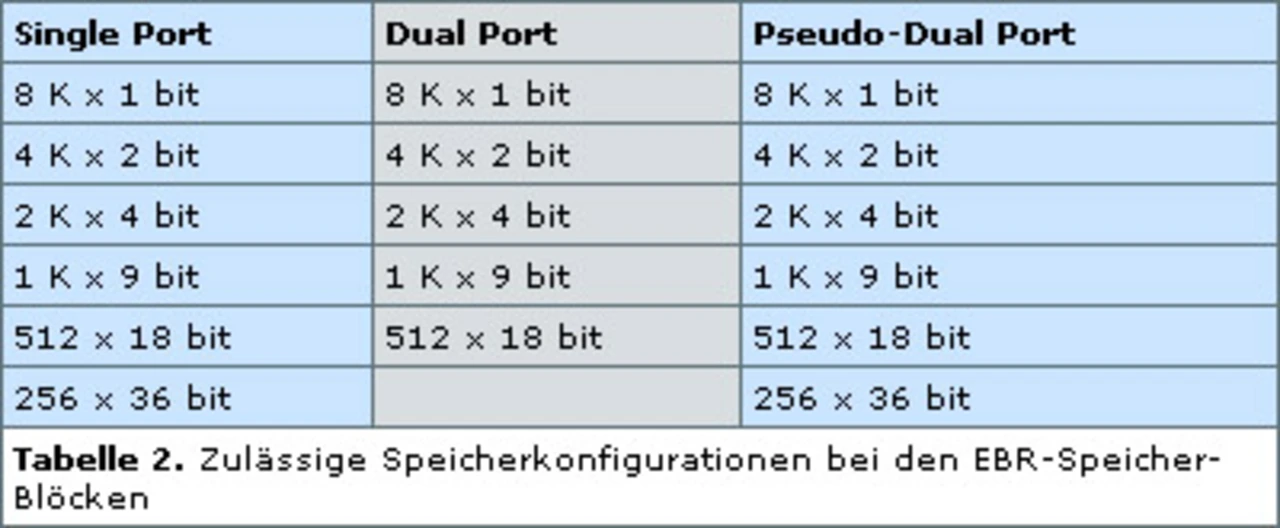

Diese Speicherblöcke sind 9 Kbit groß und zu jeweils 9 bit organisiert. In Breite und Tiefe lassen sie sich vom Anwender über den Module-Generator der Design-Software „ispLEVER“ konfigurieren. Tabelle 2 zeigt die Konfigurationsmöglichkeiten eines EBR (Embedded Memory RAM).

Diese Speicherblöcke können sowohl als „Single Port“ und „Pseudo Dual Port“ als auch als „True Dual Port“ konfiguriert werden. Der True-Dual-Port-Speicher hat zwei voneinander unabhängige Schreib-/Lese-Ports, die sich mit unterschiedlichen Taktfrequenzen betreiben lassen.

Diese Speicherblöcke unterstützen drei verschiedene Formen des Schreibens:

- Normal: Am Ausgang werden die Daten erst bei einem Lesezugriff sichtbar.

- Write-Through: die zu schreibenden Daten sind auch am Ausgang desselben Ports beim Schreibvorgang sichtbar.

- Read-Before-Write: Wird ein neuer Wert in eine Speicheradresse geschrieben, erscheint der alte Speicherinhalt dieser Adresse am Ausgang desselben Ports.

Jobangebote+ passend zum Thema

Werden FIFO-Module benötigt, lässt sich die Zusatzlogik mit den bereitgestellten PFUs implementieren. Diese Funktion stellt der Module-Generator von ispLEVER bereit.

Takt-Synthese

Oft besteht die Notwendigkeit, vorgegebene Taktverhältnisse zu beeinflussen. Dazu gehört es, Taktfrequenzen zu vervielfältigen oder zu teilen bzw. den Takt in der Phase gegenüber den Daten zu verschieben, um gegebene Laufzeitverhältnisse zwischen Daten und Takt auf die Systemanforderungen anzupassen.

Für diese Aufgaben hat Lattice bis zu vier analoge PLLs in die FPGAs integriert. Diese PLLs decken einen Frequenzbereich von 25 bis 420 MHz ab und sind tolerant gegenüber Eingangs-Jitter der Frequenz ausgelegt. Dabei werden Taktsignale mit sehr geringem Jitter erzeugt (±125 ps).

Die PLL kann verschiedene Phasen des Taktes generieren, die in Schritten zu 45° einstellbar sind. Möchte man eine Verschiebung des Taktsignals im ps-Bereich vornehmen, stehen hierfür verschiedene Laufzeit-Elemente mit 250-ps-Schritten zur Verfügung. Damit sind Verschiebungen bis ±2 ns zusätzlich möglich. Diese Einstellung kann auch dynamisch erfolgen, d.h., über ei-nen Bus lassen sich die Verzögerungselemente im laufenden Betrieb verändern. Dadurch ist die Taktflanke unterschiedlichen Gegebenheiten im System anpassbar. Die Rückkopplung der PLL kann über interne Netze laufen, um interne Laufzeiten zu eliminieren, oder durch eine externe Rückkopplung, um die kompletten Laufzeiten durch den Baustein zu kompensieren, wie es auch bei „Zero Delay Buffers“ der Fall ist. Um diese Taktsysteme vernünftig im Baustein zu verteilen, bietet das FPGA verschiedene Taktnetzwerke an.

Taktnetze

Ein weiteres wichtiges Thema ist die Verteilung der Taktsignale im FPGA. Dabei kommt es darauf an, dass diese Signale schnell und ohne großen Laufzeitunter-schied (Skew) verteilt werden. Dafür bieten die EC/ECP-FPGAs vier dedizierte Taktnetze (primary) pro Quadrant an. Dies bedeutet, dass man insgesamt 16 eigene Taktnetze in einem Baustein zur Verfügung hat. Benötigt man den Takt in verschiedenen Quadranten, können diese in der zentralen Verteileinheit zusammengeschaltet werden. Diese dedizierten Taktnetze zeigen einen Versatz von weniger als ±250 ps in einem EC20 mit 20 000 LUTs und können mit bis zu 420 MHz betrieben werden. Gespeist werden diese Taktnetze über die I/O-Pins, die PLL-Ausgänge oder über interne Routing-Ressourcen. Möchte man intern Taktnetze im laufenden System umschalten, stehen hierfür die DCS-Blöcke (Dynamic Clock Select) zur Verfügung. Mit diesen Blöcken lassen sich interne Taktsysteme Spike-frei umschalten.

Benötigt der Entwickler weitere Taktnetze, stehen die so genannten „secondary“ Taktnetze zur Verfügung. Auch hier sind es pro Quadrant vier Netze, die in der zentralen Verteilstelle zusammengeschaltet werden können. Eines dieser vier secondary Netze ist für das globale Set/Reset-Signal reserviert. Die anderen stehen für Taktnetze oder Signale mit hoher Last zur Verfügung.

I/O-Standards

Um die Daten in und aus dem FPGA zu bekommen, muss es in der Lage sein, die verschiedensten I/O-Standards zu beherrschen. Die EC/ECP-FPGAs bieten die I/O-Standards von LVTTL, LVCMOS (1.2 bis 3.3), PCI-33, SSTL und HSTL (massebezogen und differenziell) sowie True-LVDS-I/Os. Die verschiedenen I/O-Standards tragen einen großen Teil zur Siliziumfläche bei. Deshalb ist es erforderlich, intelligente Maßnahmen zu ergreifen, um die Chipfläche so klein wie möglich zu halten. Die EC/ECP-FPGAs haben die True-LVDS-Ausgänge jeweils auf der rechten und linken Seite des Bausteins. Jedes I/O-Paar kann als LVDS-Eingang konfiguriert werden. Die „PCI-Klemm-Dioden“, die für echte PCI-Schnittstellen notwendig sind, können an den I/Os der oberen und unteren Seite des FPGA eingeschaltet werden. Mit Hilfe dieser PCI-Klemm-Dioden können auch 5-V-Signale erfasst werden. Dazu muss diese Diode einschaltet sein und ein externer serieller Widerstand im Bereich von 20 bis 120 Ohm hinzugefügt werden. Der genaue Wert lässt sich über die Diodenkennlinie im Datenblatt ermitteln.

Einschaltverhalten

Die EC/ECP-FPGAs sind „Hot Socketing“ fähig, d.h., die benötigten Spannungen können in beliebiger Reihenfolge ein- und ausgeschaltet werden, ohne dass der Baustein dabei beschädigt wird. Auch sind die I/Os bis zur vollständigen Konfiguration der Bausteine hochohmig und können somit andere Bausteine nicht beschädigen, indem zwei Signale gegeneinander treiben.

Große Probleme bereiten FPGAs, die beim Einschalten wesentlich mehr Strom benötigen als im Betrieb, da die Stromversorgung auf den höchsten Strombedarf ausgelegt werden muss. Die EC/ECP-FPGAs weisen einen typischen Einschaltstrom von 150 mA auf. Die FPGAs der Mitbewerber liegen im Ampere-Bereich. Diese Eigenschaft kann die Kosten der Stromversorgungsmodule und somit des Gesamtsystems erheblich reduzieren.

- Die Schotten-FPGAs

- DDR-Speicherschnittstelle

- Interne Speicherstruktur