Die EC/ECP-FPGA-Familie von Lattice Semiconductor ist für den kostensensitiven Massenmarkt konzipiert

Die Schotten-FPGAs

Fortsetzung des Artikels von Teil 1

DDR-Speicherschnittstelle

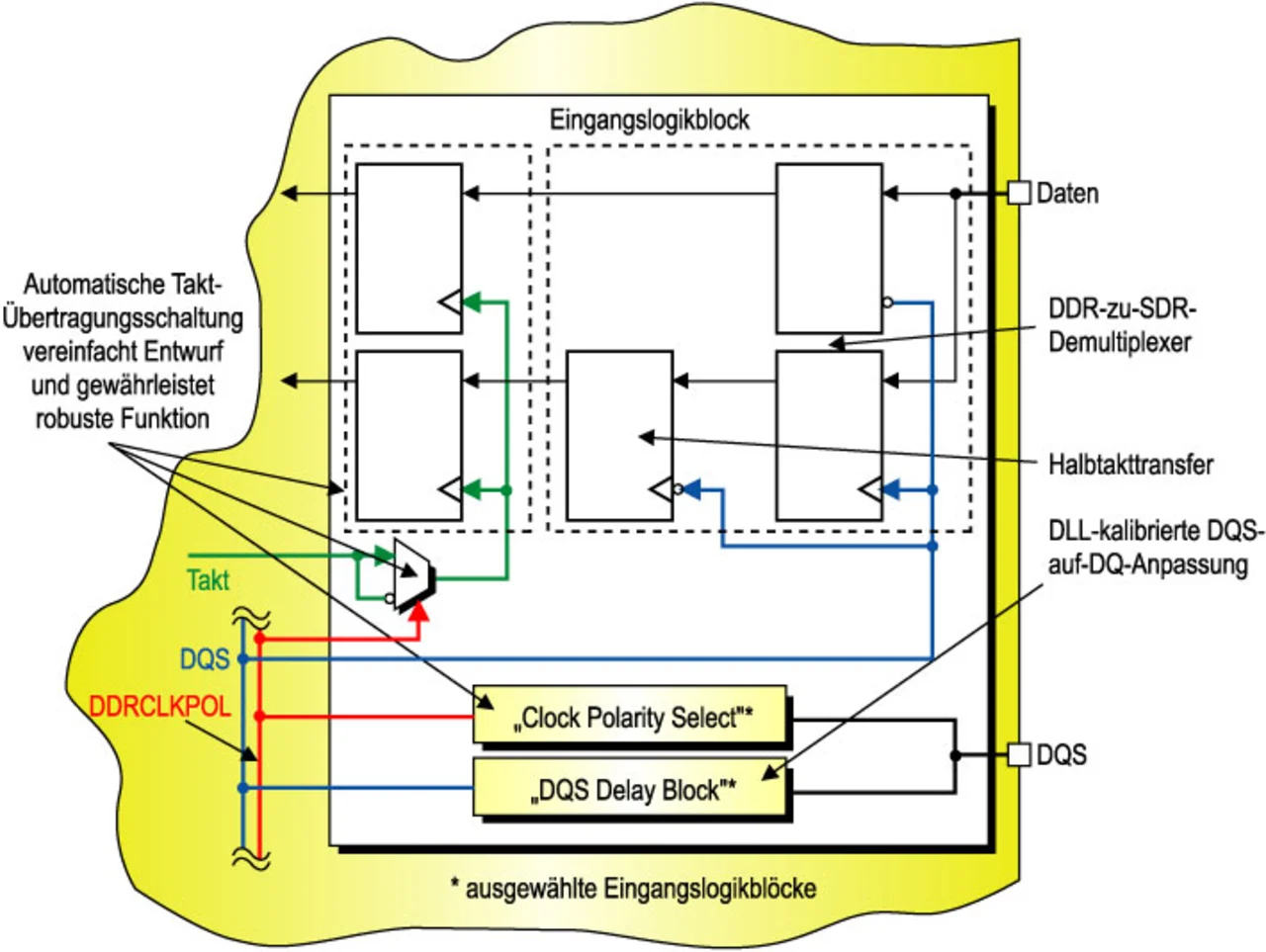

Oft ist es erforderlich, Daten in externen Speichermodulen zwischenzuspeichern, um sie nach und nach weiterverarbeiten zu können. Zu diesem Zweck muss ein externer Speicher angesteuert werden können. Welche Speicher benutzt werden, hängt meist von der Arbeitsweise ab. Werden die Daten öfter gelesen oder öfter geschrieben, oder hält sich das Verhältnis von Lesen und Schreiben die Waage? Auch die benötigte Bandbreite ist ein wesentlicher Faktor in der Auswahl der Speichermodule. Zur Zeit sind DDR-DRAMs eine gute Alternative, wenn man hohen Datendurchsatz zu bezahlbaren Kosten wünscht. Speziell bei hohem Datendurchsatz haben herkömmliche Low-Cost-FPGAs ihre Probleme. Oft stehen keine direkten DDR-I/Os zur Verfügung, oder es wird für die DDR-Schnittstelle interne FPGA-Logik benötigt, wodurch das Erreichen von hohen Datenraten beeinträchtigt wird. Lattice geht hier einen anderen Weg: In den EC/ECP-Bausteinen sind dedizierte DDR-I/Os (Bild 2) implementiert, damit die Daten direkt in die I/O-Zelle übernommen werden können.

Jobangebote+ passend zum Thema

Ein spezielles Problem, welches bei DDR-Speicherzugriffen zu lösen ist, wäre die Phasenverschiebung um 90° zwischen Daten und Takt. In einigen Low-Cost-Lösungen werden hierfür Verzögerungselemente benutzt, die aber das Problem haben, über den Temperatur- und Spannungsbereich stark zu schwanken. Die Entwickler haben hierfür in jedem EC/ECP-FPGA zwei DLLs spendiert, die genau die 90° Phasenverschiebung zwischen Daten und Takt erzeugen. Diese Verschiebung bleibt über Temperatur und Spannung konstant.

Da das Eintakten der Daten in das FPGA mit einem Strobe-Signal (DQS) erfolgt, haben wir es hier mit zwei unterschiedlichen Taktsystemen zu tun. Der Strobe übernimmt die Daten, der interne Systemtakt, der in der Frequenz, aber nicht in der Phase gleich ist, verarbeitet die Daten. Damit bei dem Übergang zwischen diesen beiden Taktsystemen keine Probleme entstehen, wird über einen „Clock Polarity Select“-Block entschieden, mit welcher Flanke die Daten dem internen Taktsystem übergeben werden. Somit werden Set-up- und Hold-Probleme eliminiert. Diese Auswahl wird an dem Zeitpunkt der „Preamble“ entschieden. Die Preamble ist der Übergang des DQS-Signals vom Tri-State- in den Low-Zustand. Dies bedeutet, dass für das Lese-Interface keine FPGA-Logik benötigt wird und es somit unabhängig von der restlichen Schaltung ist. Zum Schreiben kann man mit einer PLL die Phasenverschiebung realisieren, um speicherseitig die Phasenverschiebung von 90° zu gewährleisten.

Mit dieser Methode ist es möglich, einen DDR-Speicher mit bis zu 400 Mbit/s zu betreiben. Ein IP-Core für den DDR-Speicher-Controller steht zur Verfügung.

Digitale Signalverarbeitung mit sysDSP-Blöcken in ECP-Bausteinen

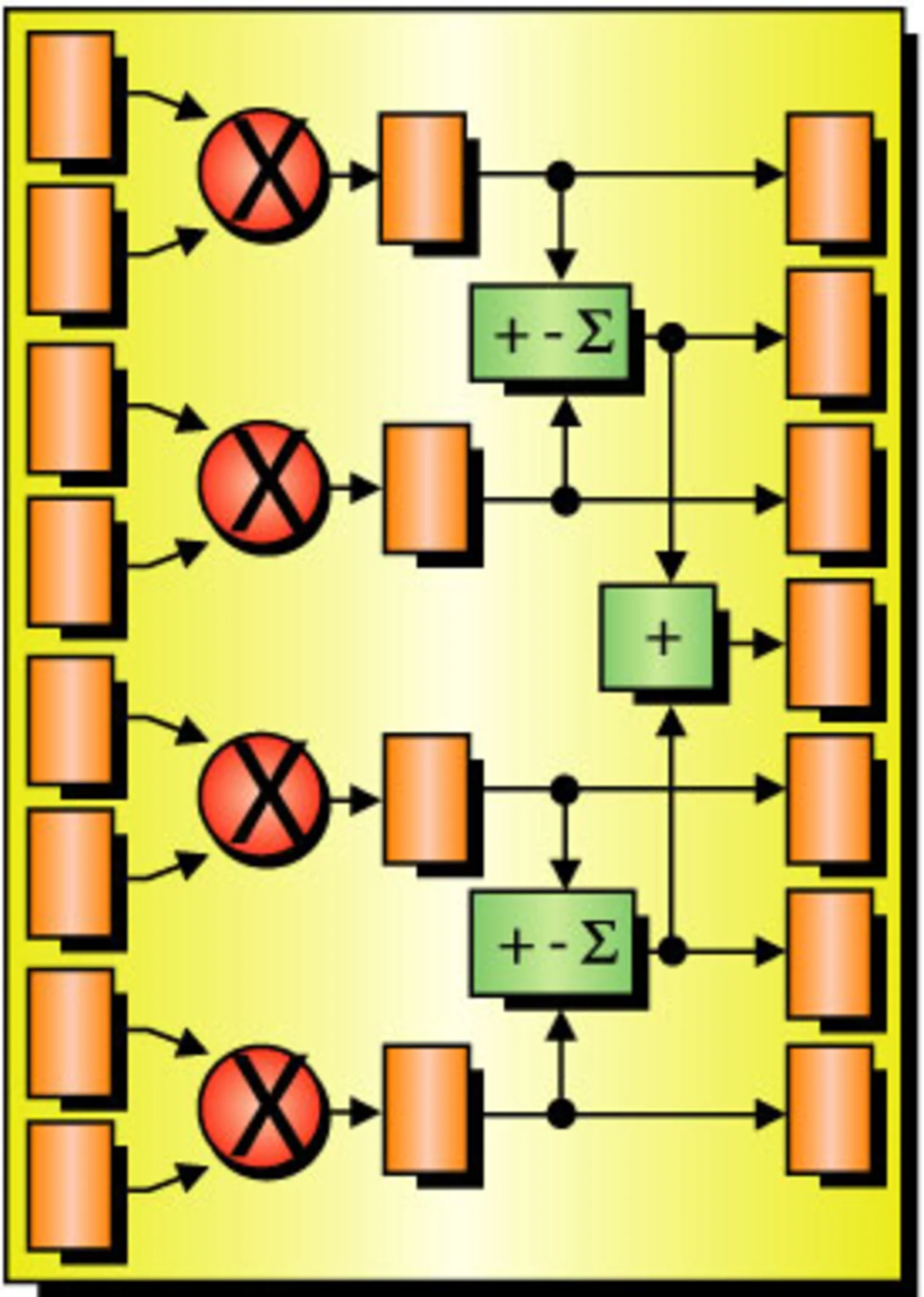

Möchte man in FPGAs Filter-Funktionen wie IIR, FFT, FIR oder andere Applikationen mit hohem arithmetischen Anteil realisieren, stehen bei der ECP-Familie (Economy Plus) spezielle DSP-Blöcke zur Verfügung.

Ein DSP-Block kann als 36x36-bit-Multiplizierer mit Eingangs-, Ausgangs- und Pipeline-Register konfiguriert werden. Eine weitere Option ist eine 18x18-bit-Multiplizierer-Variante mit Eingangs-, Ausgangs- und Pipeline-Register, wobei zusätzlich Addierer/Subtrahierer und Summationsfunktionen zur Verfügung stehen. In dieser Konfiguration bietet ein sysDSP-Block vier dieser Multiplizierer mit ihren oben aufgeführten Zusatzfunktionen (Bild 3). Ebenso lassen sich die Blöcke auch als 9x9-bit-Multiplizierer konfigurieren, wobei davon dann acht zur Verfügung stehen. In anderen Low-Cost-FPGAs finden sich oftmals keine DSP-Blöcke oder bestenfalls nur Multiplizierer mit Ausgangsregistern. Alle weiteren Funktionen müssen aufwendig in FPGA-Logik realisiert werden.

So ist zum Beispiel bei einer Realisierung eines IIR-Filters vierter Ordnung mit 18 bit Auflösung die Geschwindigkeit um 70 % höher und die Auslastung der programmierbaren Logik um den Faktor 4 geringer als bei anderen Low-Cost-FPGAs, die lediglich Multiplizierer bieten. Ein Vergleich zu Low-Cost-FPGAs ohne spezielle arithmetische Logik würde noch gravierender ausfallen.

Mit Hilfe der sysDSP-Blöcke ist es beispielsweise möglich, FFT-Routinen mit 1024 Punkten mit über 200 MHz laufen zu lassen. Dieser FFT-Core ist in der Bibliothek der ECP-Familie enthalten. Da diese Bausteine für sehr schnelle Designs optimiert sind, ist es wichtig, dass sie eine hohe Sperrschichttemperatur (Junction temperature) aushalten und eine mit 90-nm-FPGAs vergleichbare Verlustleistung aufweisen. Die zulässige Sperrschichttemperatur der EC/ECP-FPGAs liegt bei 125 °C, ein Wert, der bei heutigen 90-nm-Low-Cost-FPGAs nicht denkbar ist.

FPGA-Konfiguration

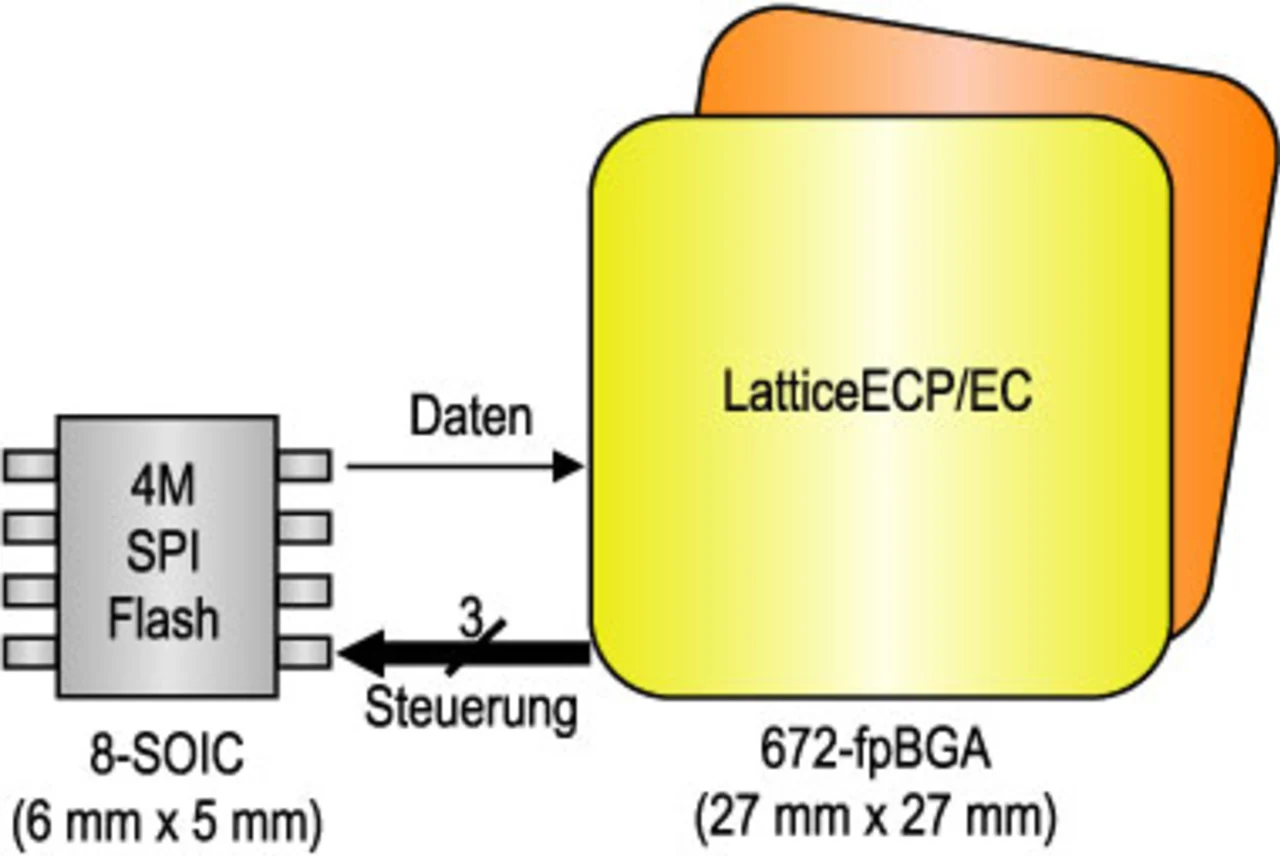

Bei den EC/ECP-FPGAs handelt es sich um SRAM basierende FPGAs, welche beim Einschalten geladen werden müssen. Dies kann entweder über einen Mikroprozessor, eine serielle oder parallele Schnittstelle oder über einen externen Boot-Baustein erfolgen. Damit die Kosten möglichst niedrig bleiben, lassen sich die EC/ECP-FPGAs direkt an SPI3- beziehungsweise SPI-Flash-Bausteine anschließen (Bild 4). Diese SPI-Flash-Speicher benötigen nur wenig Platinenfläche und sind kompatibel von 512 Kbit bis 32 Mbit. Typischerweise lassen sich diese Bausteine mit 20 MHz takten, was eine Ladezeit von ca. 265 ms bei einem 20-K-LUT-Baustein bedeutet. Nimmt man einen SPI-Flash-Speicher mit 40 MHz, wird diese Zeit entsprechend halbiert.

Die Konfigurations-Schnittstelle lässt sich im FPGA auf Taktfrequenzen von maximal 130 MHz einstellen. Müssen kürzere Ladezeiten erreicht werden, kann auch die parallele Schnittstelle benutzt werden. Diese Schnittstelle lässt sich in den verschiedenen I/O-Standards konfigurieren und ist nicht wie bei anderen Low-Cost-FPGAs auf LVCMOS mit 2,5 V beschränkt.

Ein Nachteil der SPI-Flash-Bausteine ist, dass sie sich nicht über JTAG programmieren lassen. Deshalb bietet Lattice einen kleinen IP-Core an, mit dem man über den JTAG-Port des FPGA den SPI-Flash-Speicher programmieren kann.

LatticeEC/ECP-Familie im Überblick

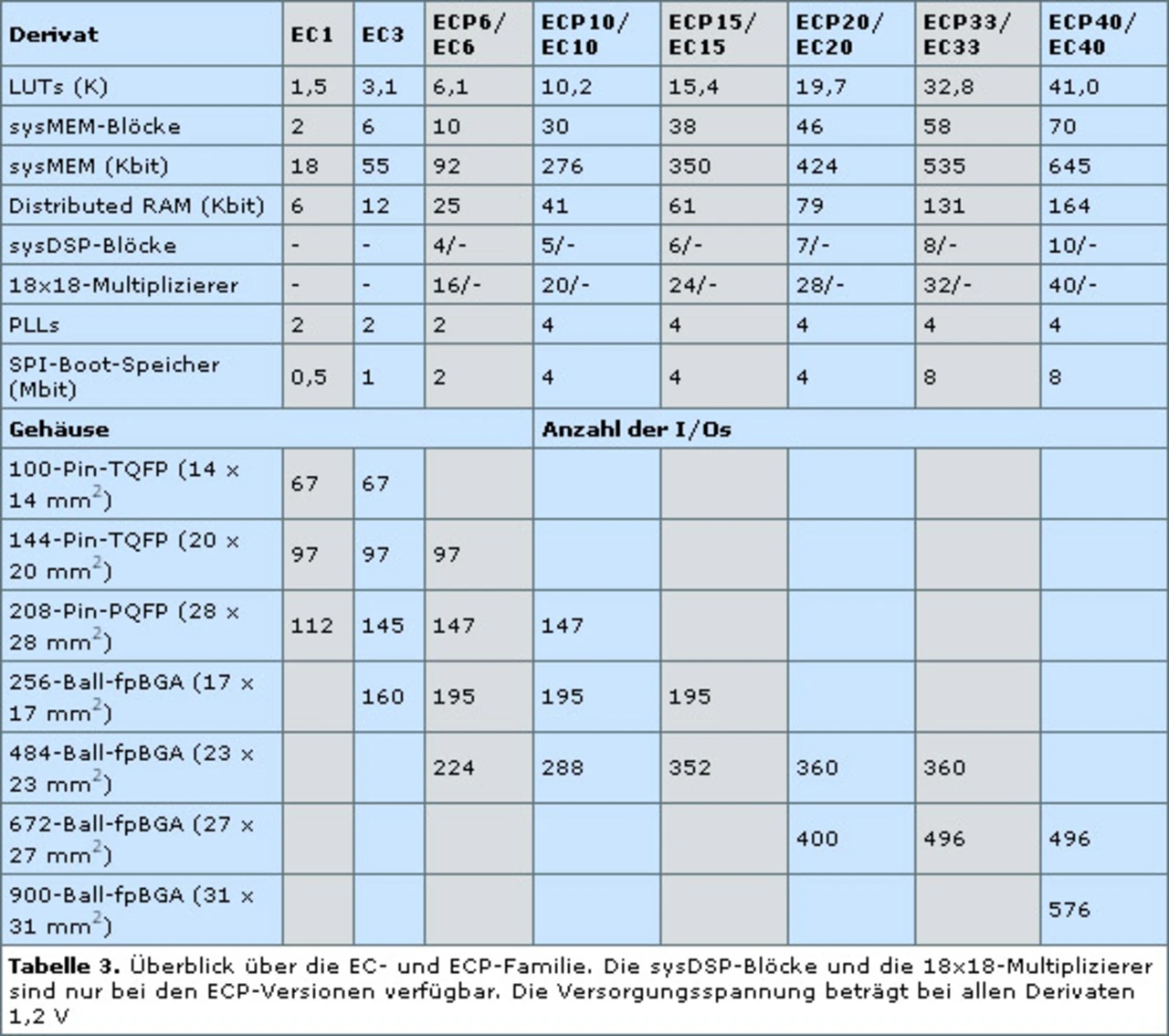

Die EC-Familie reicht von 1,5 K LUTs bis hoch auf 41 K LUTs (Tabelle 3). Die ECP-Familie startet bei 6 K LUTs und geht ebenfalls hoch bis auf 41 K LUTs. Die Bausteine EC20 und ECP20 sind bereits in Massenproduktion. Von allen anderen (bis EC/ECP33) gibt es Muster, wobei Stückzahlen bis Ende der ersten Quartals 2005 erwartet werden.

| Dipl.-Ing. (FH) Harald Werner studierte Elektrotechnik an der FH Koblenz mit Schwerpunkt Nachrichtentechnik. 1987 startete er bei Siemens als Verfahrensbetreuer der Mikroelektronik und arbeitete auf dem Gebiet der Boardlevel/System-Simulation. 1993 wechselte er zum CAE-Anbieter Viewlogic als FAE und 1996 zu Actel. Seit 2000 ist er beim PLD-Anbieter Lattice Semiconductor als Technischer Leiter zuständig für Zentral-Europa. E-Mail: Harald.Werner@latticesemi.com |

Verwandte Artikel:

- Die Schotten-FPGAs

- DDR-Speicherschnittstelle

- Interne Speicherstruktur