11-Gbit/s-Transceiver ermöglichen neue Anwendungen

Fortsetzung des Artikels von Teil 1

11-Gbit/s-Transceiver ermöglichen neue Anwendungen

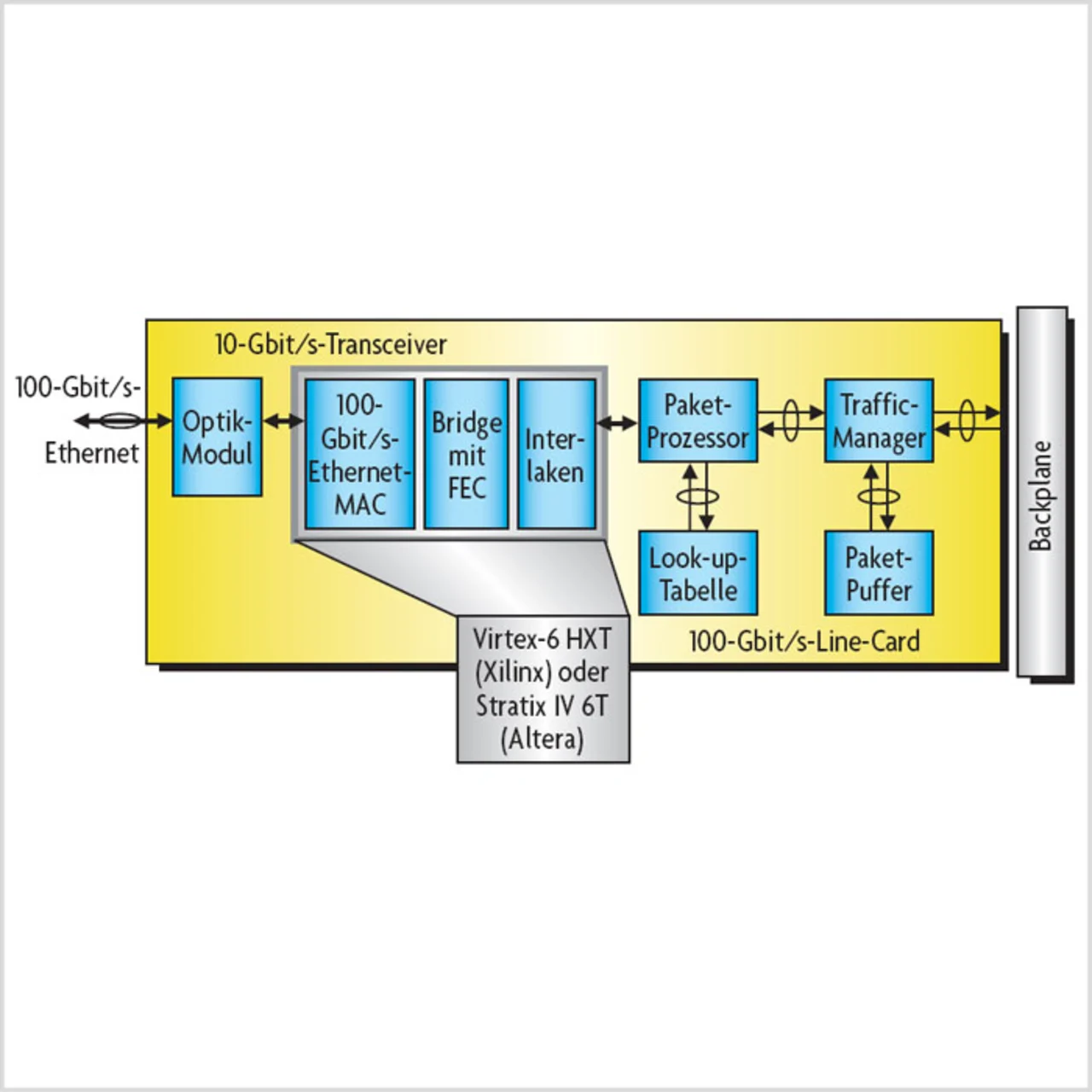

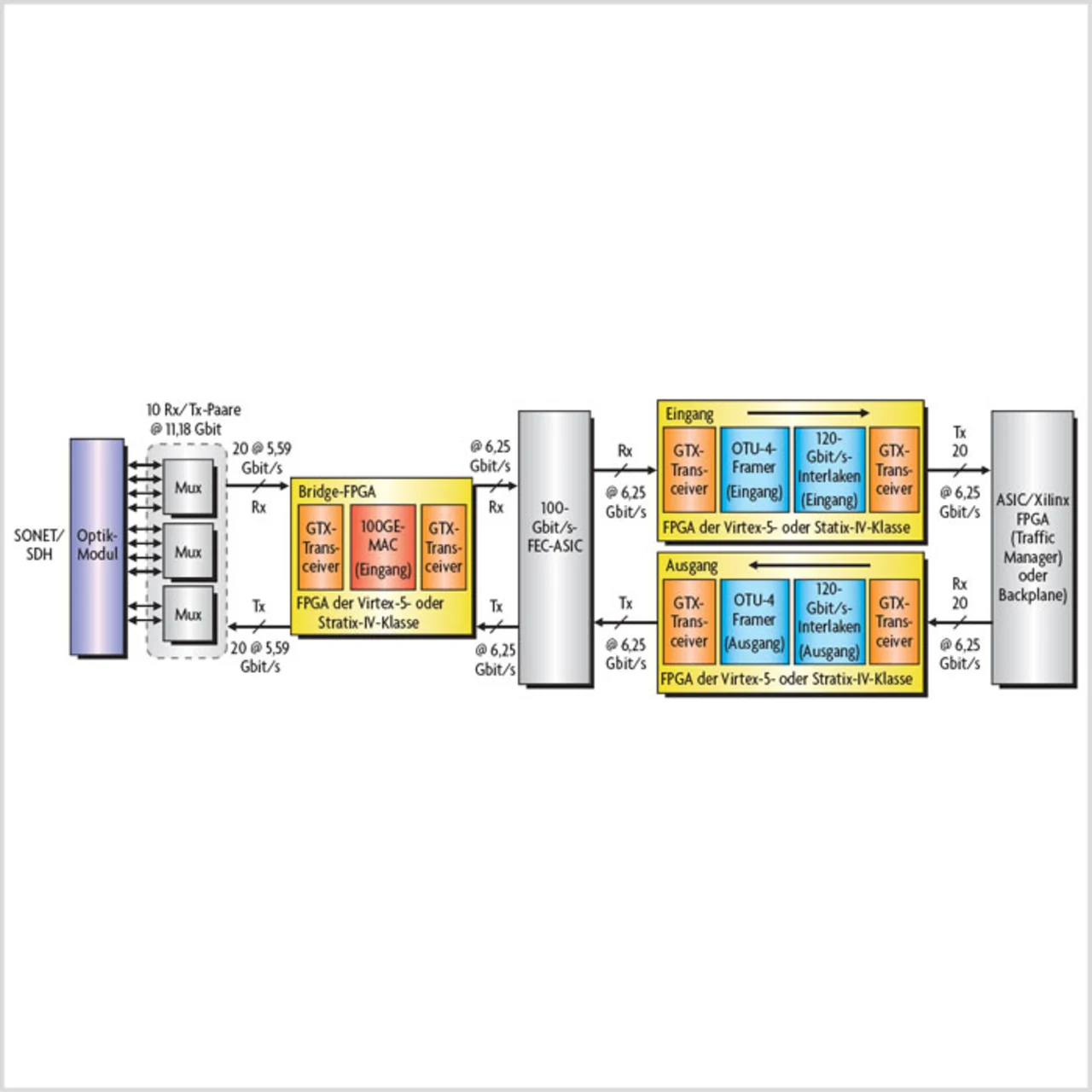

Bild 1 zeigt die Blockschaltung einer 100-Gbit/s-Line-Card. Die Design-Anforderungen umfassen unter anderem bis zu elf 10,3125-Gbit/s-Transceiver (CAUI/ XLAUI zum optischen Modul) und bis zu 24 6,25-Gbit/s-Transceiver (Interlaken zu Backplane), des weiteren müssen DDR3, QDRII oder RLDRAM II mit 533 MHz getaktet werden können. Mit Stratix IV GT oder Virtex-6 HTX lassen sich, wie in Bild 1 gezeigt, Ethernet-MAC, FEC (Foreward Error Correction) und Interlaken in einem einzigen FPGA unterbringen. Bild 2 zeigt das Blockschaltung eines Optik-Routers für Netzwerke, wie er in zahlreichen Rechenzentren im Einsatz ist. Ein Problem besteht u.a. darin, dass bei einer Veränderung des EFEC-Algorithmus (Enhanced Foreward Error Correction) das zugehörige ASIC neu designt werden muss. Des weiteren besteht die grundsätzliche Anforderung, die Kosten durch Verringerung der Komponenten zu reduzieren und die Bandbreite bei gleichbleibender Leistungsaufnahme zu erhöhen.

Jobangebote+ passend zum Thema

Da es im 0402- und 0603-Format Dünnfilm-Sicherungen mit geeigneten Schmelzeigenschaften und ESR-Werten gibt, wurde ein für diese Formate geeigneter Leadframe konstruiert (Bild 2). Letzteres ist für bis zu zwei Sicherungs-Konfigurationen geeignet und erlaubt die Verwendung automatischer Bestückungsmaschinen zum Platzieren und Befestigen der Sicherung. Je nach Anwendung kommen verschiedenene Befestigungsmethoden in Frage – z.B. leitendes Epoxidmaterial, Hochtemperatur-Lot usw.

Nach erfolgter Kapselung und vor Beendigung der Fertigung wird die mittlere Bypass-Verbindung entfernt (Bild 3), damit der Strom von der Leiterplatte über den externen Leadframe durch die Sicherung zum Tantal-Kondensator fließen kann. Die Bypass-Verbindung für die Sicherung kann übrigens wahlweise vor oder nach dem Einbrenn- und Stoßstromtest usw. entfernt werden. Diese Entscheidung sollte je nach den Anforderungen der Applikation und der Schaltung vor der Produktion getroffen werden.

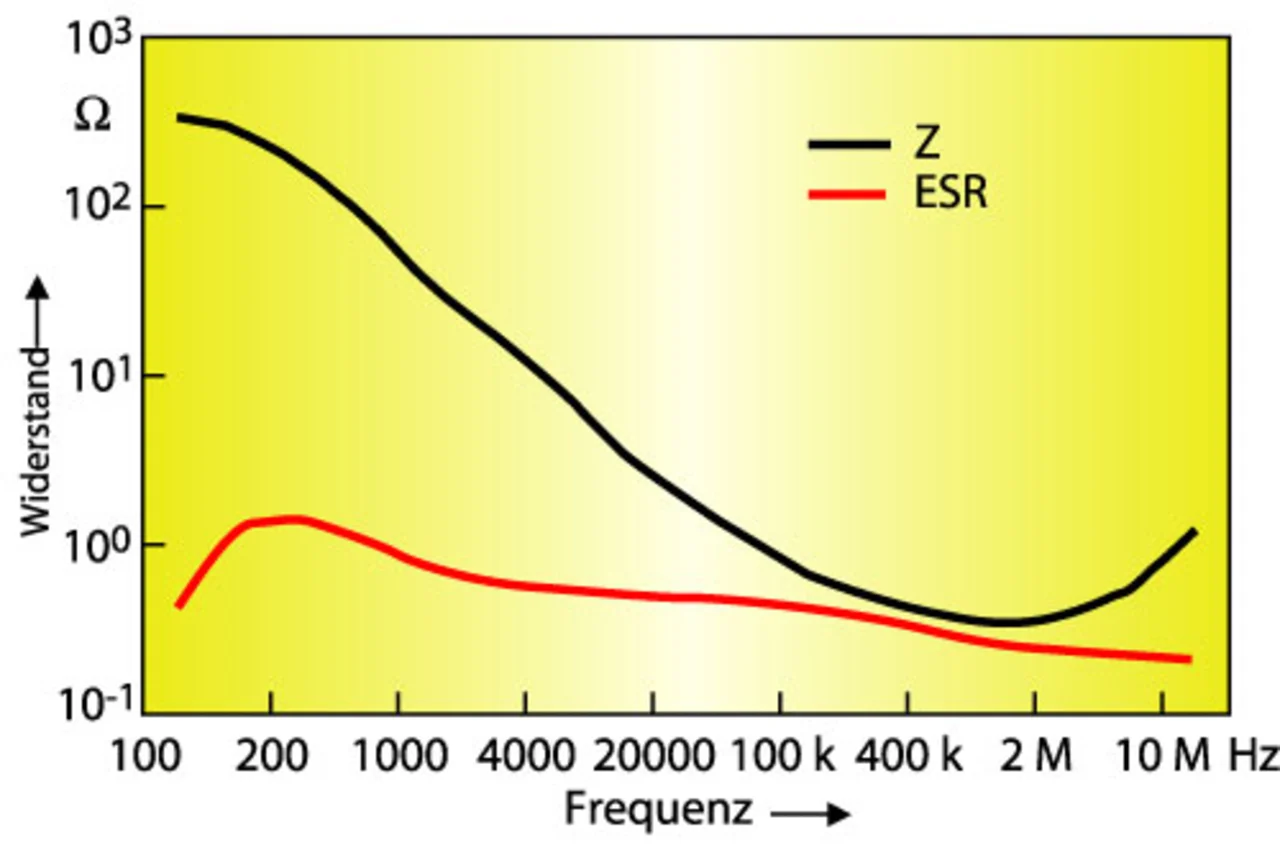

Die elektrischen Parameter eines mit Sicherung versehenen Kondensatormoduls sind recht einfach. Die ESR-Werte von Kondensator und Sicherung sind bekannt und müssen, da es sich um eine Serienschaltung handelt, schlicht addiert werden. Die folgenden Diagramme geben die Frequenzabhängigkeit von Impedanz und ESR für zwei Kondensatoren mit eingebauter Sicherung wieder. Bild 4 zeigt den Frequenzgang für eine Konfiguration mit einer Sicherung bei einem D-Case-Baustein mit 6,8 µF/35 V, Bild 5 den Frequenzgang für eine Konfiguration mit einer Sicherung und ein D-Case-Produkt mit 4,7 µF/50 V. Die ESR-Kurve bricht bei etwas über 400 kHz ab, während die Impedanz oberhalb dieser Frequenz steil zunimmt. Die Ursache hierfür ist der bei höheren Frequenzen zu Tage tretende induktive Blindwiderstand.

Um die möglichen Design-Optionen auszuloten, wurde ein Modul mit zwei Sicherungen hergestellt, die parallelgeschaltet sind (Bild 6). In Frage kommt diese Konfiguration beispielsweise, wenn ein D-Case-Baustein mit 4,7 µF/50 V oberhalb von 400 kHz eingesetzt werden soll. Das Sys-tem mit zwei Sicherungen weist bis 10 MHz einen flachen Frequenzgang auf. Obwohl sich der Ansprechstrom durch die Parallelschaltung im Prinzip verdoppelt, wird der Kondensator wegen der kurzen Ansprechzeit der Sicherungen nach wie vor wirksam geschützt.

nach Unterlagen der AVX Tantalum Corp

Alfred Goldbacher, Elektronik

Literatur

[1] ‑Reynolds, Ch.: Reliability Management of Tantalum Capacitors. AVX Tantalum Corp.

[2] ‑Gouvernelle, D.: Surface Mount Tantalum Capacitor with Built-In Fuse. CARTS-Europe ’89, October 1989, Amsterdam.

[3] ‑Fuse Terminology, User Guide. Bel Fuse Inc., Jersey City.

[4] ‑Chamberlain, M.: Tyco Fuse Selection Guide. Tyco Electronics, Menlo Park.

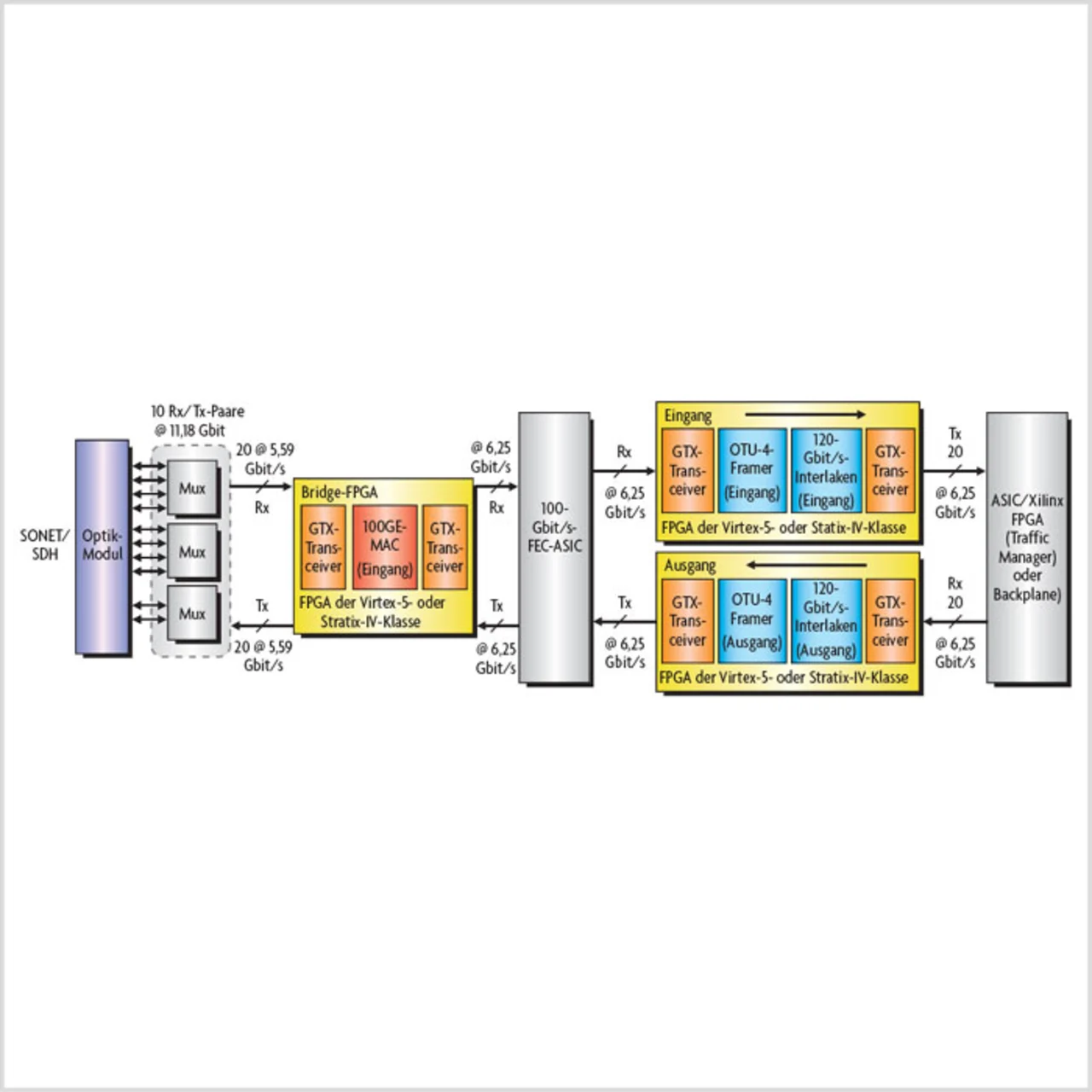

Mit Hilfe der neu vorgestellten FPGAs lässt sich das Design deutlich vereinfachen (Bild 3): Fehlerkorrektur, OTU-4-Framing und 100G-Ethernet-MAC können in zwei FPGAs (eines für jede Datenrichtung) zusammengefasst werden, wodurch sich die Leistungsaufnahme um mehr als ein Drittel reduzieren lässt und die Systemkosten um geschätzte 10 bis 20 Prozent sinken. Entwickler können teure ASICs ersetzen und dabei die Flexibilität ihrer eigenen Algorithmen verbessern, um die Reichweite der optischen Übertragung ohne Repeater zu vergrößern.

Gleichzeitig mit den neuen High-End-FPGAs stellten Xilinx mit dem Spartan-6 und Altera mit dem Arria-II zwei neue Familien mit kosten- und verbrauchsoptimierten Bausteinen vor, die auf Konsumelektronik (beispielsweise LC-Displays) oder Car-Infotainment-Anwendungen zielen.

Weitere Informationen über die einzelnen Mitglieder der neuen FPGA-Familien finden sich unter www.xilinx.com beziehungsweisewww.altera.com. fr

Siehe auch:

FPGAs: Arria II GX, ECP-3 und Spartan-6 LXT im Vergleich

Datenraten bis zu 8,5 Gbit/s

Die bei der nachstehend beschriebenen Kondensatorserie eingesetzten Sicherungen basieren auf einer Dünnfilm-Technologie. Die elektrischen und physikalischen Eigenschaften des Bauteils lassen sich mit Hilfe dieser Technologie auf eine Weise steuern, die mit konventionellen Sicherungs-Technologien nicht möglich ist. Die Bausteine sind eigentlich als Schutz für moderne, per Oberflächenmontage bestückte Leiterplatten vorgesehen.

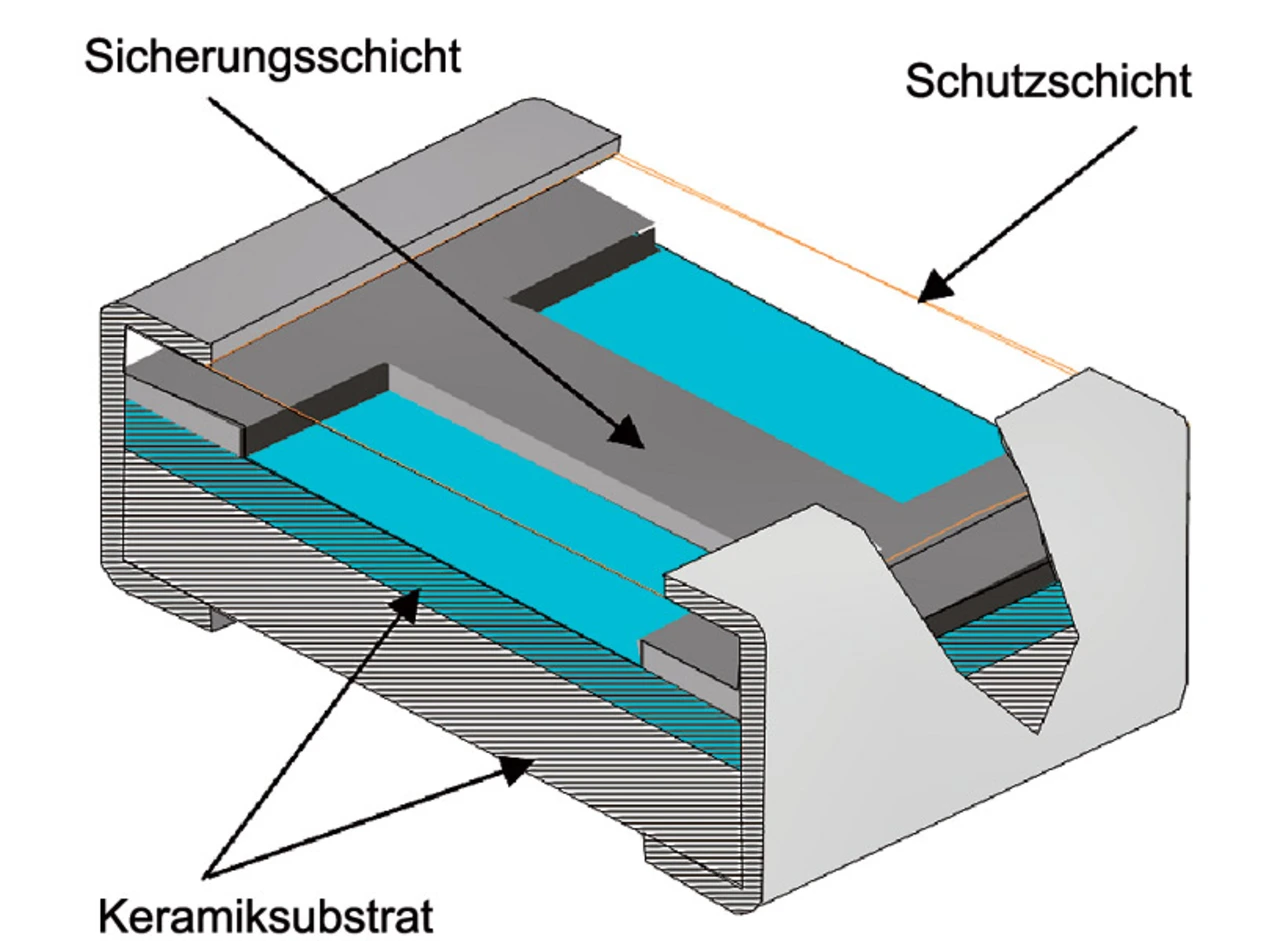

Die Dünnfilm-Sicherung wird in der Regel auf einem Aluminiumoxid-Substrat angeordnet (Bild 1) und bietet in Größe und Profil erhebliche Vorteile gegenüber herkömmlichen Sicherungs-Technologien. Das Ultraminiatur-Chipgehäuse erlaubt eine problemlose Oberflächenmontage mit automatischen Bestückungsmaschinen, und dank der verwendeten Dünnfilm-Technologie lassen sich die Parameter der Sicherung präzise und reproduzierbar definieren. Ansprechzeiten von weniger als 100 µs sind möglich. Eingelötete Sicherungen bieten zudem einen sicheren Schutz vor Überstrom-Situationen, ohne mit dem Risiko des unerwarteten Wiedereinschaltens bei selbstrückstellenden Sicherungselementen behaftet zu sein.

- 11-Gbit/s-Transceiver ermöglichen neue Anwendungen

- 11-Gbit/s-Transceiver ermöglichen neue Anwendungen

- Auswahl einer Sicherung